一、前言

在过去的几年中,计算机处理器取得了相当大的进步,晶体管的尺寸每年都在变小,而且这种进步达到了摩尔定律迅速变得多余的地步。

当涉及到处理器时,不仅晶体管和频率很重要,高速缓存也很重要。

在讨论 CPU(Central Processing Units)时,您可能听说过高速缓存。但是,我们并没有过多地关注这些数字,它们也不是这些 CPU 广告的主要亮点。

那么,CPU 缓存到底有多重要,它又是如何工作的?

二、什么是 CPU 缓存?

首先,缓存只是一种非常快速的内存类型。您可能知道,计算机内部有多种内存类型。有一个主存储(如硬盘或 SSD),用于存储大量数据(操作系统和所有程序)。

接下来,我们有随机存取存储器,通常称为 RAM。这比主存储要快得多。

最后,CPU 自身具有更快的存储单元,我们称之为缓存。

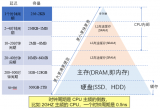

计算机的内存具有基于速度的层次结构,而缓存位于该层次结构的顶部,是最快的。它也是最靠近中央处理的地方,它是 CPU 本身的一部分。

高速缓存是静态 RAM(SRAM),而系统 RAM 是动态 RAM(DRAM)。静态 RAM 是一种可以保存数据但是不要用一直刷新的存储器,与 DRAM 不同,SRAM 更加适合用于高速缓存。

三、CPU 缓存如何工作?

我们已经知道,程序被设计为一组指令,最终由 CPU 运行。

当我们运行程序的时候,这些指令必须从主存储器取指令到 CPU。这是内存层次结构起作用的地方。

数据首先被加载到 RAM 中,然后被发送到 CPU。因为 CPU 每秒都能够执行大量指令。为了充分利用其功能,CPU 需要访问超高速内存,这是缓存的来源。

内存控制器执行从 RAM 中获取数据并将其发送到缓存的工作。根据系统中使用的 CPU,此控制器可以位于主板的北桥芯片组上,也可以位于 CPU 本身内部。

然后,高速缓存在 CPU 内执行数据的来回传输。内存的层次结构也存在于缓存中。

四、缓存级别:L1,L2 和 L3

CPU 缓存分为三个主要的**“级别”**,即 L1,L2 和 L3。这里的层次结构是根据缓存速度来划分的。

L1(1 级)高速缓存是计算机系统中存在的最快的内存。就访问优先级而言,L1 缓存具有 CPU 在完成特定任务时最可能需要的数据。

就其大小而言,L1 高速缓存通常最多可达 256KB。但是,一些真正功能强大的 CPU 现在将其占用近 1MB。现在,某些服务器芯片组(如 Intel 的高端 Xeon CPU)具有 1-2MB 的一级缓存。

L1 缓存通常也分为两种方式,分为指令缓存和数据缓存。指令高速缓存处理有关 CPU 必须执行的操作的信息,而数据高速缓存则保留要在其上执行操作的数据。

L2(2 级)缓存比 L1 缓存慢,但大小更大。它的大小通常在 256KB 到 8MB 之间,尽管更新,功能强大的 CPU 往往会超过此大小。L2 高速缓存保存下一步可能由 CPU 访问的数据。在大多数现代 CPU 中,L1 和 L2 高速缓存位于 CPU 内核本身,每个内核都有自己的高速缓存。

L3(3 级)高速缓存是最大的高速缓存存储单元,也是最慢的一个。它的范围从 4MB 到 50MB 以上。现代 CPU 在 CPU 裸片上具有用于 L3 高速缓存的专用空间,并且占用了很大一部分空间。

五、缓存命中或未命中以及延迟

数据会从 RAM 依次流到 L3 高速缓存,然后是 L2,最后是 L1。

当处理器正在寻找要执行操作的数据时,它首先尝试在 L1 高速缓存中找到它。如果 CPU 能够找到它,则该情况称为高速缓存命中。然后,它继续在 L2 和 L3 中找到它。

如果找不到数据,它将尝试从主内存访问数据。这称为高速缓存未命中。

现在,众所周知,高速缓存旨在加快主内存和 CPU 之间的数据传输。

从内存访问数据所需的时间称为延迟,L1 具有最低的延迟,是最快的,并且最接近核心,而 L3 具有最高的延迟。缓存未命中时,延迟会增加很多。这是因为 CPU 必须从主存储器中获取数据。

随着计算机变得越来越快和越来越好,我们看到延迟减少了。现在,我们拥有低延迟的 DDR4 RAM,以及具有低访问时间的超高速 SSD 作为主要存储,这两项都大大降低了整体延迟。

以前,缓存设计曾经使 L2 和 L3 缓存位于 CPU 外部,这对延迟产生了负面影响。

然而,CPU 制造工艺的进步使得在比以前更小的空间中安装数十亿个晶体管。因此,为缓存留出了更多空间,这使缓存尽可能地靠近核心,从而大大减少了延迟。

六、缓存的未来

缓存设计一直在发展,尤其是随着内存变得更便宜,更快和更密集。英特尔和 AMD 在缓存设计方面进行了相当多的试验,英特尔甚至还在试验 L4 缓存。CPU 市场正在以前所未有的速度向前发展。

这样,我们必定会看到缓存设计跟上 CPU 不断增长的能力。

缓存设计方面进行了相当多的试验,英特尔甚至还在试验 L4 缓存。CPU 市场正在以前所未有的速度向前发展。

这样,我们必定会看到缓存设计跟上 CPU 不断增长的能力。

此外,还有很多工作可以减少现代计算机的瓶颈。减少内存延迟可能是其中最大的一部分。业界正在为相同的解决方案而努力,并且未来看起来确实充满希望。

审核编辑黄宇

-

处理器

+关注

关注

68文章

19286浏览量

229873 -

cpu

+关注

关注

68文章

10863浏览量

211800 -

RAM

+关注

关注

8文章

1368浏览量

114707 -

内存

+关注

关注

8文章

3025浏览量

74061

发布评论请先 登录

相关推荐

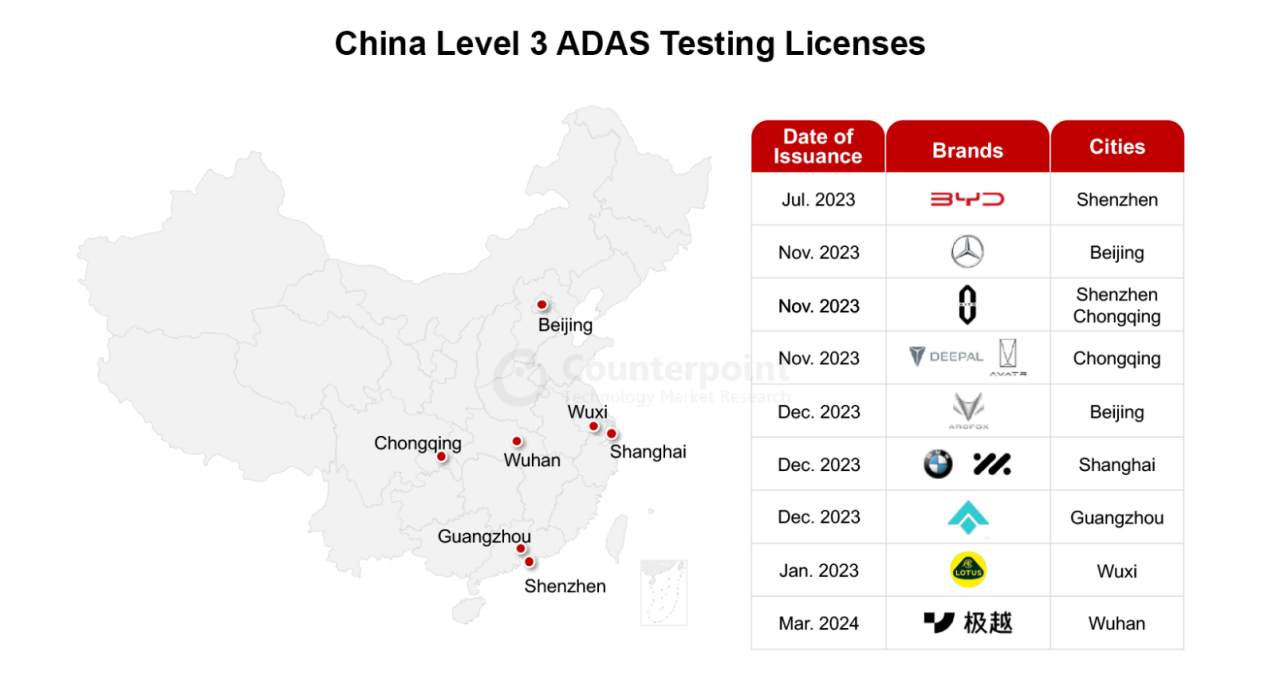

宝马成为首家获L2+与L3智驾系统组合认证车企

华为智能汽车解决方案BU CEO靳玉志畅谈L3级智能驾驶及规划

BK1661 全集成的单芯片 L1 频段 GNSS 解决方案

BK1662 单芯片L1/L5双频GNSS解决方案

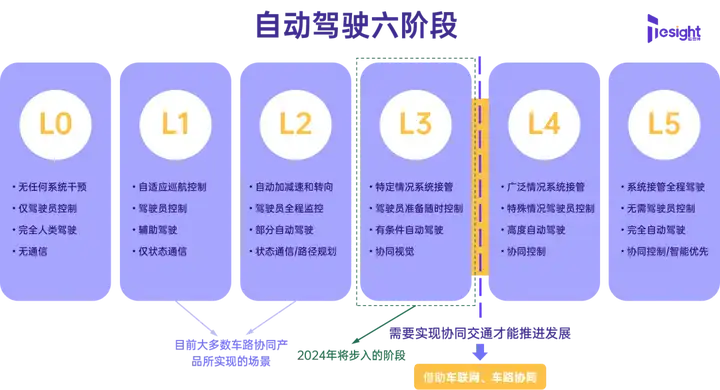

驶向L3级自动驾驶:车路协同

中性线的作用如何?三相四线制供电线路的注意事项?

全球L3自动驾驶汽车销量将破25000辆,中国市场潜力巨大

一文详解步进电机和伺服电机接线区别

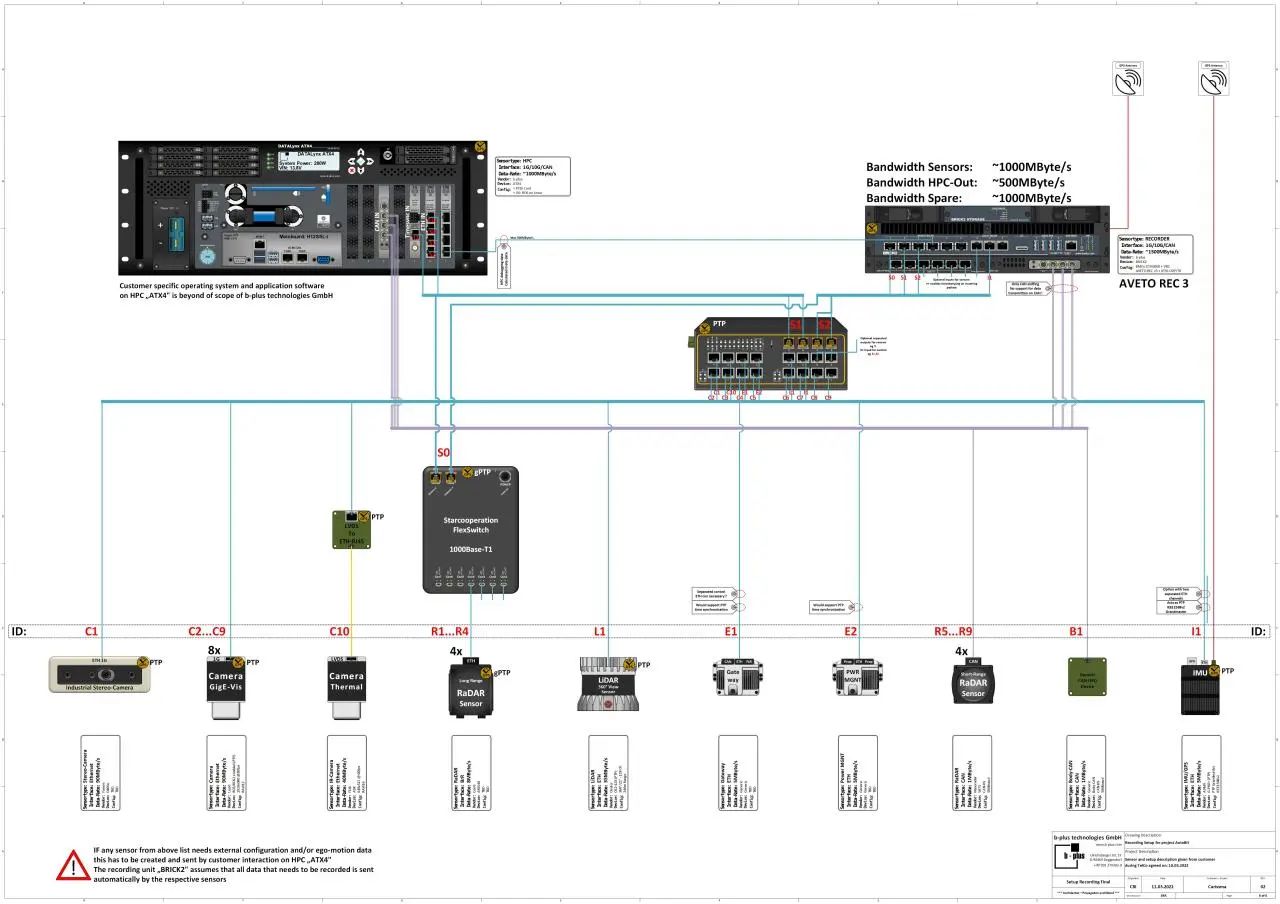

康谋方案 | L2进阶L3,数据采集如何助力自动驾驶

缓存大小对CPU性能的影响解析

一文带你了解CPU缓存L1,L2,L3的工作原理

一文带你了解CPU缓存L1,L2,L3的工作原理

评论