碳化硅(SiC)MOSFET的快速开关速度,高额定电压和低RDSon使其对于不断寻求在提高效率和功率密度的同时保持系统简单性的电源设计人员具有很高的吸引力。

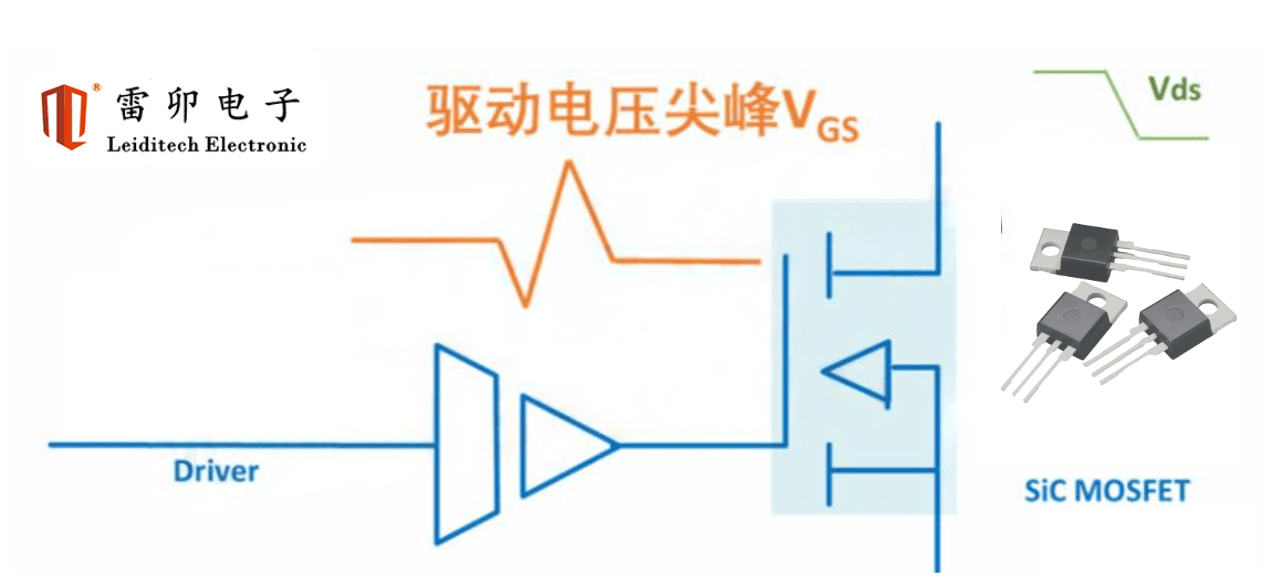

但是,由于它们的快速开关速度会产生高振铃持续时间的高漏源电压(VDS)尖峰,因此会引入EMI,尤其是在高电流水平下。

了解VDS尖峰和振铃

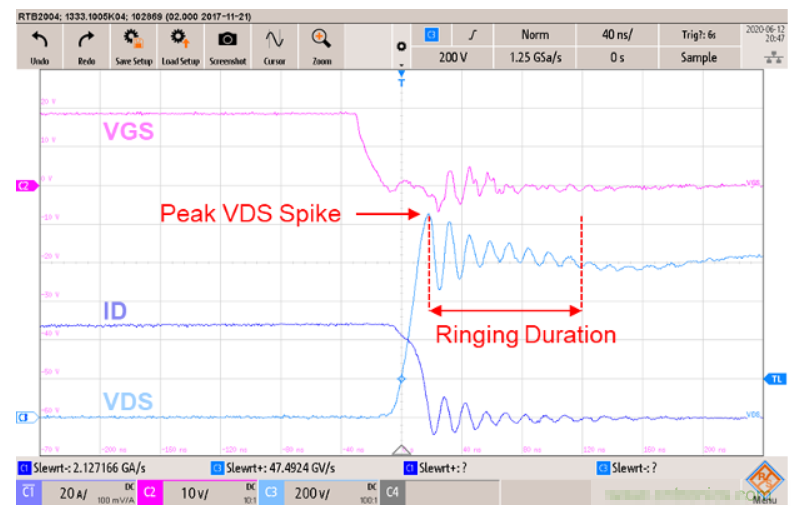

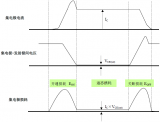

寄生电感是SiC MOSFET VDS尖峰和振铃的主要原因。查看关断波形(图1),栅极-源极电压(VGS)为18V至0V。关断的漏极电流为50A,VDS为800V。SiC MOSFET的快速开关速度会导致高VDS尖峰和较长的振铃时间。这种尖峰会降低设备的设计裕量,以应对闪电条件或负载的突然变化,并且较长的振铃时间会引入EMI。在高电流水平下,此事件更加明显。

图1 VDS尖峰和关断时通过SiC MOSFET产生的振铃(1200V 40mOhm)

常见的EMI去除威廉希尔官方网站

抑制EMI的常规方法是降低通过器件的电流速率(dI / dt),这是通过使用高栅极电阻(RG)来实现的。但是,较高的RG会显着增加开关损耗,从而损失效率。

抑制EMI的另一种方法是降低电源环路的杂散电感。但是,要实现这一点,PCB的布局需要更小的电感。但是,最大程度地减小电源环路是有限的,并且必须遵守最小间距和间隙安全规定。使用较小的封装也会影响热性能。

滤波器设计可用于帮助满足EMI要求并减轻系统权衡。控制威廉希尔官方网站 (例如,频率抖动)还可以降低电源的EMI噪声。

使用RC缓冲器

使用简单的RC缓冲器是一种更有效的方法。它可控制VDS尖峰并以更高的效率和可忽略的关闭延迟来缩短振铃时间。借助更快的dv/dt和额外的电容器,缓冲电路具有更高的位移电流,从而降低了关断过渡时的ID和VDS重叠。

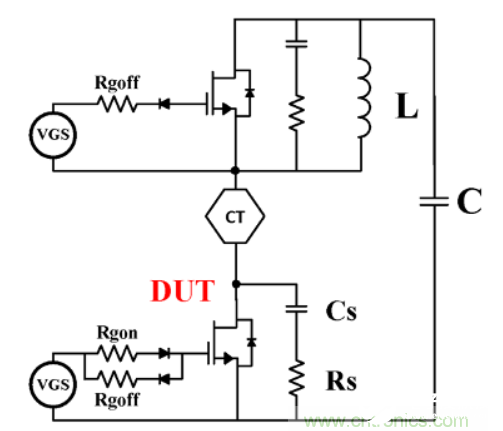

双脉冲测试(DPT)证明了RC缓冲器的有效性。它是带有感性负载的半桥。桥的高边和低边都使用相同的器件,在低边测量了VGS,VDS和ID(图2)。电流互感器(CT)同时测量设备和缓冲电流。因此,测得的总开关损耗包括器件损耗和缓冲损耗。

图2.半桥配置(顶部和底部使用相同的设备)

RC缓冲器只是一个200pF电容器和一个10Ω电阻器,串联在SiC MOSFET的漏极和源极之间。

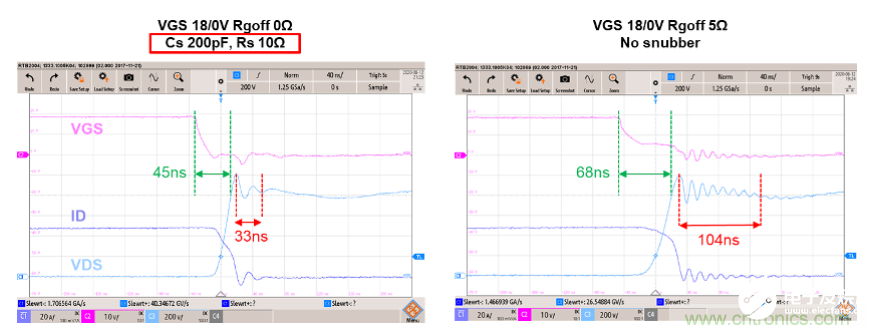

图3:RC缓冲器(左)比高RG(右)更有效地控制关断EMI

在图3中,比较了图1中相同设备的关闭状态。左波形使用具有低RG(关)的RC缓冲器,而右波形具有高RG(关)且无缓冲器。两种方法都限制了关断峰值尖峰漏极——源极电压VDS。但是,通过将振铃时间减少到仅33ns,缓冲电路更加有效,并且延迟时间也更短。

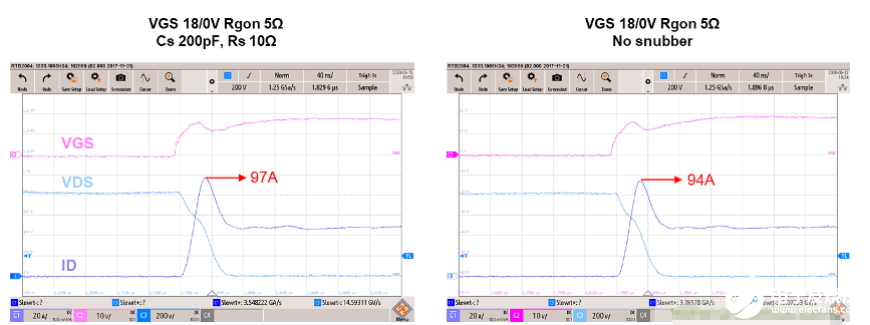

图4.比较显示,使用RC缓冲器在开启时影响很小

图4比较了带有RC缓冲器(左)和不带有RC缓冲器的5ΩRG(开)下的波形。 RC缓冲器的导通波形具有稍高的反向恢复峰值电流(Irr),但没有其他明显的差异。

RC缓冲器比高RG(关)更有效地控制VDS尖峰和振铃持续时间,但这会影响效率吗?

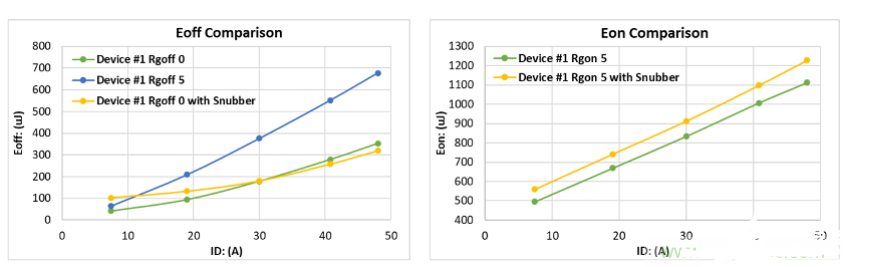

图5.缓冲器和高RG(off)之间的开关损耗(Eoff,Eon)比较

在48A时,高RG(关)的关断开关损耗是低RG(关)的缓冲器的两倍多,几乎与不使用缓冲器的开关损耗相当。因此,可以得出这样的结论:缓冲器效率更高,可以更快地切换和控制VDS尖峰并更有效地振铃。从导通开关损耗来看,缓冲器只会稍微增加Eon。

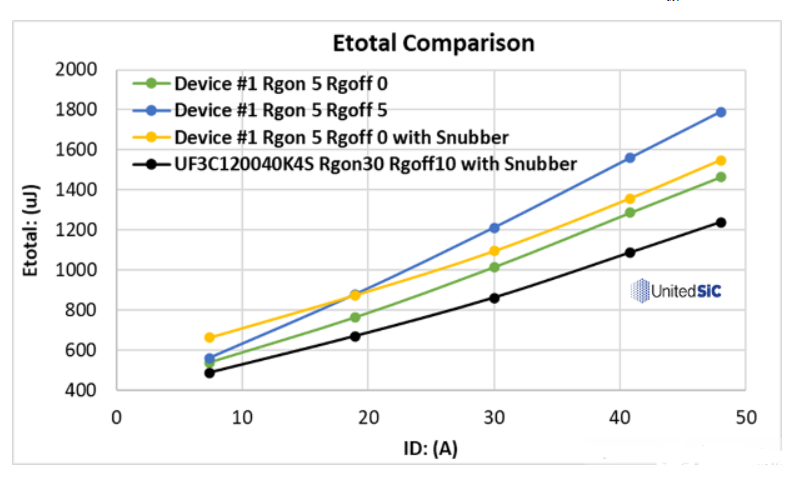

图6.缓冲器与高RG(关闭)的总开关损耗(Etotal)的比较

为了更好地理解整体效率,将Eoff和Eon一起添加了Etotal(图6)。全速切换时,缓冲器在18A以上时效率更高。对于以40A / 40kHz开关的40mΩ器件,使用RC缓冲器的高和低RG(关)之间的损耗差为11W。总之,与使用高RG(关)相比,缓冲器是一种将EMI和开关损耗降至最低的更简单,更有效的方法。

随着第四代SiC器件进入市场,这种简单的解决方案将继续使工程师进行设计以获得最佳效率。

编辑:hfy

-

MOSFET

+关注

关注

147文章

7158浏览量

213163 -

emi

+关注

关注

53文章

3587浏览量

127614 -

缓冲器

+关注

关注

6文章

1922浏览量

45473 -

sic器件

+关注

关注

1文章

56浏览量

15531

发布评论请先 登录

相关推荐

SiC MOSFET模块封装威廉希尔官方网站 及驱动设计

影响MOSFET开关损耗的因素

SiC MOSFET和SiC SBD的区别

差分探头在测量开关损耗中的应用

一文读懂MOSFET开关损耗介绍

如何使用示波器测量电源开关损耗

如何更好地驱动SiC MOSFET器件?

水下航行器电机的SiC MOSFET逆变器设计

反激CCM模式的开通损耗和关断损耗详解

SiC MOSFET的EMI和开关损耗解决方案解析

SiC MOSFET的EMI和开关损耗解决方案解析

评论