设备或组件可以保持在可接受的范围内,则功能,性能和生命周期都会增加。如果设备或组件要保持在可接受的范围内,则必须首先了解这些限制是什么。举个例子,我的一位同事无法理解为什么他与电容器串联的保险丝反复失效。

经进一步审查,罪魁祸首是建议保险丝的安培数(裕度)贴错标签。事实证明,该板显示20安培,但建议的安培数为40安培。他通过研究原理图发现了这一发现。利润和对它们的遵守在功能,性能和耐用性中起着至关重要的作用。这包括CMOS反相器中的噪声容限。

噪声裕度和CMOS特性

在电气工程领域,可以代数地将无噪声的最坏情况下的输入电平代数加到不引起输出电压偏离允许的逻辑电压电平的外部信号的最大电压幅度称为噪声裕度。在通信系统工程领域,我们通常以分贝(dB)为单位测量噪声容限。

此外,我们将噪声容限定义为信号超过最小可接受量的比率。关于数字电路,噪声容限是信号超过产生“ 1”或“ 0”所需的阈值的量。

CMOS代表互补金属氧化物半导体。其制造过程包括使用互补且对称的p型和n型MOSFET对来实现逻辑功能。该威廉希尔官方网站 正用于IC(集成电路)芯片,微控制器,CMOS BIOS,微处理器,存储芯片和其他数字逻辑电路的构造中。

我们还可以发现CMOS威廉希尔官方网站 在诸如数据转换器,RF电路,高度集成的收发器(通信)和图像传感器等interwetten与威廉的赔率体系 电路中的使用。总体而言,CMOS器件的两个基本特征是低静态功耗和高抗噪性。

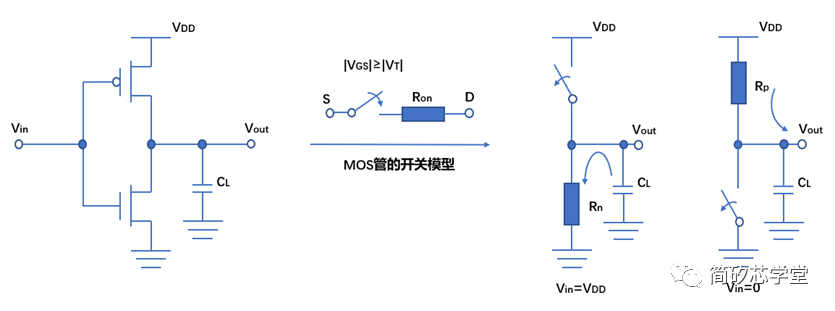

由于一对MOSFET始终处于关断状态,因此串联组合仅在开关状态(开和关)时瞬间消耗大量功率。结果,CMOS器件产生的热量通常比其他形式的逻辑(例如TTL)产生的热量少,即使它不改变状态,该逻辑通常也具有恒定电流。

CMOS反相器的特性

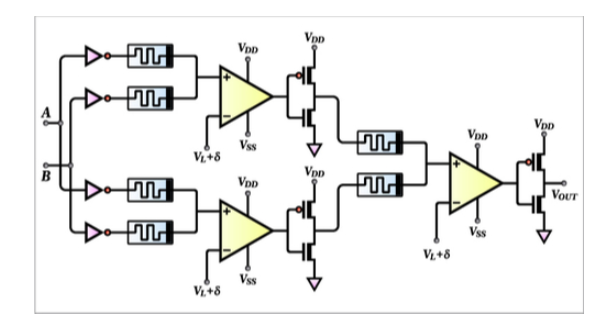

CMOS威廉希尔官方网站 轻松集成到芯片逻辑和VLSI芯片中。此外,它们以较高的速度运行,同时保持极少的功率损耗特性。此外,CMOS反相器提供了出色的逻辑缓冲功能,因为它的高和低噪声容限同等重要。

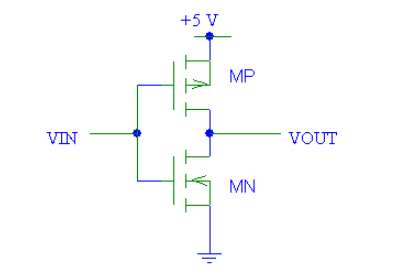

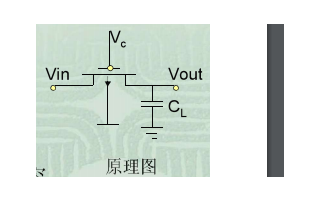

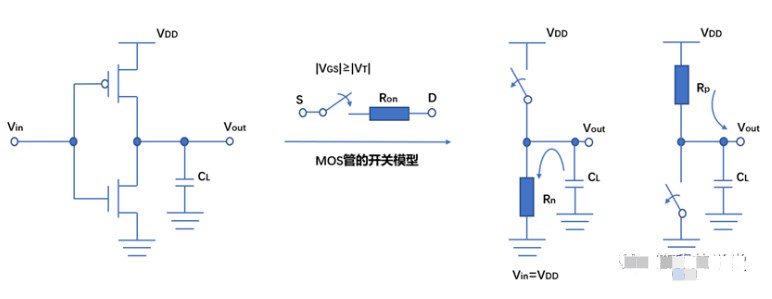

现在,让我们仔细看一下CMOS反相器的工作原理及其特性。首先,CMOS反相器包含连接到漏极和栅极端子的PMOS(p型)和NMOS(n型)晶体管。而且,它在PMOS源极端子上包含电源电压(VDD),并在NMOS源极端子上包含接地。最后,它具有到栅极端子的VIN连接和到漏极端子的VOUT连接。请记住,CMOS反相器在其设计中没有使用电阻,因此与标准电阻MOSFET反相器相比,它具有更高的功率效率。

参考上面的CMOS反相器图,由于CMOS器件输入端的电压在5伏和0伏之间变化,因此PMOS和NMOS的状态将相应地不同。因此,如果将每个晶体管建模为一个由VIN激活的简单开关,那么毫无疑问,我们可以看到CMOS反相器的功能。

CMOS反相器中的噪声裕度

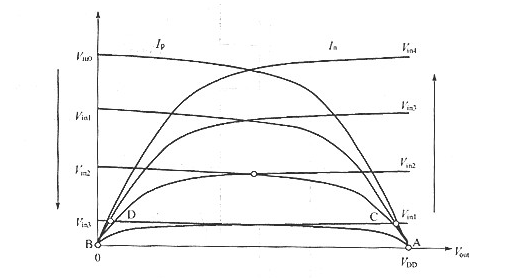

现在,对于纯数字反相器,由于存在一定程度的电容,它们不会立即从“ 1”(逻辑高)切换到“ 0”(逻辑低)。当逆变器从逻辑高电平过渡到逻辑低电平时,会有一个不清楚的区域,在该区域中我们无法考虑电压是低还是高。正是在这一时刻,我们认为这是我们的噪声余量。

我们必须考虑两个噪声容限,它们分别是:高噪声容限(NMH)和低噪声容限(NML)。逻辑高电平的驱动设备的最小电压输出(VOH min)必须大于逻辑高电平的接收设备的最小电压输入(VIH min)。由于导线上存在噪声,因此驱动设备输出端的逻辑高信号可能会以较低电压到达接收设备的输入端。

因此,逻辑高电平的噪声容限NMH =(VOH min – VIH min)是您仍然可以正确接收逻辑高电平信号的容差范围。对于噪声容限,我们可以说相同,对于逻辑低电平,NML =(VIL max – VOL max),这规定了线路上逻辑低电平信号的容限范围。噪声容限越小,表明电路对噪声越敏感。

噪声容限是设计容限的标准,可以在特定条件下建立适当的电路功能。噪声源可以包括电源,运行环境,电场和磁场以及辐射波。片上晶体管的开关活动也会产生不希望的噪声。因此,为了在特定的噪声条件下提供适当的晶体管开关,电路的设计必须包括这些特定的噪声容限。

编辑:hfy

-

CMOS

+关注

关注

58文章

5710浏览量

235427 -

MOSFET

+关注

关注

147文章

7158浏览量

213164 -

反相器

+关注

关注

6文章

311浏览量

43294 -

图像传感器

+关注

关注

68文章

1897浏览量

129529 -

VLSI

+关注

关注

0文章

73浏览量

42913

发布评论请先 登录

相关推荐

LTC4313的典型应用具有高噪声容限的2线总线缓冲器

抖频要要有效降低开关电源EMI噪声容限的威廉希尔官方网站

噪音容限,噪音容限是什么意思

MOS反相器和CMOS反相器的详细资料说明

浅谈CMOS反相器中的噪声容限

浅谈CMOS反相器中的噪声容限

评论