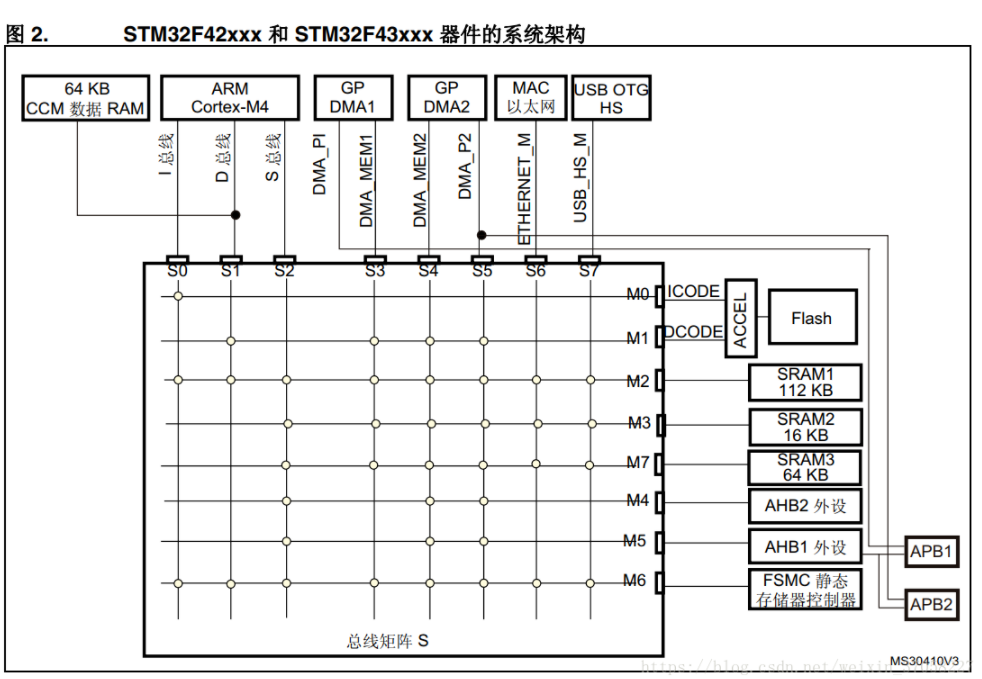

1. 存储器和总线架构

1.1 系统架构

I总线:

此总线用于将 Cortex™-M4F 内核的指令总线连接到总线矩阵。内核通过此总线获取指令。

此总线访问的对象是包含代码的存储器(内部 Flash/SRAM 或通过 FSMC 的外部存储器)。

D总线:

此总线用于将 Cortex™-M4F 数据总线和 64 KB CCM 数据 RAM 连接到总线矩阵。内核通过此总线进行立即数加载和调试访问。此总线访问的对象是包含代码或数据的存储器(内部Flash 或通过 FSMC 的外部存储器)

注意:

CCM(Core Coupled Memory)是给F4内核专用的全速64KB RAM, 它们没有经过总线矩阵, F4内核与之直接相连, 地址空间在0x1000_0000 ~ 0x1000_FFFF。可以用作堆栈以及高速运算的数据缓存。

参考应用:CCM中移植FreeRTOS

s:总线:

此总线用于将 Cortex™-M4F 内核的系统总线连接到总线矩阵。此总线用于访问位于外设或 SRAM 中的数据。也可通过此总线获取指令(效率低于 ICode)。此总线访问的对象是112 KB、 64 KB 和 16 KB 的内部 SRAM、包括 APB 外设在内的 AHB1 外设、 AHB2 外设以及通过 FSMC 的外部存储器

S3,S4:DMA存储器总线

此总线用于将 DMA 存储器总线主接口连接到总线矩阵。 DMA 通过此总线来执行存储器数据的传入和传出。此总线访问的对象是数据存储器:内部 SRAM( 112 KB、 64 KB、 16 KB)以及通过 FSMC 的外部存储器。

S5:DMA外设总线:

此总线用于将 DMA 外设主总线接口连接到总线矩阵。 DMA 通过此总线访问 AHB 外设或执行存储器间的数据传输。此总线访问的对象是 AHB 和 APB 外设以及数据存储器:内部SRAM 以及通过 FSMC 的外部存储器。

S6:以太网 DMA 总线

此总线用于将以太网 DMA 主接口连接到总线矩阵。以太网 DMA 通过此总线向存储器存取数据。此总线访问的对象是数据存储器:内部 SRAM( 112 KB、 64 KB 和 16 KB)以及通过FSMC 的外部存储器。

S7: USB OTG HS DMA 总线

此总线用于将 USB OTG HS DMA 主接口连接到总线矩阵。 USB OTG DMA 通过此总线向存储器加载/存储数据。此总线访问的对象是数据存储器:内部 SRAM(112 KB、 64 KB 和 16 KB)以及通过 FSMC 的外部存储器。

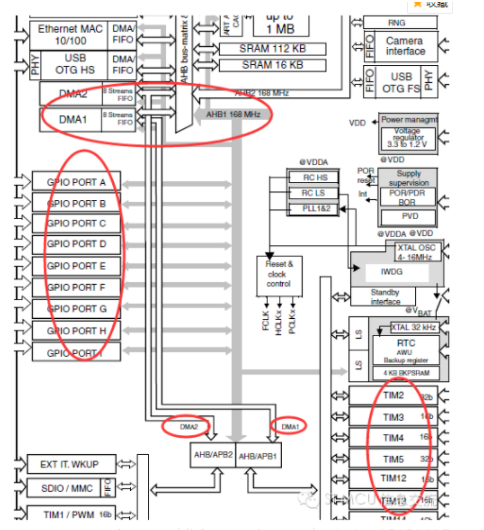

AHB、APB总线图:

结合以上两张图可见:GPIO由AHB1控制,DMA1可以访问TIM2、3、4、5、12、13;DMA2访问GPIO(因为在AHB1总线上)

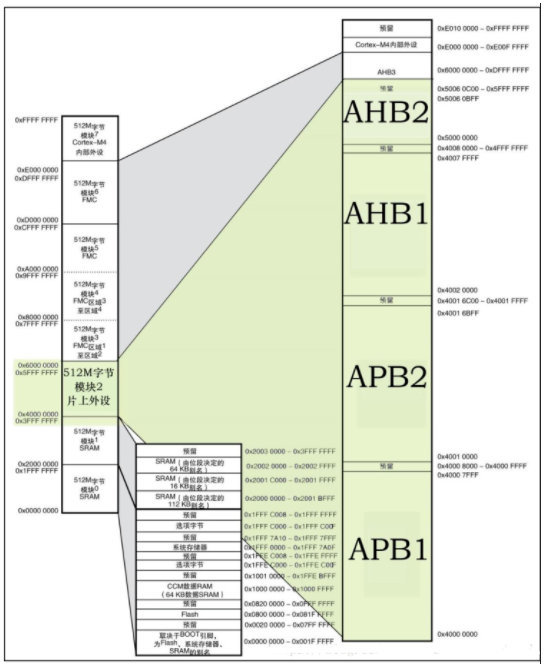

1.2.存储器映射

存储器本身不具有地址信息,它的地址是由芯片厂商或用户分配,给存储器分配地址的过程就称为存储器映射,具体见图 5-5。 如果给存储器再分配一个地址就叫存储器重映射

模块0:FLASH、CCM等

模块1:SRAM1、SRAM2、SRAM3(根据图1,以太网和AHB总线能访问SRAM1\2\3,并且支持并发访问,即CPU读写SRAM1时,以太网可读写SRAM2)

外设地址APB1、APB2、AHB1可以详细查找 stm32F4xx中文参考手册

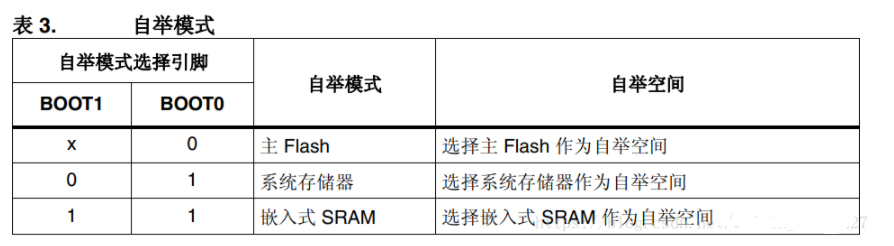

1.3、自举配置

嵌入式自举程序模式用于通过以下串行接口重新编程 Flash:

● USART1(PA9/PA10)

● USART3( PB10/11 和 PC10/11)

● CAN2(PB5/13)

● USB OTG FS(PA11/12) 从设备模式( DFU:器件固件升级)。

编辑:hfy

-

FlaSh

+关注

关注

10文章

1633浏览量

147958 -

存储器

+关注

关注

38文章

7484浏览量

163776 -

总线

+关注

关注

10文章

2878浏览量

88056

发布评论请先 登录

相关推荐

FPGA与STM32通过FSMC总线通信的实验

存储器和总线架构分析:stm32F429-系统架构

存储器和总线架构分析:stm32F429-系统架构

评论