1. 背景

这篇文章主要介绍了DDR3IP核的写实现。

2. 写命令和数据总线介绍

DDR3 SDRAM控制器IP核主要预留了两组总线,一组可以直接绑定到DDR3 SDRAM芯片端口,一组是留给用户端使用的,框图如图1所示。

如图1 所示的中间部分为我们调取的IP 核,user FPGA Logic 为用户端逻辑,DDR2/DDR3 SDRAM 为存储芯片。其中IP 核与存储芯片之间的总线大部分以ddr 作为开头,这部分总线我们只需要在top 模板设为端口即可,无需我们控制。用户端与IP 核之间的总线大部分以app 作为开头,并且从用户端输出到IP 核的信号线需要我们产生。

在了解了大概的框架之后,下面我们首先通过以app 为开头的总线实现对IP写控制操作。为了更好的了解相关的参数,我们可以登录Xilinx 官网下载UG586手册,具体的下载地址如下所示: https://www.xilinx.com/support/documentation/ip_documentation/mig_7serie...

通过手册我们可以了解到,为了实现写,我们需要控制app 端的命令总线和数据总线,下面先对app 端命令总线作解释,此处的input 和output 均现对于IP核而言。

| 端口名称 | 端口名称 | 端口描述 |

| app_cmd | input | 3bit命令总线,3’b000代表写,3’b001代表读。 |

| app_addr | input | 30bit地址总线(位宽根据芯片不同会不同)。 |

| app_en | input | 1bit命令使能信号,该信号有效(高电平),且app_rdy也有效时,IP核才可以接收到用户端发送的app_cmd和app_addr。 |

| app_rdy | output | 1bit命令空闲信号,该信号有效(高电平),且app_en也有效时,IP核才可以接收到用户端发送的app_cmd和app_addr。 |

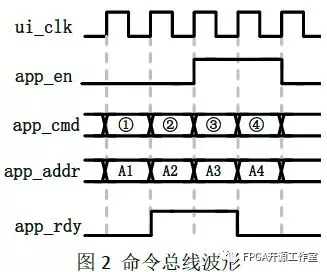

在了解到命令端每一个信号的作用后,我们可以给出下图2 所示的波形,其中①、②、④处的指令均不会被IP 核接收,只有③处的指令才会被IP 接收。

app 端写数据总线中的每一根信号作用如下表所示,此处的input 和output 均现对于IP 核而言。

| 端口名称 | 端口名称 | 端口描述 |

| app_wdf_data | input | 128bit写数据总线(位宽根据芯片不同会不同),该数据包含8个需要写入DDR3芯片的数据。 |

| app_wdf_wren | input | 1bit写数据有效标志,该信号有效(高电平),且app_wdf_rdy也有效时,IP核才可以接收到用户端发送的app_wdf_data。 |

| app_wdf_rdy | output | 1bit写数据空闲信号,该信号有效(高电平),且app_wdf_rdy也有效时,IP核才可以接收到用户端发送的app_wdf_data。 |

| app_wdf_end | input | 1bit最后一个写数据的标志,该信号有效(高电平)时,代表对应的app_wdf_data为当前写的最后一个数据。 |

| app_wdf_mask | input | 16bit写数据掩码(位宽根据芯片不同会不同),该信号为写数据的掩码。 |

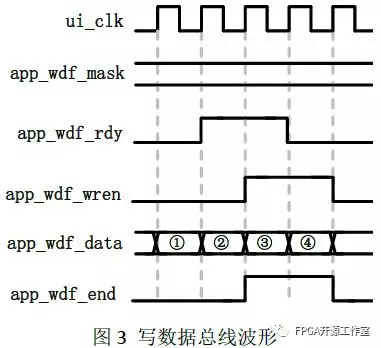

根据上表所描述,我们可以对app 端写时序所用到的每一根信号有一点的了解,下面给出写时序的波形。图3 中所示的①、②、④处的数据均不会被写入到IP 中,只有③处的数据才会被IP 接收。

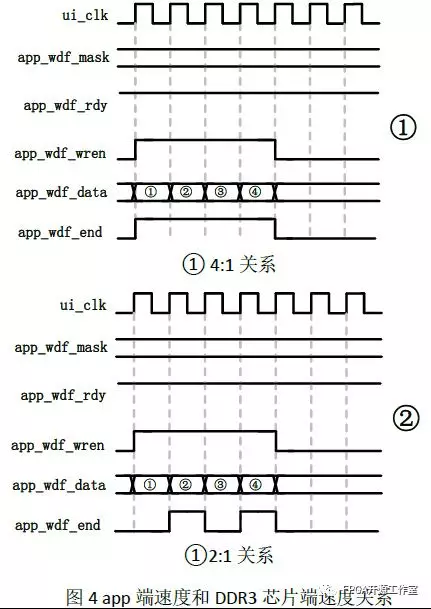

我们对app_wdf_end 这个信号做最进一步的讲解,该信号表示的是当前突发写的最后一个数据。在A7 DDR3 控制器IP 核中,只存在突发长度为8 这种形式,因此每一次的突发均为16bit x 8 = 128bit,并且在我们调取该IP 核时,会发现DDR3 的物理层端与用户端存在两种速率关系,即4:1 和2:1。当选取速率比例为4:1 时app_wdf_data 为128bit,此时每一个发送的有效app_wdf_data 数据均为当前8 突发的第一个数据,同时也是最后一个数据,因此此时app_wdf_end 信号 与app_wdf_wren 信号同步;当选取速率比例为2:1 时app_wdf_data 为64bit,此时每一个发送的有效app_wdf_data 数据均为当前突发的4 个数据,因此此时app_wdf_end 信号与app_wdf_wren 信号如下图②所示。

3. 写命令和写数据间关系讲解

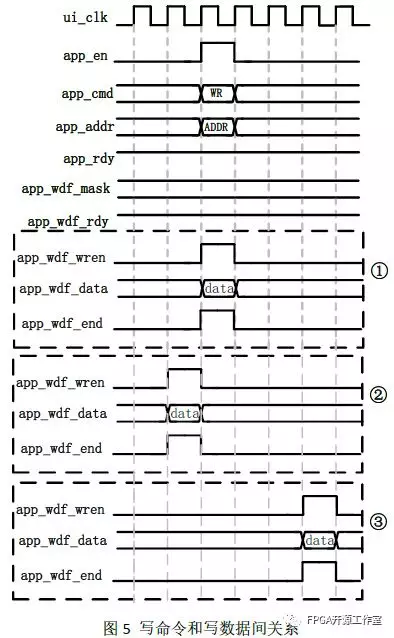

根据Xilinx UG586 手册我们可知,写命令和写数据直接存在三种逻辑关系,具体示例如图5 所示。图中①状态指的是命令和数据同时发送到IP 核,②状态指的是数据提前于命令发送到IP 核,③状态指的是命令提前于数据发送到IP 核。第①、②种情况均可稳定传输,但是第③种情况需要一个前提条件,即命令提前数据的时间不能超过两个用户端的时钟周期。因此,为了更稳定的发送数据,建议采取第①、②种发送模式,在本讲中,我们采取第②种发送方式。

编辑:hfy

-

FPGA

+关注

关注

1629文章

21729浏览量

603036 -

SDRAM

+关注

关注

7文章

423浏览量

55205 -

DDR3

+关注

关注

2文章

276浏览量

42246 -

Xilinx

+关注

关注

71文章

2167浏览量

121314 -

存储芯片

+关注

关注

11文章

896浏览量

43135

发布评论请先 登录

相关推荐

教程!FPGA DDR4读写实验(1)

DDR3、DDR4、DDR5的性能对比

DDR内存与SDRAM的区别 DDR4内存与DDR3内存哪个好

FPGA DDR4读写实验

DDR4 SDRAM控制器的主要特点

FPGA DDR4读写实验(1)

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 电源解决方案同步降压控制器数据表

完整DDR,DDR2,DDR3 和LPDDR3 存储器电源解决方案同步降压控制器数据表

具有同步降压控制器、2A LDO和缓冲基准的完整DDR2、DDR3和DDR3L存储器电源解决方案TPS51216-EP数据表

完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表

具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表

具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表

完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表

DDR3 SDRAM控制器IP核的写命令和写数据间关系讲解

DDR3 SDRAM控制器IP核的写命令和写数据间关系讲解

评论