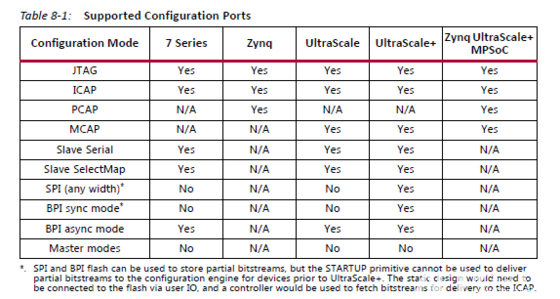

本博文主要是对基于PCIE(mcap)的部分可重构实现的步骤做一个简单的演示,如有错误之处,欢迎批评指正。值得说明的是,基于PCIE的部分可重构需在ultrascale系列及ultrascale+芯片才能实现,具体哪些系列能实现哪种配置方式如下图所示:

图1

本质上来说,无论是JTAG还是ICAP或者MCAP以及其它FPGA的配置方式,目的都是配置FPGA的逻辑。MCAP是通过PCIE来实现对FPGA的烧写,最终结果和使用JTAG进行FPGA烧写没有区别,而使用PCIE对FPGA烧写有更好的灵活性,在某些需求场合是必不可缺的,譬如在数据加速的部署,FPGA加速板卡是位于服务器端,在服务上线之后修改FPGA业务逻辑的话如果使用JTAG烧写,一方面操作十分不便,可行性极低,另一方面,重新烧写FPGA会导致原FPGA的PCIE设备从服务器中删除,需要重新启动服务器枚举设备(目前本人没有找到可以进入系统后重新枚举设备的方法),对于已经上线的服务器,在每次切换FPGA业务逻辑后重启服务器是无法接受的,因此,使用PCIE对FPGA的部分重配置就十分必要,部分重配置能够在保持FPGA静态逻辑(PCIE部分和其他非业务逻辑)正常工作的情况下动态修改某个区域的逻辑(业务逻辑)。使用这种威廉希尔官方网站 能够不重启服务器情况下快速切换业务逻辑。

本文的实现基于Xilinx的VCU1525加速板卡实现,VCU1525的FPGA是一颗ultrascale+的VU9P,由上图可以知道UltraScale+系列的FPGA支持MCAP配置模式。下面由一个简单的例程实现MCAP部分重配置。

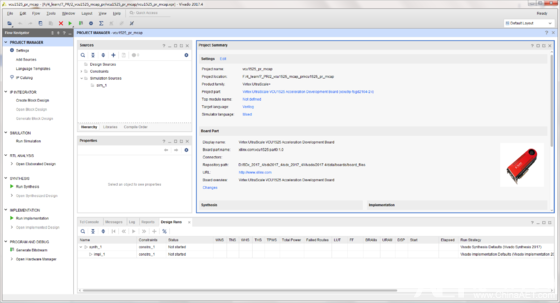

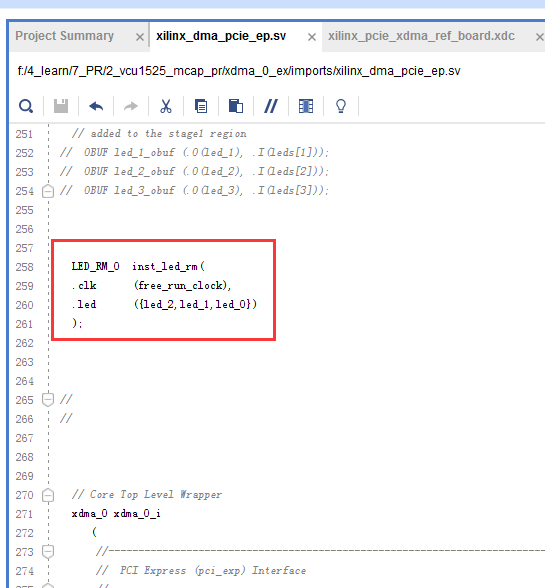

1.新建一个空白工程。

图2

2.因为使用MCAP的配置方式,而MCAP集成于PCIE硬核中,因此需要例化一个PCIE相关的IP,这里使用XDMA进行本次例程(裸PCIE硬核也可以),该例程没有XDMA进行数据DMA搬运的相关内容,仅仅是借用XDMA中的MCAP功能,本人目前也有一个比较痛苦的地方,就是XDMA的上位机驱动怎么和MCAP的驱动整合在一起,不懂上位机驱动开发表示很迷茫,有大佬懂这个可以探讨下。

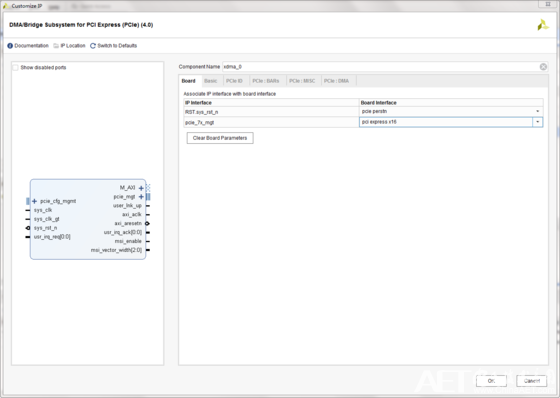

3.在Board选项中(在建立工程时选择Xilinx官方板卡才有这个选项)选择如下。

图3

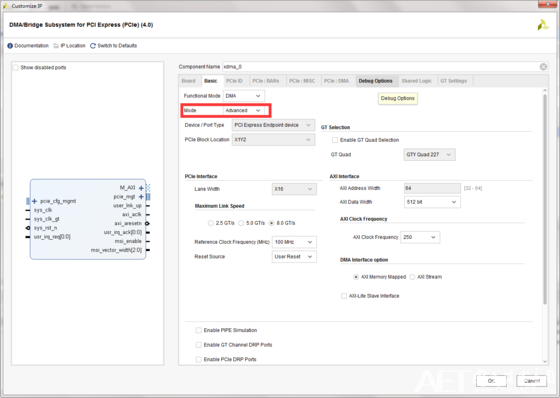

4.在Basic选项中,把图中红色框中的Mode设置成Advanced。

图4

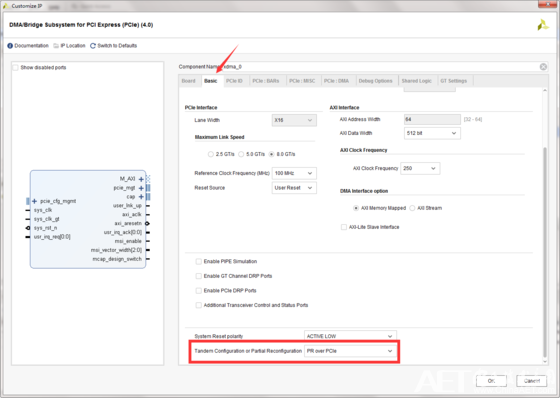

5.在Basic选项中,在最底部的Tandem Configuration or Partial Reconfiguration中选择PR over PCIE。

图5

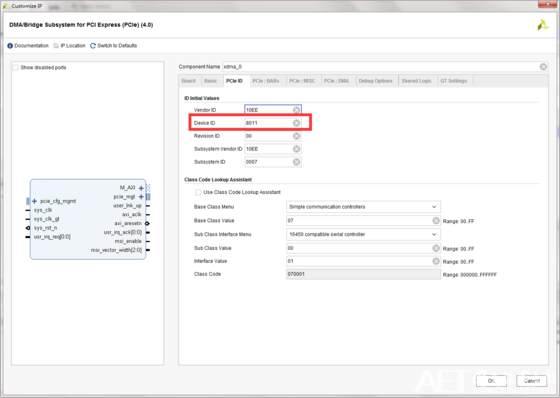

6.在Pcie ID选项的Device ID中设置成8011(因为Xilinx提供的驱动支持8011,8038,506F)

图6

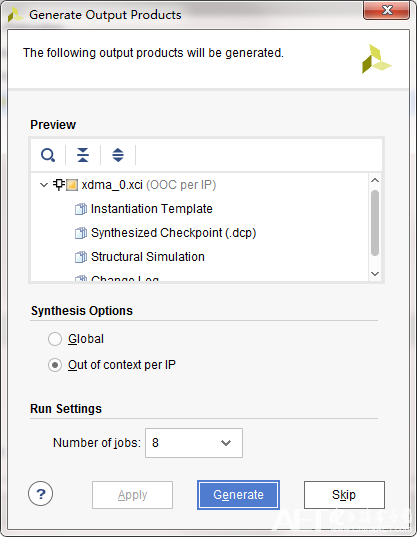

7.其它按照默认选项,生成该IP。

图7

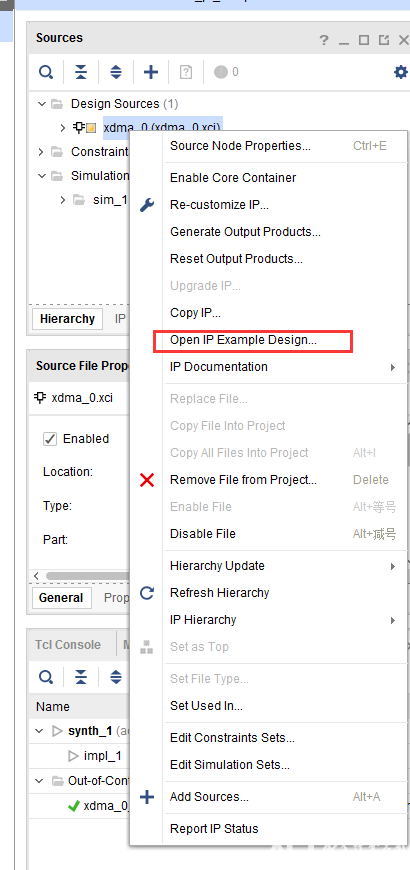

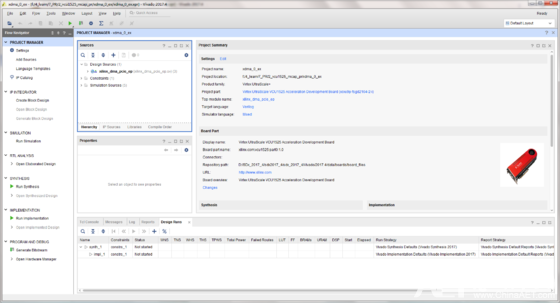

8.考虑到测试和实现的方便,使用XDMA的Example Design来修改例程,在XDMA综合完成之后(记得选择OOC),打开该IP的Example Design,在该工程上面做修改。

图8

9.Example Design如下图。

图9

10.首先我们先修改XDC文件和工程顶层,主要是LED的管脚和电平约束。在这个例子中,我们将要实现使用两个可重构模块,一个模块用于控制VCU1525的LED灯亮,一个模块用于控制VCU1525的LED灯灭,用这个简单的例子来说明PR的实现步骤。

11.修改工程中的时钟生成IP,此步骤不是必要,主要是指定输入时钟管脚,如果不是官方板子,在XDC里面约束即可。

图10

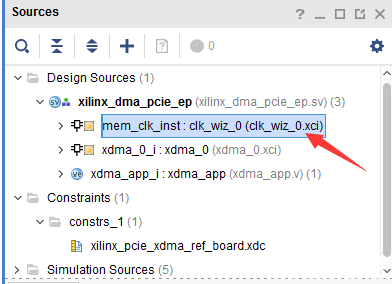

12.新建两个模块,分别是LED_RM_0和LED_RM_1。其中LED_RM_0用于控制LED灭,LED_RM_1用于控制LED亮。两个模块的逻辑很简单,只是做演示作用。代码逻辑如下。

图11

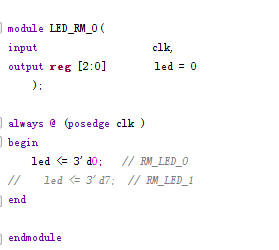

13.在工程顶层例化其中一个RM模块。

图12

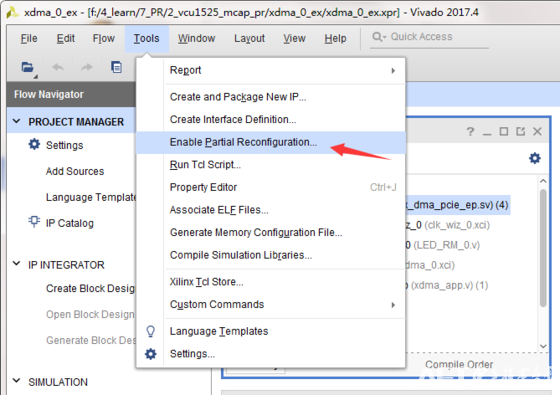

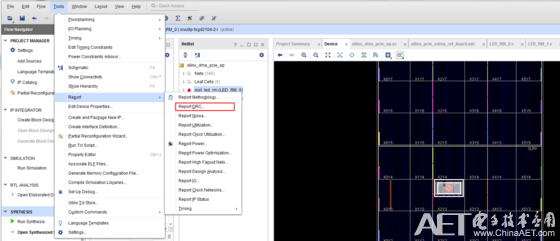

14.完成上述步骤之后,选择Tools->Enable Partial Reconfiguration...选项,将工程转换成支持PR类型的工程,在后续弹出的方框中选择Convert。

图13

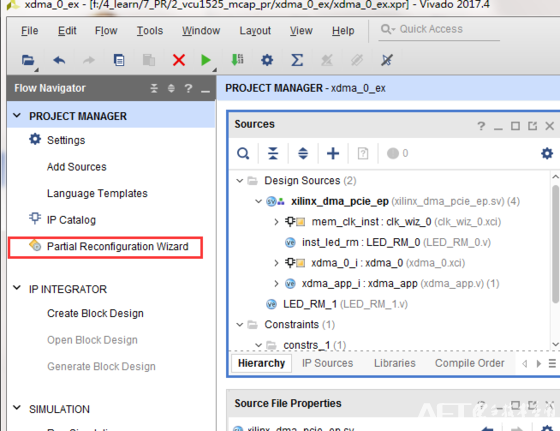

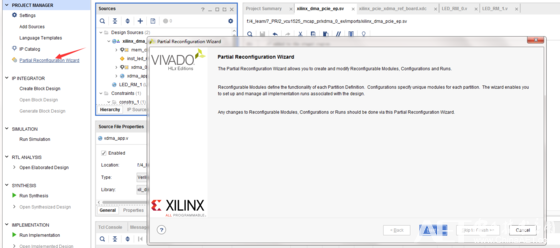

15.此时工程已经转换完成,对比转换之前,在Flow Navigator的PROJECT MANAGER会多出Partial Reconfiguration Wizard选项。

图14

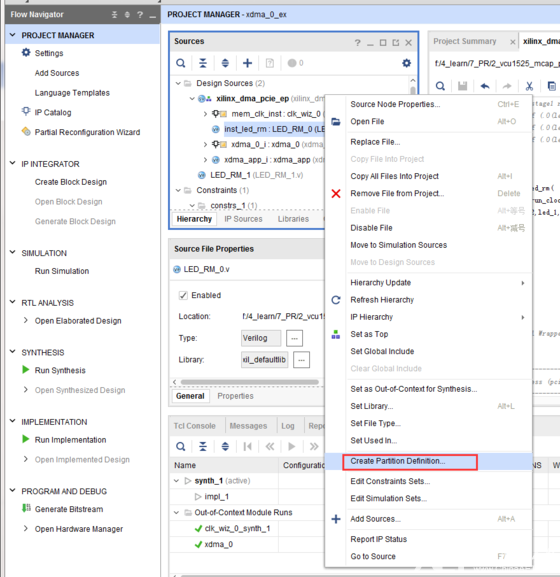

16.设置我们要进行部分重构的逻辑,即LED_RM_x模块,如下图所示,右键LED_RM_0,选择Create Partition Definition...

图15

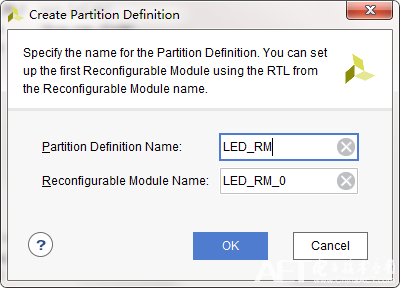

17.在弹出的窗口中指定一个分区的名字,这里设置为LED_RM,点击OK。

图16

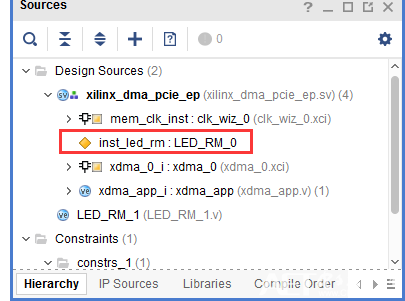

18.完成上一步之后,LED_RM_0模块变成了一个黄色的棱形标志,如下图所示。

图17

19.打开Partial Reconfiguration wizard

图18

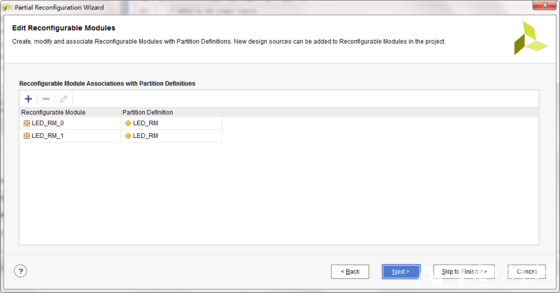

20.在Edit Reconfiguration Modules界面中,点击“+”符号,把LED_RM_1添加进来,表明有两个重配置模块,添加完成后如下图所示,属于LED_RM分区定义列表里面有LED_RM_0和LED_RM_1两个重配置模块。

图19

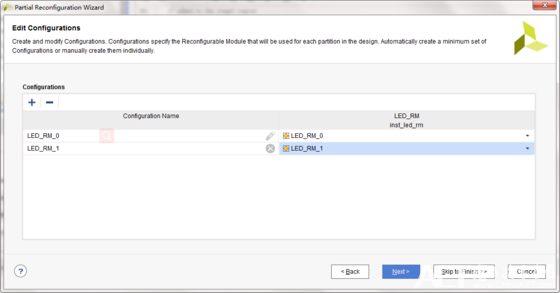

21.在Editing Configurations界面中,选择automatically create configurations,并修改Configuration Name,如下图所示。

图20

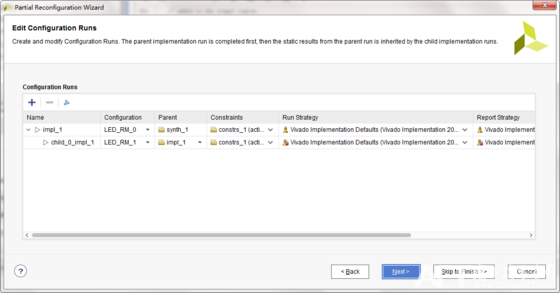

22.在Edit Configuration Runs界面中,选择automatically create configurations。

图21

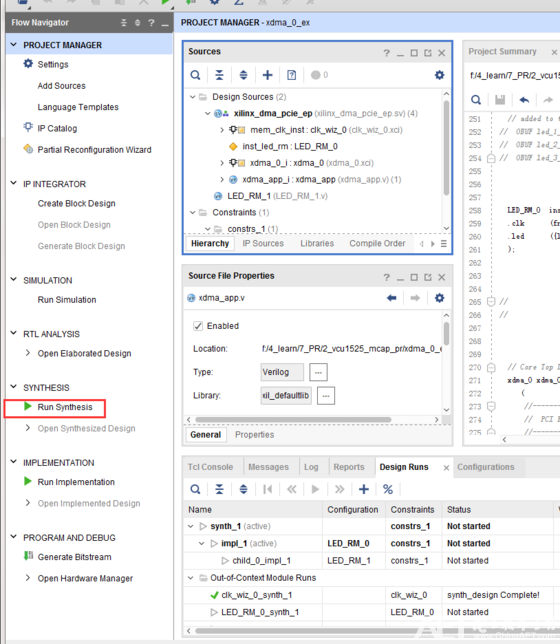

23.最后,点击Finish,部分重配置的向导设置完成,然后点击Run Synthesis综合设计。

图22

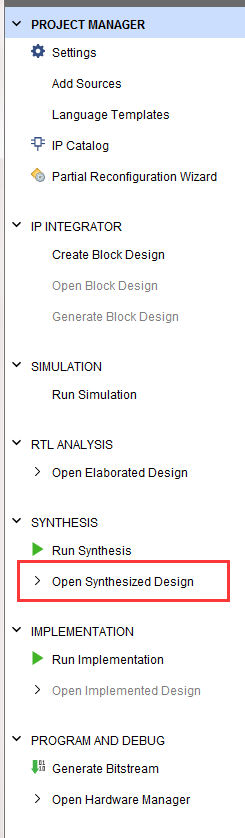

24.综合完成之后打开综合设计。

图23

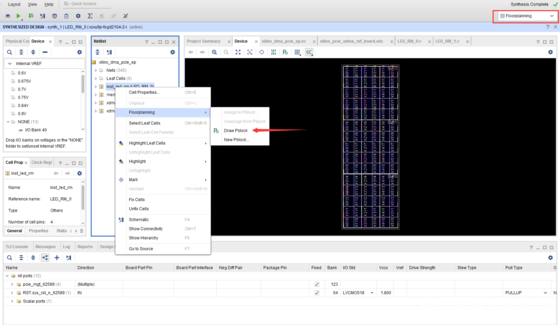

25.在Floorplanning界面,右键LED_RM_0,选择Floorplanning->Draw Pblock,给RM模块划分重配置的区域。

图24

26.在分配完重配置区域之后,保存相应的约束到xdc文件中,然后做DRC检查,检查分配的区域是否符合要求。

图25

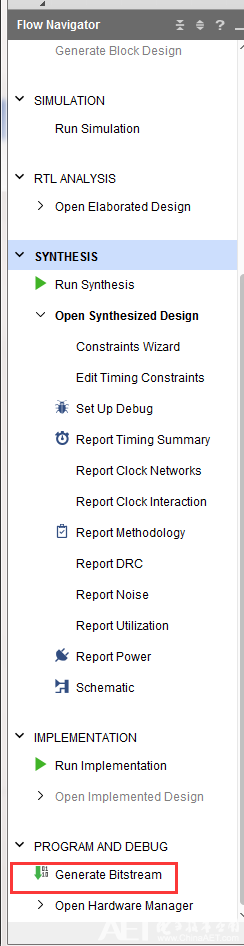

27.DRC检查没有问题之后,点击Generate Bitstream.

图26

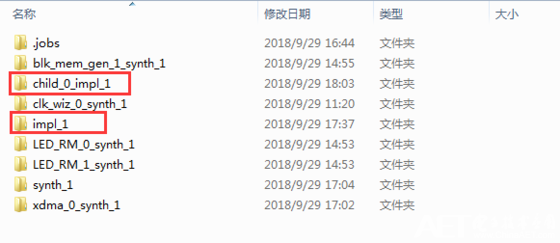

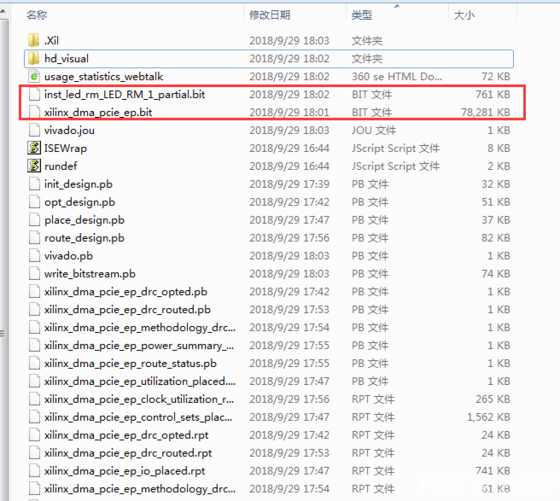

28.至此,部分重配置的工程就生成完毕,在生成出来的文件里面,在工程目录下会有两个imp的文件夹,里面会分别有静态逻辑和各自的重配置逻辑,我们将静态逻辑先烧写进去FPGA,之后就可以通过PCIE配置动态逻辑,关于MCAP的驱动的上位机,在Xilinx_Answer_64761__UltraScale_Devices这份文档中有详细的说明。

图27

图28

编辑:hfy

-

FPGA

+关注

关注

1629文章

21729浏览量

603050 -

Xilinx

+关注

关注

71文章

2167浏览量

121326 -

JTAG

+关注

关注

6文章

400浏览量

71675 -

PCIe

+关注

关注

15文章

1235浏览量

82597

发布评论请先 登录

相关推荐

PCIe信号完整性问题解决方案

基于相变材料的可重构超构表面用于图像处理

Cadence展示完整的PCIe 7.0 IP解决方案

PCIe 5.0 SerDes 测试

实测952Mbps!四路千兆网PCIe拓展方案,国产工业级!

新思科技PCIe 7.0验证IP(VIP)的特性

pcie4.0和pcie3.0接口兼容吗

麦格纳为中国本土汽车制造商提供可重构座椅系统

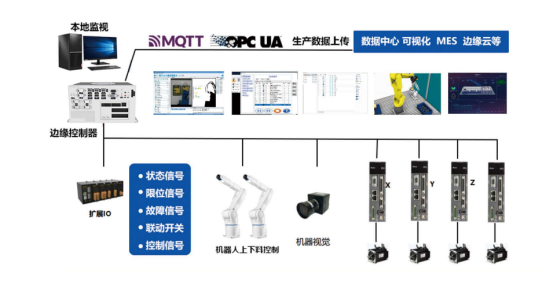

可重构柔性装配产线:AI边缘控制威廉希尔官方网站 的崭新探索

可重构柔性装配产线整体解决方案,智能化生产转型的引领者

高性能NVMe主机控制器,Xilinx FPGA PCIe 3

PCIe-AXI-Cont用户手册

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

基于PCIE(mcap)的部分可重构实现方案

基于PCIE(mcap)的部分可重构实现方案

评论