时序电路基本模型

首先对于纯组合逻辑电路来说,其逻辑功能块的输出仅仅与当前的输入值有关系,其电路延时分析也非常的简单,只考虑输入到输出的信号延时Tdelay,但是影响Tdelay时间的因素比较多,比如不同的器件输入到输出的延时时间不同,不同的工艺条件以及在不同的环境下,Tdelay的时间也不同。

所以组合逻辑电路的延时参数是不固定的,我们研究组合逻辑电路的延时没有实际意义。

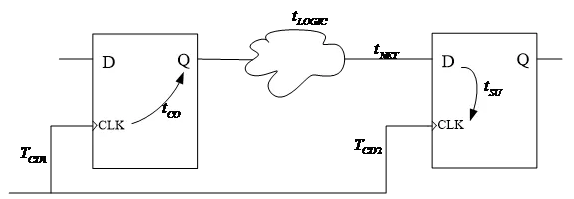

对于绝大部分的电路来说输出不仅取决于当前的输入值,也取决于原先的输入值,也就是说电路具有记忆功能,这属于同步时序电路,其基本时序模型如图1所示,。基本的时序模型就是由D触发器和多个延时参数组成的。在时钟的驱动下,从一个D触发器到另外一个D触发器信号传输过程中,为了保证信号的稳定传输,需要考虑到如下时序参数:

tCLK是时钟的最小周期,

tCO是寄存器固有的时钟输出延时,

tLOGIC是同步元件之间的组合逻辑延迟,

tNET是网线的延迟;

tSU是寄存器固有的时钟建立时间,

tCLK_SKEW是两个DFF之间的时钟扭曲

图1基本同步时序电路模型

三个重要的时序参数

同步时序电路由寄存器和组合逻辑组成,系统中所有的寄存器均在一个全局时钟的控制下工作,有三个重要的时序参数与寄存器有关。

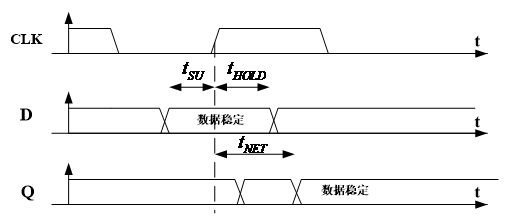

1. 建立时间(tSU)

建立时间是在时钟翻转(对于正沿触发寄存器为0→1的翻转)之前数据输入(D)必须有效的时间。

2. 保持时间(tHOLD)

保持时间是在时钟边沿之后数据输入必须仍然有效的时间。

假设建立和保持时间都满足的情况下,那么输入端D处的数据则在最坏情况下的传播延时(tNET)之后被复制到了输出端Q,如图2所示。

图2 同步寄存器的建立时间、保持时间以及传播延迟的定义

3. 最高时钟频率

熟悉了建立时间、保持时间以及传播延迟的基本概念,下面通过这三个基本参数来推导时钟的最高频率,对于同步时序逻辑电路,对时钟激励做出响应的开关事件是同时发生的,但是运行结果必须等到下一个时钟翻转时才能进入到下一级,也就说,只有在当前所有的计算都已经完成了并且系统开始闲置的时候下一轮的操作才能开始,

因此,为了保证时序电路数据采集和处理的正确性,时钟周期tCLK必须能容纳电路中任何一级的最长延时。假设该组合逻辑的最长延时等于tLOGIC,那么时序电路正确工作要求的最小时钟为:

tCLK = tCO+tLOGIC+tNET+tSU(公式1)

其中tNET为传输延迟,tCO 是寄存器固有的时钟输出延时,那么通过公式1很容易得到系统的最高频率fMAX,常用表示:

fMAX = 1/tCLK (公式2)

我们假设寄存器的固有最小延时时间为tCOregister,那么为了保证时序电路正常工作,还需要如下的约束:

tCOregister + tLOGIC >= tHOLD (公式3)

这一约束保证了时序元件的输入数据在时钟边沿之后能够维持足够长的时间,并且不会由于新来的数据流而过早的改变。

总结

本文介绍了时序模型和时序电路的几个重要参数,在下面的文章中,会重点介绍同步和异步的区别以及异步电路同步化的处理技巧。

编辑:hfy

-

寄存器

+关注

关注

31文章

5343浏览量

120379 -

时序电路

+关注

关注

1文章

114浏览量

21700

发布评论请先 登录

相关推荐

同步时序电路需要考虑的三个重要的时序参数

同步时序电路需要考虑的三个重要的时序参数

评论