作者: OpenSLee

1 概述

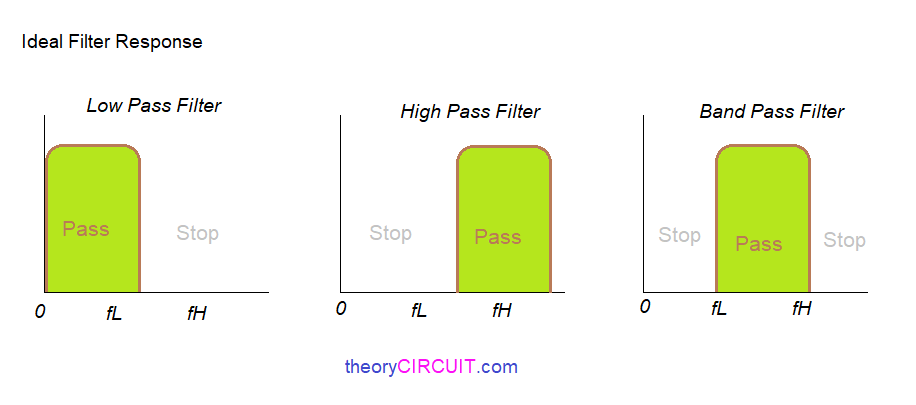

在数字信号处理中,CIC滤波器是FIR滤波器中最优的一种,其使用了积分,梳状滤波器级联的方式。

CIC滤波器由一对或多对积分-梳状滤波器组成,在抽取CIC中,输入信号依次经过积分,降采样,以及与积分环节数目相同的梳状滤波器。在内插CIC中,输入信号依次经过梳状滤波器,升采样,以及与梳状数目相同的积分环节。

CIC滤波器的发明者是 Eugene B. Hogenauer,这是一类使用在不同频率的数字信号处理中的滤波器,在内插和抽取中使用广泛。与大多数FIR滤波器不同的是,它有一个内插或者抽取的结构。

1,线性相位响应

2,仅需延迟,加减法便可实现,不需要乘法,在FPGA等平台上易于实现。

2 单级CIC滤波器

CIC滤波器的冲击响应为:

3 设计目标

利用单级CIC滤波器将采样率为352.8KHZ的1khz sin波向下降采样率到44.1khz的1khz sin波(8倍抽取)。

1,matlab设计验证

2,FPGA verilog设计验证。

4 matlab设计验证

%Single CIC %352.8khz sample rate down to 44.1khz sample rate close all clc clear all %参数定义 FS =352800; %Sample rate Frequncy fc = 1000; %1khz N = 1024; Q = 16; M= 8; D = 8; t =0:2*pi/FS:2*pi*(N-1)/FS;%时间序列 %波形产生 sin_osc =sin(t*fc); %滤波器系数 b=ones(1,M); a = 1; %8倍抽值处理 sf=filter(b,a,sin_osc); sm =sf./M; sd=sm(1:D:length(t)); %绘图 figure(1), subplot(221),stem(sin_osc); title('采样频率352.8khz 1khz sin','fontsize',8); subplot(222),stem(si0); title('采样频率44.1khz 1khz sin','fontsize',8); subplot(223);plot(f,mag); xlabel('频率(Hz)','fontsize',8); ylabel('幅度(dB)','fontsize',8); title('freqz()幅频响应','fontsize',8); subplot(224);plot(f,ph); xlabel('频率(Hz)','fontsize',8); ylabel('相位(度)','fontsize',8);

图1 8倍抽取前后的1khz sin时域波形

图2 滤波器系数的幅频和相频响应

由图1和图2分析可知,单级CIC滤波器的降采样率设计成功。

5 FPGA设计验证

FPGA的单级cic滤波器的设计其实就是一个滑动平均滤波器,由一个累加器和一个移位操作完成。

`timescale 1ps/1ps

module cic(

input mclk,//45.1584MHZ

input reset_n,

input signed[31:0] pcm_in,//352.8khz

output signed[31:0] pcm_out //44.1khz

);

localparam LAST_CYCLE = 128;

reg [9:0] i;//44.1

reg signed [35:0] temp_pcm;

reg signed [35:0] dout_pcm;

assign pcm_out = dout_pcm[35:4];

always @(posedge mclk or negedge reset_n) begin

if(reset_n == 1'b0) begin

i <= 0;

temp_pcm<=0;

dout_pcm<=0;

end

else begin

i<= i+1;

if(i == (LAST_CYCLE-1) || i == (LAST_CYCLE*2-1) ||i == (LAST_CYCLE*3-1) || i == (LAST_CYCLE*4-1) || i == (LAST_CYCLE*5-1)||i == (LAST_CYCLE*6-1) ||i == (LAST_CYCLE*7-1) ) temp_pcm <= temp_pcm + pcm_in;

if(i == (LAST_CYCLE*8-1)) begin

dout_pcm<= temp_pcm + pcm_in;

temp_pcm<=0;

end

end

end

endmodule

图3 modelsim时域数据检测

图4 modelsim时域波形

图5 matlab还原数据的时域和频域

由图3,图4,和图5分析,1khz基本未发生改变,44.1khz相对于352.8khz采样率1khz点变得疏松。

编辑:hfy

-

FPGA

+关注

关注

1629文章

21729浏览量

603044 -

数字信号处理

+关注

关注

15文章

560浏览量

45847 -

fir滤波器

+关注

关注

1文章

95浏览量

19037 -

CIC滤波器

+关注

关注

0文章

15浏览量

10539 -

梳状滤波器

+关注

关注

0文章

5浏览量

6636

发布评论请先 登录

相关推荐

基于FPGA实现FIR数字滤波器

基于FPGA的单级cic滤波器设计方案

基于FPGA的单级cic滤波器设计方案

评论