在ZYNQ进阶之路2中我们讲解了PL端PWM呼吸灯的设计,本节我们讲解PL端实现串口UART的发送设计;

首先新建一个串口发送的工程,工程建立在ZYNQ进阶之路1中已经讲述,这里不再累述;

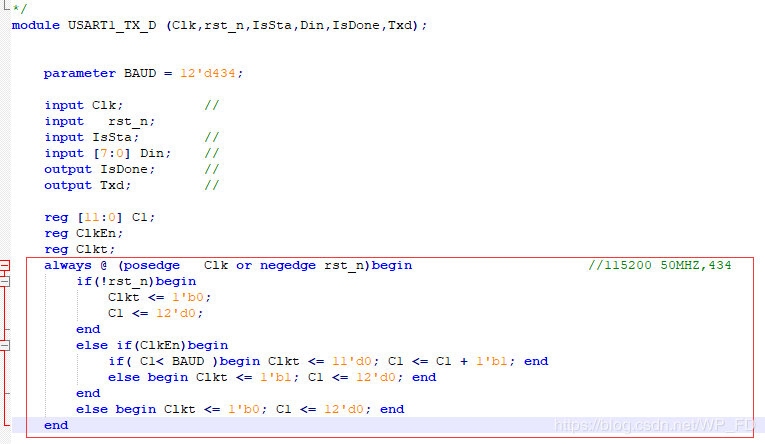

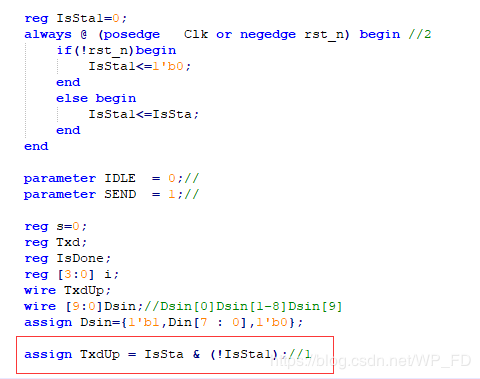

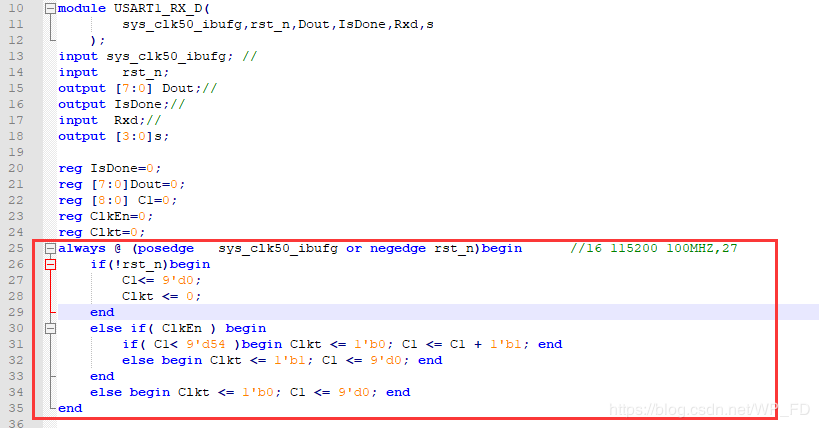

下面主要是uart发送模块的编码讲述,uart发送模块设计主要分为波特率控制计数逻辑和按位发送逻辑,其具体编码如下所示:

波特率控制计数逻辑:

其中BAUD = 434是根据主时钟频率为50Mhz,这里我们去波特率为115200,所以计数值BAUD = 50000000/115200 =434;

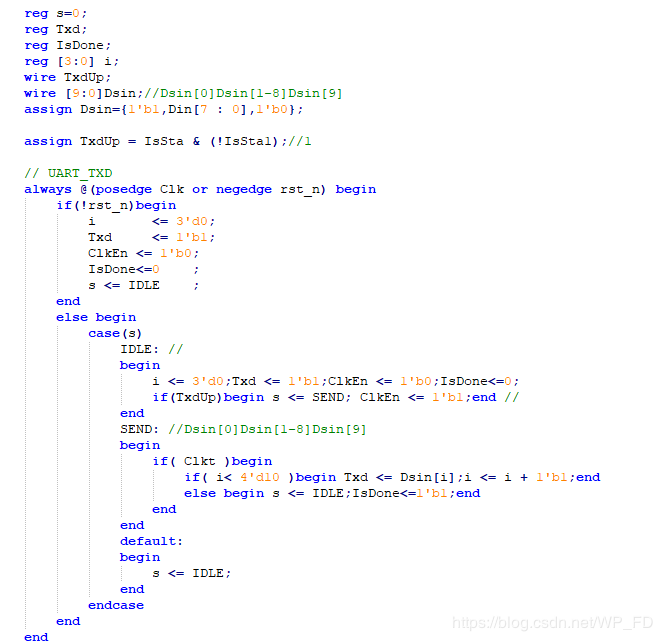

按位发送逻辑如下所示:

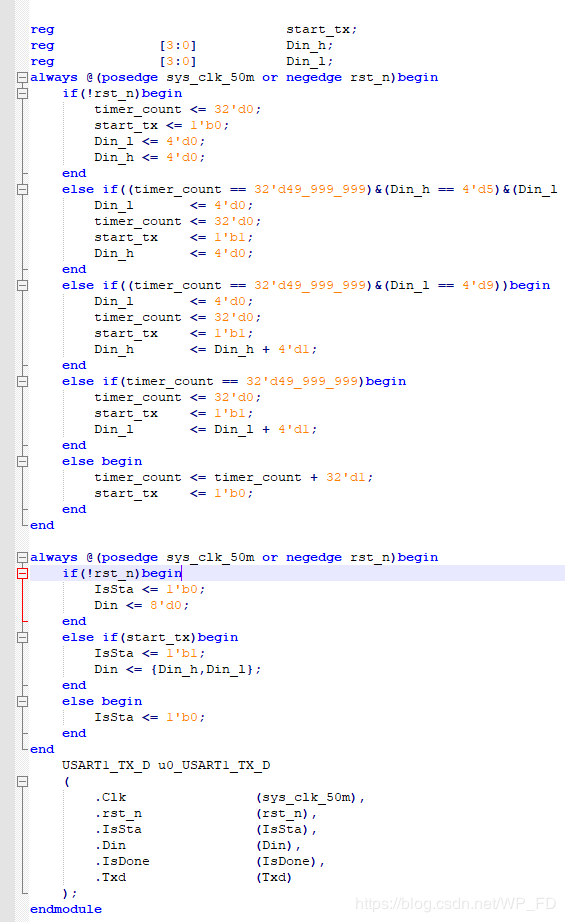

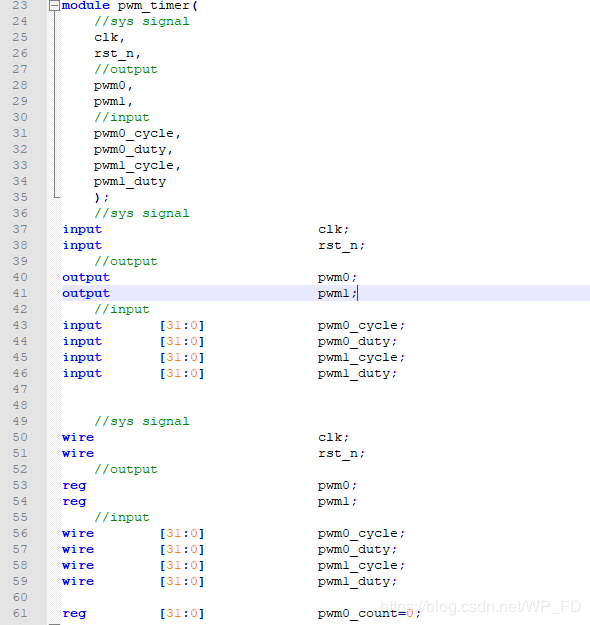

然后我们需要一个顶层文件,让串口按照每秒钟发送一个秒计时数据出去(BCD码),器逻辑代码如下所示:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

uart

+关注

关注

22文章

1235浏览量

101358 -

波特率

+关注

关注

2文章

307浏览量

34117 -

Zynq

+关注

关注

10文章

609浏览量

47176

发布评论请先 登录

相关推荐

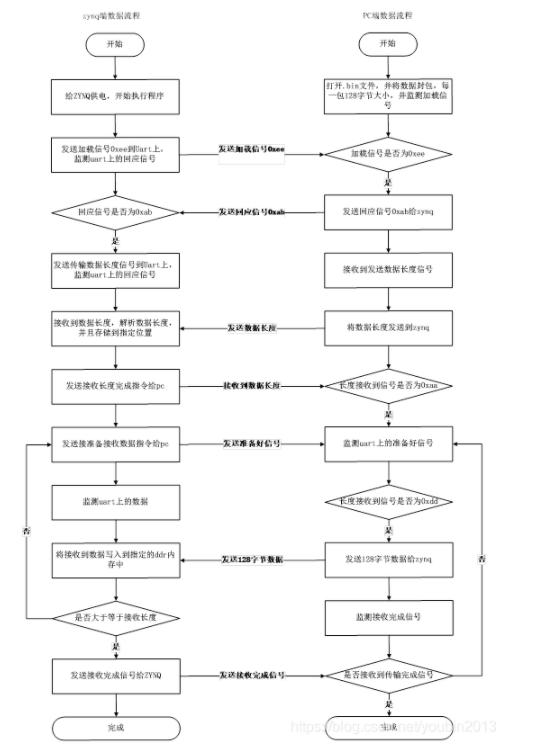

ZYNQ开发案例之ZYNQ的UART加载

,最终将这个文件写入到QSPIFLASH中,整个ZYNQ在配置好启动方式为FLASH启动后,便可做到上电自启动运行下载到FLASH中的用户程序。 为了实现远程加载,抛开仿真器,通过UART的方式将固定的.bin文件发送给

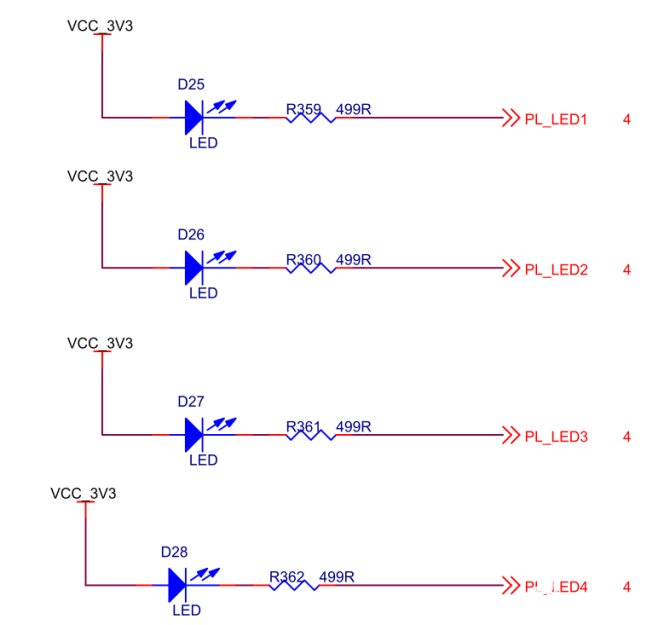

【ZYNQ Ultrascale+ MPSOC FPGA教程】第四章PL的LED实验

对于ZYNQ来说PL(FPGA)开发是至关重要的,这也是ZYNQ比其他ARM的有优势的地方,可以定制化很多ARM端的外设,在定制ARM端的外

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十九章PL端AXI GPIO的使用

使用zynq最大的疑问就是如何把PS和PL结合起来使用,在其他的SOC芯片中一般都会有GPIO,本实验使用一个AXI GPIO的IP核,让PS端通过AXI总线控制PL

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十二章PL读写PS端DDR数据

PL和PS的高效交互是zynq soc开发的重中之重,我们常常需要将PL端的大量数据实时送到PS端处理,或者将PS

怎么在Petyninux 2014.4上使用Zynq上的PL UART?

你好我在Zynq 7010设计上添加了一个UART 16550 IP,中断直接连接到Zynq INTC。在petalinux中导入硬件设计后,pl.dtsi结构似乎没问题,但是当我编译

发表于 04-08 07:50

zynq 7020 PS和zynq PL是如何通话的?

嗨,我必须找出zynq 7020 PS和zynq PL如何通话,特别是我必须找到将在ARM中处理的SDK C代码。你能用一个明确的C代码告诉我,它解释了数据如何从PS转移到PL,这是A

发表于 05-08 09:37

请问zynq 怎么实现PS与PL数据交互,然后通过UART串口打印出来?

请问zynq 怎么实现PS与PL数据交互,然后通过UART串口打印出来?前辈们做过的指导我一下。

发表于 08-03 15:53

使用Zynq PL结构时钟驱动代码没有反应是为什么?

错误。然后,我在SDK中编程PS端,led闪烁正确的频率!我的问题,当锁定Zynq PL时钟? PS程序之后?需要多长时间?是不是意味着,PL配置期间LED闪烁错误,在非易失性Flas

发表于 08-27 15:09

PS端实现FreeRTOS嵌入式系统

ZYNQ进阶之路9--PS端实现FreeRTOS嵌入式系统导论FreeRTOS简介实现步骤导论在之前的章节中我们我们完成了PS端、PL

发表于 12-22 08:29

AD9681是否可被zynq-7020的pl端驱动?

您好:

我想咨询AD9681是否可以被zynq-7020的PL端驱动(zynq7020的性能是否足够)。我们需要做卫星的探测载荷,由于卫星能源控制严格,我们需要低功耗、多通道(至少8个

发表于 12-04 08:18

关于Zynq-7000 PL端HDMI的显示控制的性能分析和应用介绍

Zynq-7000 PL端HDMI的显示控制 Zynq-7000 PS到PL端emio的使用 V

发表于 09-15 14:57

•3679次阅读

ZYNQ进阶:PL端UART 发送设计案例

ZYNQ进阶:PL端UART 发送设计案例

评论