1、实际走线分析:

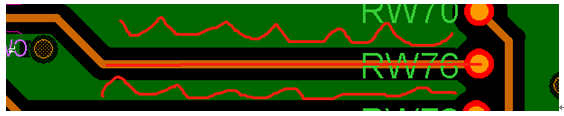

上面的走线橘色为信号走线,周围绿色(波浪标注)为周围包地,下方为第二层完整地平面。

从上图来看设计师的本意是好的,有参考地平面,周围也有包地,此时设计正确的话可以保证回流路径阻抗最小,因为可以从两边包地回流和地平面回流,此时可以效果最好。

但是,上面出现的问题就是包地并未通过地孔和地平面连接起来。具体如下所示:

假设回流路径是两边包地,信号流向为从右向左,下边部分包地红色路径为回流信号,此时回流信号向右走,但是因为前面没有接地孔,所以信号返回,寻找最小路径(图中下边白色路径);另上边回流也是,因为靠近过孔处无接地过孔,则信号沿着灰色路线找到最近的接地过孔,此时这两个不完整的包地,导致了信号路径阻抗不是最小,且下边走线较细,寄生电感较大,且为一端接地,此时模型就是一个天线,很有可能导致“天线辐射能量”,所以有了完整的地平面,包地只是锦上添花的行为,但是一定要注意包地处理不好,有可能导致更为严重的辐射。

最好的解决方法如下:

在两边包地线上沿一定距离打上接地/包地过孔,此时可以解决回流路径阻抗增大的问题。

2、实际走线分析

如下图所示为一组PCIE走线,其中包括三组差分线,发送、接收和时钟参考。如下走线差分线走的没有问题,但是背部的横向走线切断了背面的完整地平面,虽然走线周围是有完整包地的,但是地平面被三端走线破坏严重。如果做高速分析以及实际测试验证很久的话,我们都知道完整的地平面是根本,周围包地只是锦上添花的行为,我们以时钟来分析信号回流。

时钟信号回流分析:

时钟信号是由PCIE主机给到PCIE从机的,所以信号流向是指向左下角的。而此时的信号回流路径包含包地路径和地平面路径。

包地路径很好,信号直接沿着包地路径回流没有多大问题;但是对于地平面回流就存在问题了,所以此时来看一下:

假设地平面回流信号在未分割处是在信号下方镜像回流,但是因为下方走线导致地平面被破坏,假设黄色箭头指示为地平面回流信号,当遇到分割,则电流沿着分割界面一直走,直到绕过分割平面,然后再回到信号路径镜像对应面;当然也有一条路径是寻找最近过孔,如白色路径,沿着过孔走顶层,再经过过孔回到底层参考地,此时大家发现一个很明显的问题那就是路程变长了(因为绕路了),此时在低频下没有问题,但是在高频下速率很高,一个简单的上升沿就可能导致辐射严重超标,而此时回流路径变长,寄生电感增加,感抗变大,很有可能导致严重的EMC问题,所以请一定不要这样做。

所以成本允许的话,对于这种一定设计为四层板,因为两层板真的很难找到一个完整的地参考平面,哪怕四层板完整的参考地没有,但是对应信号层找出完整的电源平面也是可以的。另外而言,是在不允许,则可以在分割的两个地之间连接一个0欧姆电阻,也就是我们俗称的“跨接电阻”,就是把两边连接起来,此时回流信号直接走我们搭建的“跨街桥”就行,不用绕路,当然阻抗就是最小的。

编辑:hfy

-

PCIe

+关注

关注

15文章

1235浏览量

82597 -

走线

+关注

关注

3文章

113浏览量

23903 -

时钟信号

+关注

关注

4文章

448浏览量

28542 -

差分线

+关注

关注

0文章

37浏览量

8905 -

回流路径

+关注

关注

0文章

12浏览量

6741

发布评论请先 登录

相关推荐

高速信号回流环路实际走线分析

高速信号回流环路实际走线分析

评论