Xilinx的开发板ZCU102支持休眠到内存(suspend-to-ram)。休眠到内存时,DDR进入自刷新,MPSoC被关电,完全不耗电。唤醒时,MPSoC根据外部输入信号判断出不是上电启动而是休眠,就从DDR读出系统状态,恢复系统。

MPSoC启动时,它的DDR控制器会驱动DDR的复位信号,有可能破坏DDR里的数据。为了避免这种情况,需要对DDR复位信号进行特殊设计。

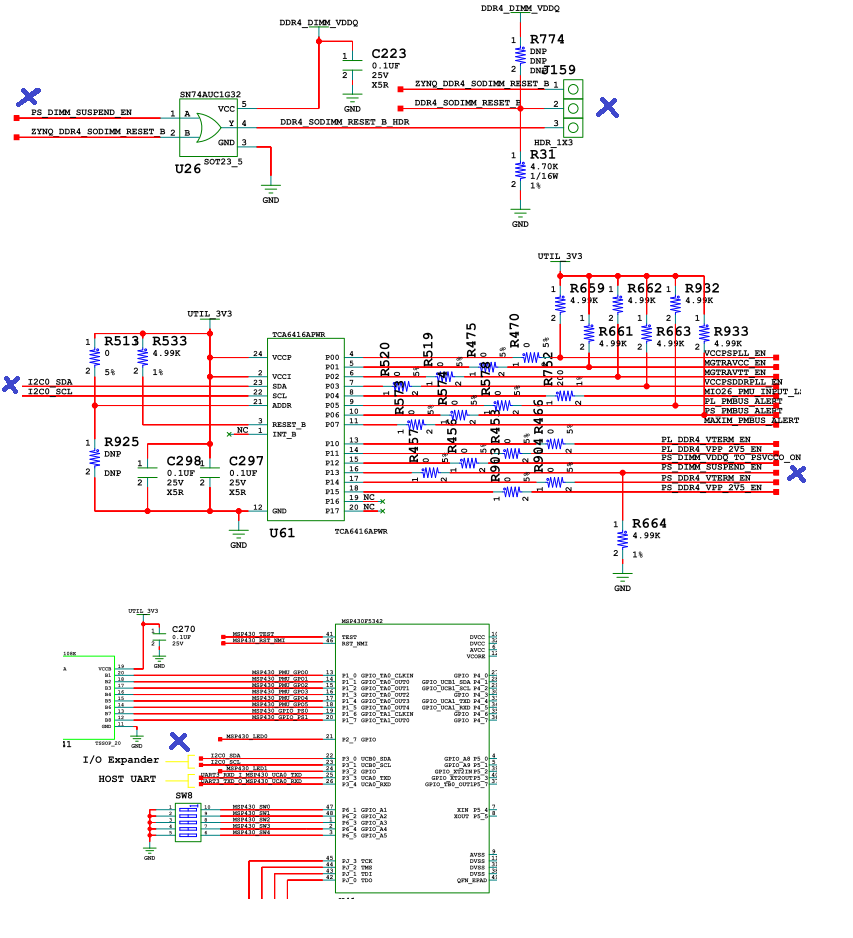

在开发板ZCU102上,DDR复位信号由外部单片机MSP430和MPSoC联合控制,两个的控制信号经过SN74AUC1G32(2输入或)再连接到DDR内存条。MSP430的信号有下拉,缺省情况下只由MPSoC控制DDR复位信号。如果需要支持休眠到内存(suspend-to-ram),MSP430控制I2C芯片输出高,相当于屏蔽了DDR复位功能,使DDR内存条一直不被复位。

下面是相关的原理图。DDR4_SODIMM_RESET_B信号连接到DDR内存条。ZYNQ_DDR4_SODIMM_RESET_B是从MPSoC来的信号。PS_DIMM_SUSPEND_EN来自于MSP430控制的I2C芯片TCA6416APWR。

-

单片机

+关注

关注

6036文章

44555浏览量

634853 -

DDR

+关注

关注

11文章

712浏览量

65318 -

Xilinx

+关注

关注

71文章

2167浏览量

121338 -

MPSoC

+关注

关注

0文章

198浏览量

24272 -

复位信号

+关注

关注

0文章

54浏览量

6316

发布评论请先 登录

相关推荐

Zynq UltraScale + MPSoC USB 3.0 CDC器件类设计

为什么在Vivado(任何版本)中没有ZCU102的板级支持?

请问Zynq Ultrascale + MPSOC本身是否存在问题?

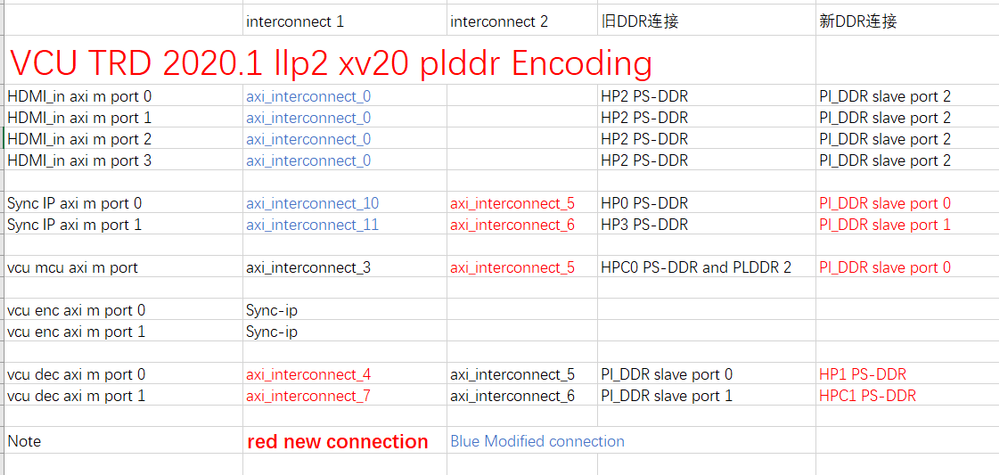

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器

如何使用ZCU102评估板来运行应用

Zynq UltraScale+ MPSoC ZCU102评估套件解决方案

Zynq UltraScale+ MPSoC的ZCU102开发套件的开发流程

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?

Zynq UltraScale + MPSoC的DDR接口

在MPSoC ZCU106单板的HDMI-Tx上基于eglfs_kms的运行QT应用程序

ZCU106在PLDDR实现超低延时编码

zcu102和zcu104有什么区别

AMD/Xilinx Zynq® UltraScale+ ™ MPSoC ZCU102 评估套件

ZCU10中MPSoC对DDR复位信号设计

ZCU10中MPSoC对DDR复位信号设计

评论