几十年来使用的三种最常见的多线串行数据传输格式是I2C,UART和SPI。本文着眼于串行外设接口(SPI)总线,该总线已摆脱了显式的标准化,因此在实现协议之前,请始终检查要使用的集成电路的数据表。

能力和特点

串行外围设备接口总线使用四个数据线在主设备和从设备之间提供全双工同步通信。

基本主从配置

串行外设接口允许将数据位从主设备移出到从设备中,同时,还可以将位从从设备移出到主设备中。

动画1显示了数据从Microchip A移入Microchip B,又从Microchip B移入MicrochipA。

动画2显示了两个微芯片之间SPI事务的虚拟4通道示波器轨迹。由马克·休斯(Mark Hughes)用Mathematica创建

由于SPI尚未标准化,因此可能会遇到先传输最高有效位(MSb)或最低有效位(LSb)的情况。检查设备的数据表并相应地设置数据处理例程。如果您使用的是Arduino,则可以参考此页面以获取有关配置SPI端口的信息。

时钟极性和相位

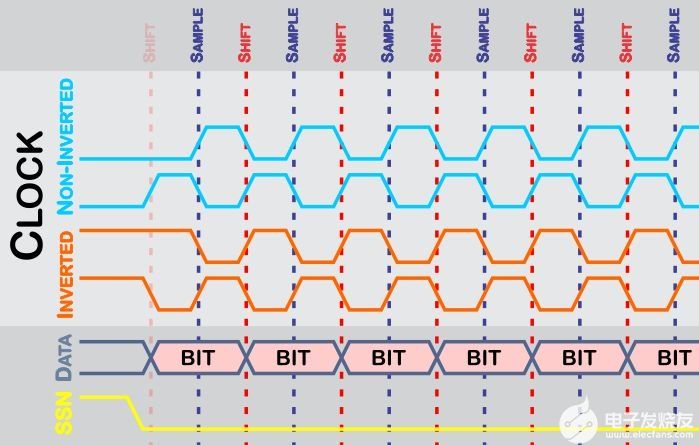

时钟转换控制数据的移位和采样。SPI具有四种模式(0、1、2、3),分别对应四种可能的时钟配置。

在时钟周期的上升沿采样的位在时钟周期的下降沿移出,反之亦然。

当从选择线被驱动至逻辑低电平(从选择通常为低电平有效信号)时,每个事务开始。从选择线,数据线和时钟线之间的确切关系取决于如何配置时钟极性(CPOL)和时钟相位(CPHA)。

在时钟极性不变的情况下(即,当从器件选择转换为逻辑低电平时,时钟处于逻辑低电平):

模式0:配置时钟相位,以便在时钟脉冲的上升沿采样数据,并在时钟脉冲的下降沿移出数据。这对应于上图中的第一个蓝色时钟轨迹。注意,数据必须在时钟的第一个上升沿之前可用。

模式1:配置时钟相位,以便在时钟脉冲的下降沿采样数据,并在时钟脉冲的上升沿移出数据。这对应于上图中的第二条蓝色时钟轨迹。

在时钟极性反转的情况下(即,当从器件选择转换为逻辑低电平时,时钟处于逻辑高电平):

模式2:配置时钟相位,以便在时钟脉冲的下降沿采样数据,并在时钟脉冲的上升沿移出数据。这对应于上图中的第一个橙色时钟轨迹。注意,数据必须在时钟的第一个下降沿之前可用。

模式3:配置时钟相位,以便在时钟脉冲的上升沿采样数据,并在时钟脉冲的下降沿移出数据。这对应于上图中的第二个橙色时钟轨迹。

关键参数

CLK:串行时钟。由主设备控制。每个时钟周期都会移出一个新的数据位。

SSN:从机选择(“ N”将其标识为低电平有效信号)。由主设备控制。激活的从设备选择线指示主机正在向相应的从设备发送数据或从其请求数据。

MOSI:主输出⇒从输入。数据离开主设备并进入从设备。芯片A上的MOSI线连接到芯片B上的MOSI线。

MISO:主机输入⇐从机输出。数据离开从设备并进入主设备(或以菊花链配置的另一个从设备;请参阅下一节)。芯片A上的MISO线连接到芯片B上的MISO线。

CPOL:时钟极性。这支配时钟信号的初始逻辑状态。有关更多信息,请参考上一节。

CPHA:时钟相位。这支配了数据转换和时钟转换之间的关系。有关更多信息,请参考上一节。

从选择和菊花链

多从选择配置

在标准的SPI安排中,主设备可以通过启用设备(即,将相应设备的从选择线设置为逻辑低电平)向共享公共数据线的单个设备写入数据或向其请求数据。注意不要同时启用多个从站,因为返回到主站的数据将由于MISO线之间的驱动程序争用而损坏。某些应用程序不需要将数据返回给主服务器;在这种情况下,如果主机希望将相同的数据发送到多个从机,则可以同时寻址多个从机。

在多从站选择配置中,每个从站都需要来自主站的唯一从站选择线。如果主站没有足够的I / O引脚来满足所需数量的从站,则可以通过合并解码器/多路分解器来实现I / O扩展,例如74HC(T)238(PDF)(3至8行)解码器/解复用器)。

菊花链配置

在此配置中,数据从一台设备移动到另一台设备。最终的从设备可以将数据返回给主设备。

在菊花链配置中,所有从机共享一条公共的从机选择线。数据从主机转移到第一个从机,然后从第一个从机转移到第二个,依此类推。数据沿线级联直至该系列中的最后一个从机,然后可以使用其MISO线将数据发送到主设备。

这种配置非常适合节日期间流行的可单独寻址的LED灯串。

结论

串行外设接口已经存在了数十年,没有理由期望它会很快消失。虽然I2C和UART可能会更受欢迎,但SPI是一种通用且直接的串行通信接口,非常适合某些应用。

fqj

-

SPI

+关注

关注

17文章

1706浏览量

91528 -

串行数据传输

+关注

关注

0文章

4浏览量

6826

发布评论请先 登录

相关推荐

KeyStone架构串行外设接口(SPI)手册

CAN总线的接口类型

SPI总线的定义和特点

电脑通用串行总线控制器怎么接

通用串行总线控制器和通用串行总线设备的区别

通用串行总线控制器影响什么设备

高速串行总线有哪些

南京沁恒微USB总线转接芯片 CH341

是否有可能使用CYSPP配置文件连接到外围设备?

什么是I2C接口?什么是I3C接口?I2C与I3C的区别

串行外围设备接口总线的特点以及它的基本配置

串行外围设备接口总线的特点以及它的基本配置

评论