保护三极管的基极

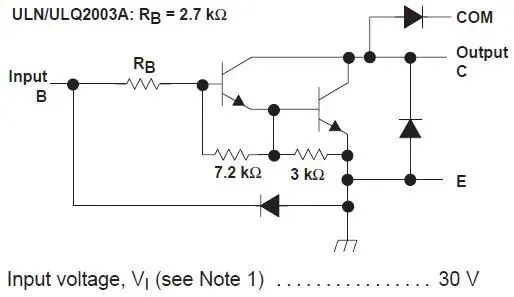

这次出现的问题是使用了ULN2003,由于直接用它的输入级接入模块的输入端,因此出现了问题。

由于电缆上存在分布电感和分布电容,因此很容易出现耦合,在ISO7637的实验中,存在高频脉冲250V,200ns

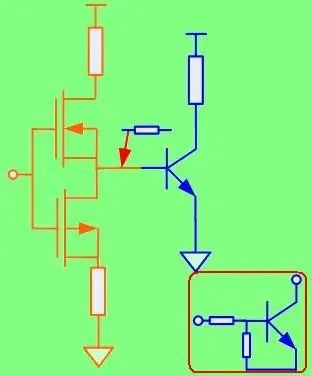

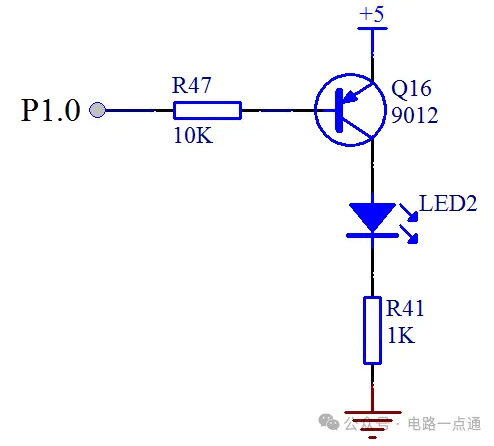

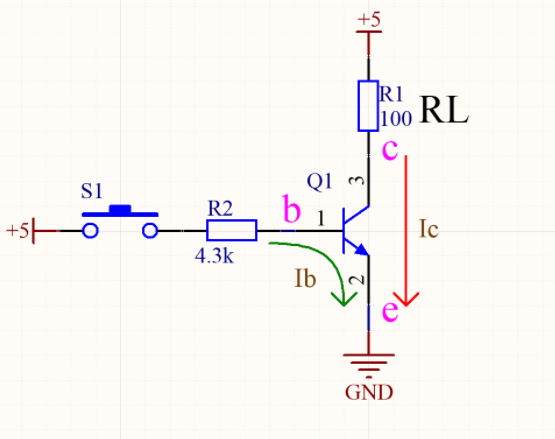

我们必须加入限流电阻,并且与RB和分压,或者加入其他抗瞬态的器件,这样的设计是非常耗成本的,因此一般可以采用分立的器件。

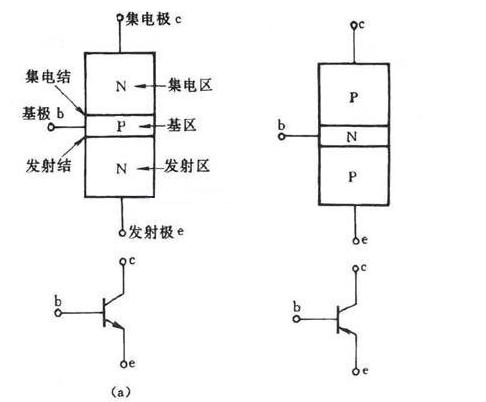

最好不用用晶体管的基极直接面对输入,这回造成很大的隐患。

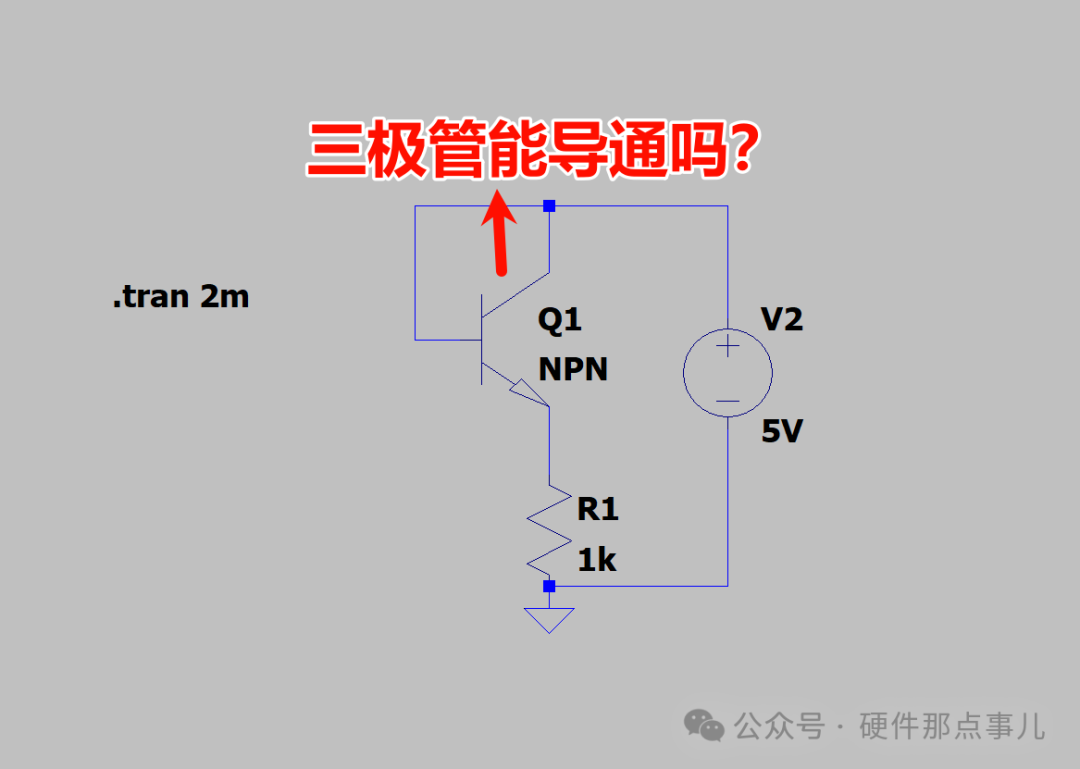

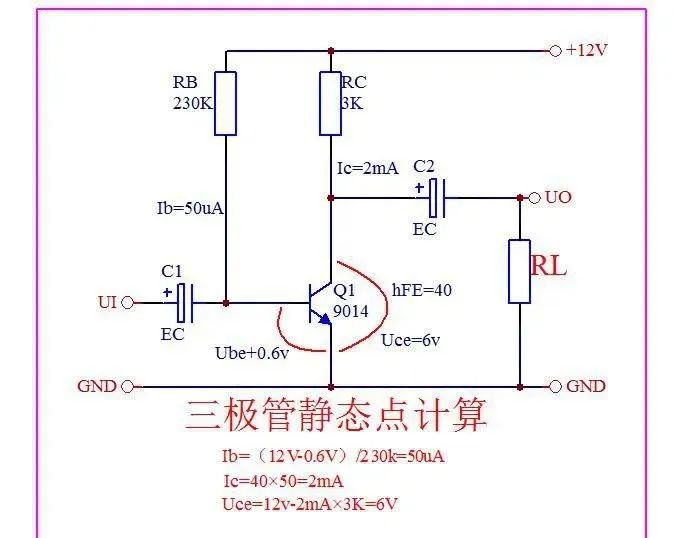

另外一个错误很常见,就是直接把晶体管的基极接至MCU的输出管脚上面,前面已经验算过MCU的输出能力:单片机IO口的驱动能力

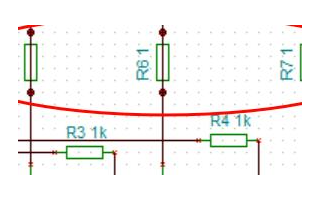

这很明显的造成了晶体管Ib过大,引起过大的损耗。

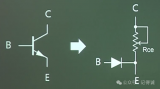

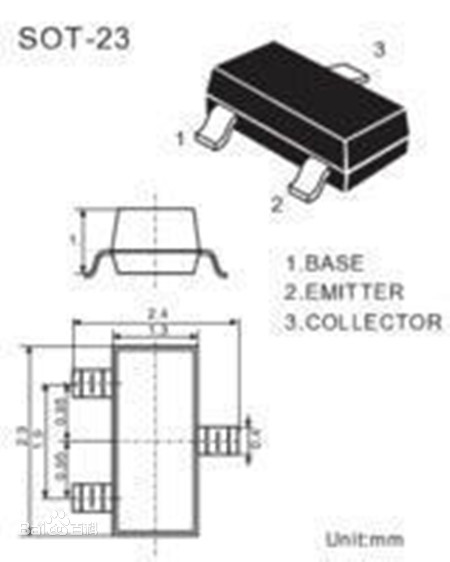

因此如果遇到分立的晶体管,注意验证它的基极,是否直接接MCU,是否内部含有限流电阻(Build-in),否则很可能造成过热和损坏。

这里顺便说明一下,三极管由于有热击穿效应,所以建议把余量放大些,60%~75%,否则很有可能造成损坏。

-

三极管

+关注

关注

142文章

3611浏览量

121878 -

基极

+关注

关注

0文章

18浏览量

8349

原文标题:简析保护三极管的基极

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

NPN三极管基极电压等于或高于集电极电压,三极管能导通吗?搞懂这个问题你就搞懂三极管电路了

三极管工作原理解析 三极管选择与应用指南

数字三极管的优点和应用

如果用多个三极管并联搭建扩流电路,多个三极管的基极共用一个电阻合理吗?

一文知道什么是保护三极管的基极

一文知道什么是保护三极管的基极

评论