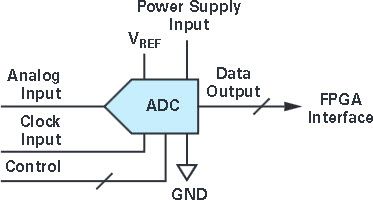

场可编程门阵列(FPGA)与模数转换器(ADC)输出的接口是一项常见的工程设计挑战。本文简要介绍各种接口协议和标准,并提供有关在高速数据转换器实现方案中使用LVDS的应用诀窍和技巧。

接口方式和标准

现场可编程门阵列(FPGA)与模数转换器(ADC)数字数据输出的接口是一项常见的工程设计挑战。此外,ADC使用多种多样的数字数据样式和标准,使这项挑战更加复杂。对于通常在200 MHz以下的低速数据接口,单倍数据速率(SDR) CMOS非常普遍:发送器在一个时钟沿传送数据,接收器在另一个时钟沿接收数据。这种方式可确保数据有充足的时间完成建立,然后由接收器采样。在双倍数据速率(DDR) CMOS中,发送器在每一个时钟沿都会传送数据。因此,在相同的时间内,它传输的数据量是SDR的两倍。然而,接收器正确采样的时序更加复杂。

并行低压差分信号(LVDS)是高速数据转换器的常见标准。它采用差分信号,每一位均有P线和N线;在最新的FPGA中,其速度可达DDR 1.6 Gbps或800 MHz。并行LVDS的功耗低于CMOS,但所需的线数则是CMOS的两倍,因而布线可能比较困难。

LVDS常常用在具有“源同步”时钟系统的数据转换器中,不过这并不是LVDS标准的一部分。在这种设置中,时钟与数据同相,并且与数据一同发送。这样,接收器就能使用该时钟更轻松地捕捉数据,因为它现在知道数据传输何时发生。

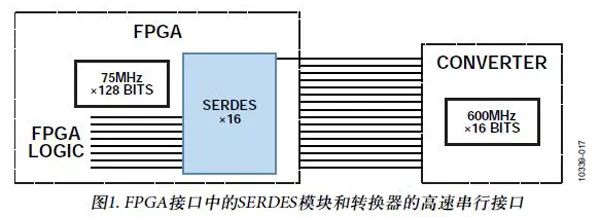

FPGA逻辑的速度一般跟不上高速转换器的总线速度,因此大多数FPGA具有串行器/解串器(SERDES)模块,用以将转换器端的快速、窄带串行接口转换为FPGA端的慢速、宽带并行接口。针对总线中的每个数据位,此模块输出2、4或8位,但以½、¼或1/8的时钟速率输出,从而有效地将数据解串。数据由FPGA内部的宽总线处理,其速度远低于连接到转换器的窄总线。

LVDS信号标准也用于串行链路,大部分是用在高速ADC上。当引脚数量比接口速度更重要时,通常使用串行LVDS。常常使用两个时钟:数据速率时钟和帧时钟。并行LVDS部分提到的所有考虑同样适用于串行LVDS。并行LVDS不过是由多条串行LVDS线组成。

I2C使用两条线:时钟和数据。它支持总线上的大量器件,而无需额外的引脚。I2C相对较慢,考虑协议开销,速度为400 kHz至1 MHz。它通常用在慢速、小尺寸器件上。I2C也常常用作控制接口或数据接口。

SPI使用3到4条线:

时钟

数据输入和数据输出(4线),或者双向数据输入/数据输出(3线)

片选(每个非主机器件使用一条线)

可用片选线有多少,SPI就能支持多少器件。它的速度可达约100 MHz,通常用作控制接口和数据接口。

串行PORT (SPORT)是一种基于CMOS的双向接口,每个方向使用一个或两个数据引脚。对于非%8分辨率,其可调字长能够提高效率。SPORT支持时域复用(TDM),通常用在音频/媒体转换器和高通道数转换器上。它提供每引脚约100 MHz的性能。

Blackn处理器支持SPORT,FPGA上可直接实现SPORT。SPORT一般仅用于数据传输,但也可以插入控制字符。

JESD204是一种JEDEC标准,用于单一主机(如FPGA或ASIC等)与一个或多个数据转换器之间的高速串行链路。最新规格提供每通道或每差分对最高3.125 Gbps的速度。未来的版本可能提供6.25 Gbps及更高的速度。通道采用8B/10B编码,因而通道的有效带宽降为理论值的80%。时钟嵌入在数据流中,因此没有额外的时钟信号。多个通道可以结合在一起以提高吞吐量,数据链路层协议确保数据完整性。在FPGA/ASIC中,为实现数据帧传输,JESD204需要的资源远远多于简单的LVDS或CMOS。它显著降低了接线要求,不过要求使用更昂贵的FPGA,PCB布线也更加复杂。

一般建议

进行ADC与FPGA的接口设计时,下列一般建议会有所帮助。

使用接收器、FPGA或ASIC的外部电阻终端,而不要使用FPGA内部终端,以免不匹配引起反射,致使超出时序预算。

如果系统使用多个ADC,请勿使用某个ADC的某个DCO。

布设连接到接收器的数字走线时,请勿采用大量“转接”(tromboning)来使所有走线保持等长。

利用CMOS输出端的串联终端降低边沿速率并限制开关噪声。确认所用的数据格式(二进制补码或偏移二进制)正确。

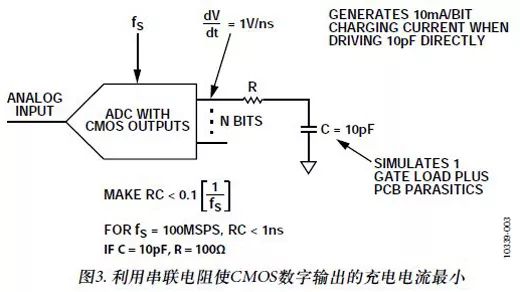

采用单端CMOS数字信号时,逻辑电平以大约1 V/nS的速度移动,典型输出负载为10 pF(最大值),典型充电电流为10 mA/位。应采用尽可能小的容性负载,使充电电流最小。这可以利用尽可能短的走线仅驱动一个门来实现,最好没有任何过孔。在数字输出端和输入端使用阻尼电阻,也可以使充电电流最小。

阻尼电阻和容性负载的时间常数应为采样速率周期的大约10%。如果时钟速率为100 MHz,负载为10 pF,则该时间常数应为10 nS的10%,即1 nS。这种情况下,R应为100 Ω。为获得最佳信噪比(SNR)性能,1.8 V DRVDD优于3.3 VDRVDD。然而,当驱动大容性负载时,SNR性能会下降。CMOS输出支持最高约200 MHz的采样时钟速率。如果驱动两个输出负载,或者走线长度大于1或2英寸,建议使用缓冲器。

ADC数字输出应小心对待,因为瞬态电流可能会耦合回interwetten与威廉的赔率体系 输入端,导致ADC的噪声和失真提高。

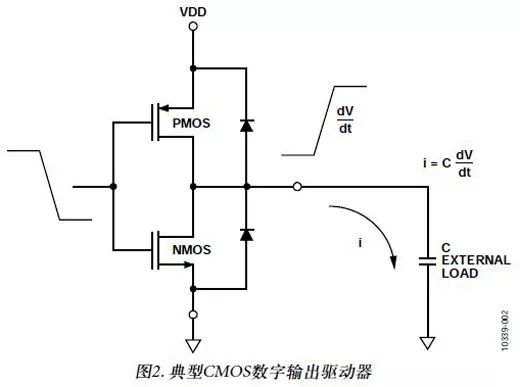

图2所示的典型CMOS驱动器能够产生很大的瞬态电流,尤其是驱动容性负载时。对于CMOS数据输出ADC,必须采取特别措施以使这些电流最小,不致于在ADC中产生额外的噪声和失真。

典型示例

图3显示了一个16位并行CMOS输出ADC的情况。每路输出有一个10pF负载,用以模拟一个门负载加上PCB寄生电容;当驱动10 pF负载时,各驱动器产生10 mA的充电电流。因此,该16位ADC的总瞬态电流可能高达16 × 10 mA = 160 mA。在各数据输出端增加一个小串联电阻R,可以抑制这些瞬态电流。应适当选择该电阻的值,使RC时间常数小于总采样周期的10%。如果fs = 100 MSPS,则RC应小于1 ns。C = 10 pF,因此最佳的R值约为100 Ω。选择更大的R值可能会降低输出数据建立时间性能,并干扰正常的数据捕捉。CMOS ADC输出端的容性负载应以单个门负载为限,通常是一个外部数据捕捉寄存器。任何情况下都不得将数据输出端直接连到高噪声数据总线,必须使用一个中间缓冲寄存器,使ADC输出端的直接负载最小。

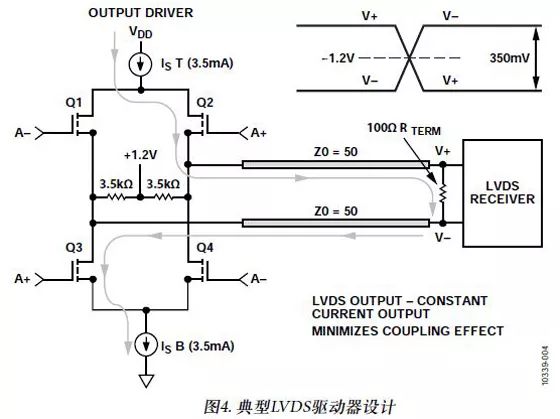

图4显示了CMOS中的一个标准LVDS驱动器。标称电流为3.5 mA,共模电压为1.2 V。因此,当驱动一个100 Ω差分终端电阻时,接收器各输入的摆幅为350 mV p-p,这相当于700 mV p-p的差分摆幅。这些数值来源于LVDS规范。

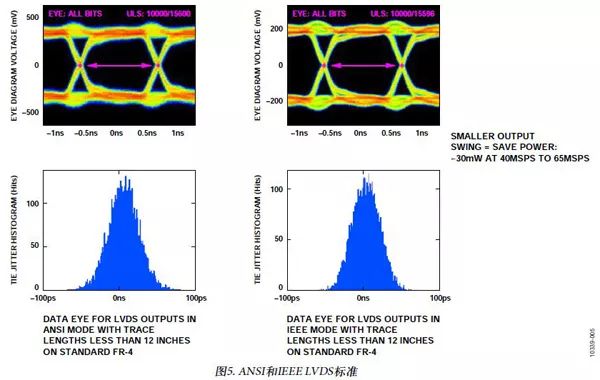

LVDS标准有两个:一个由ANSI制定,另一个由IEEE制定。虽然这两个标准类似且大致兼容,但并不完全相同。图5比较了这两个标准的眼图和抖动直方图。IEEE标准LVDS的摆幅为200 mV p-p,低于ANSI标准的320 mV p-p,这有助于节省数字输出的功耗。因此,如果IEEE标准支持目标应用及与接收器的连接,建议使用IEEE标准。

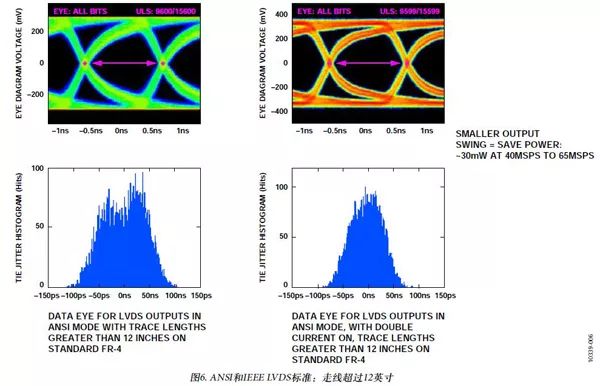

图6比较了走线长度超过12英寸或30厘米情况下的ANSI和IEEE LVDS标准。两幅图中,驱动电流均采用ANSI版标准。右图中,输出电流加倍,这可以净化眼图并改善抖动直方图。

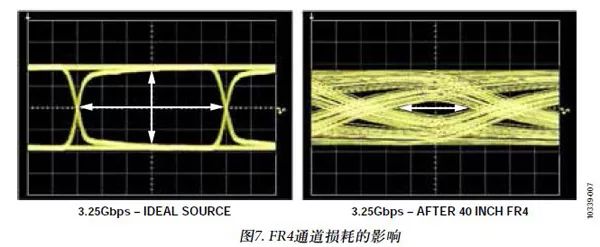

图7显示了长走线对FR4材料的影响。左图显示了发送器端的理想眼图。在距离40英寸的接收器端,眼图几乎闭合,接收器难以恢复数据。

故障排除技巧

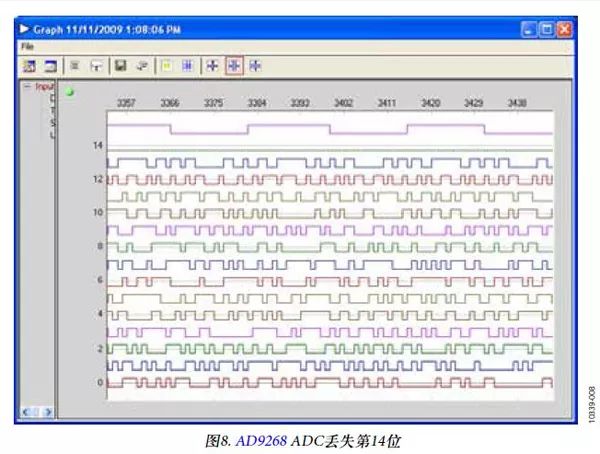

ADC丢失第14位

图8中,数据位的VisualAnalog数字显示表明,第14位从未跳变。这可能说明器件、PCB或接收器有问题,或者无符号数据不够大,无法使最高有效位跳变。

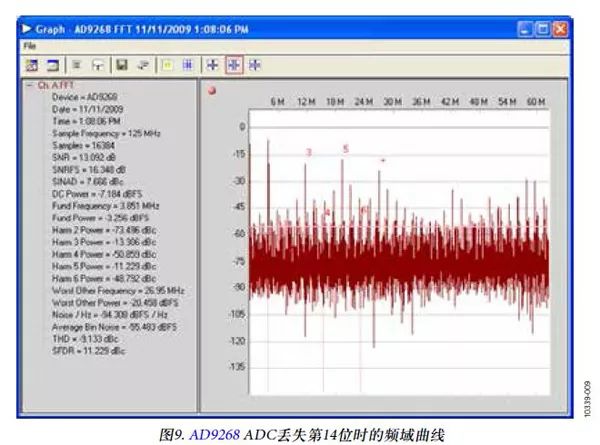

ADC丢失第14位时的频域曲线

图9显示了上述数字数据(其中第14位未跳变)的频域视图。该图说明,第14位有意义,系统中的某个地方发生错误。

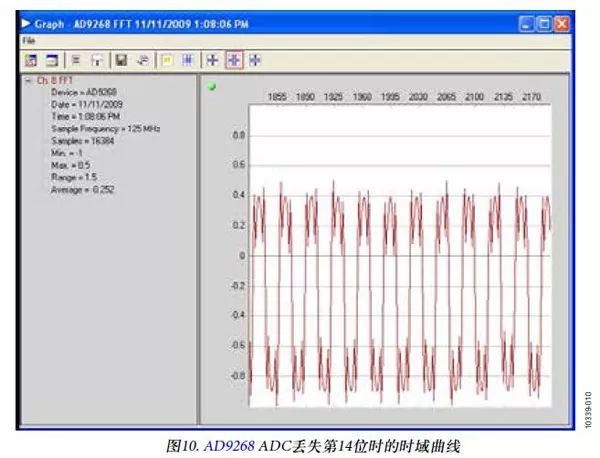

ADC丢失第14位时的时域曲线

图10为相同数据的时域曲线。它不是一个平滑的正弦波,数据发生偏移,波形中多个点处有明显的尖峰。

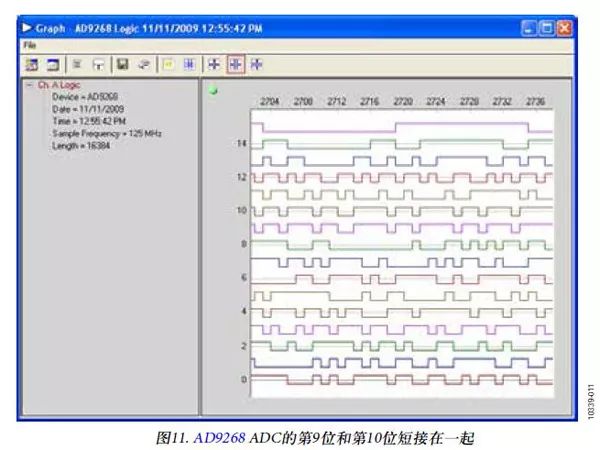

ADC的第9位和第10位短接在一起

图11所示不再是丢失一位的情况,而是两位短接在一起,因此对于这两个引脚,接收器始终接收到相同的数据。

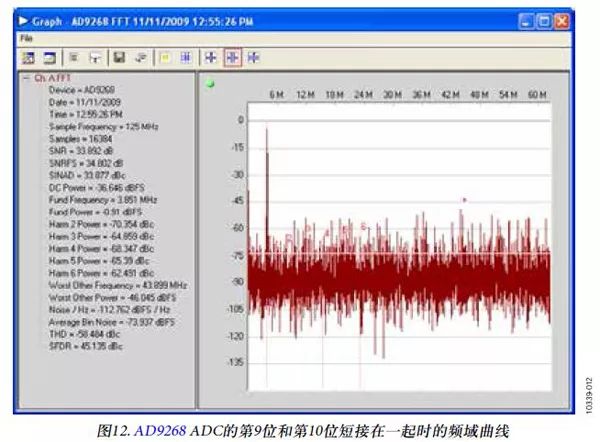

ADC第9位和第10位短接在一起时的频域曲线

图12显示了两位短接在一起时的频域视图。虽然基频音非常清楚,但噪底显著低于预期。噪底失真的程度取决于短接哪两位。

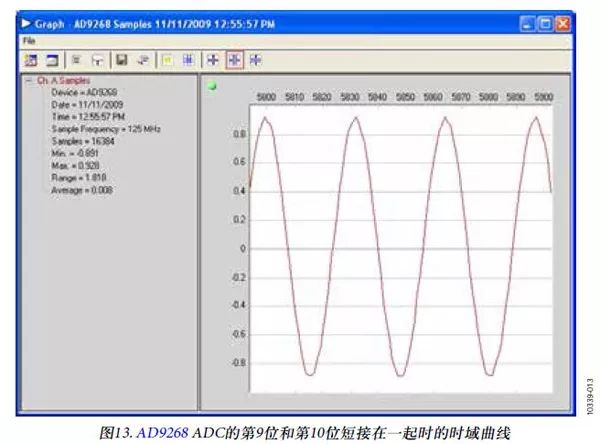

ADC第9位和第10位短接在一起时的时域曲线

在图13所示的时域图中,问题相对不明显。虽然在波峰和波谷处损失了一些平滑度,但当采样速率接近波形频率时,这是常见现象。

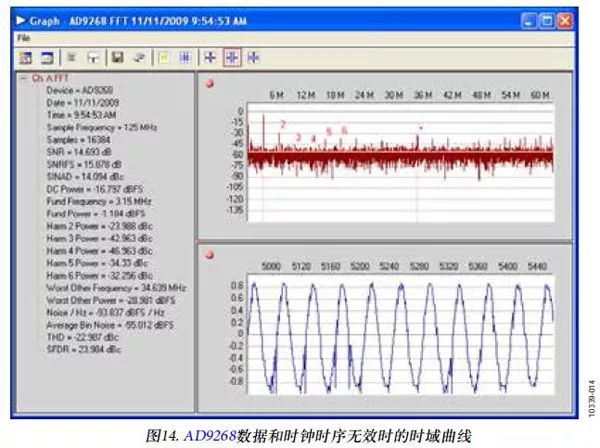

数据和时钟时序无效时的时域曲线

图14显示了一个因建立/保持问题而导致时序无效的转换器的情况。上述错误一般会在数据的每个周期中出现,而时序错误则不然,通常并不是持续存在。不太严重的时序错误可能是间歇性的。这些图显示了不符合时序要求的数据捕捉的时域和频域曲线。注意,各周期的时域错误并不一致。还应注意FFT/频域的噪底有所提高,这通常表示有一位丢失,原因可能是时序对齐错误。

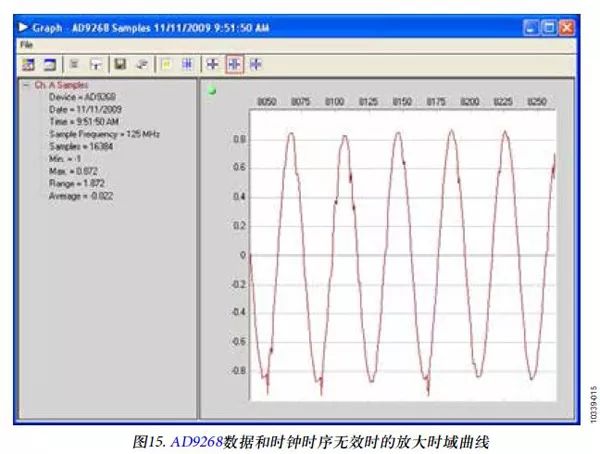

数据和时钟时序无效时的放大时域曲线

图15是图14所示时域时序误差的放大图。同样应注意,各周期的错误并不一致,但某些错误会重复。例如,该图中有多个周期的谷底上出现负尖峰。

-

FPGA

+关注

关注

1629文章

21736浏览量

603279 -

adc

+关注

关注

98文章

6498浏览量

544616

原文标题:FPGA与ADC数字数据输出的接口

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CTSD精密ADC—利用异步采样速率转换(ASRC)简化数字数据接口

FPGA与ADC数字输出的各种接口协议和标准

28335AD数据采集当ADC0为0V时DSP输出数字数据并不是0

JESD204B与LVDS接口并行 管线式ADC延迟问题分析及解答

FPGA与ADC数字数据输出的接口资料下载

具有LVDS输出的LTM9011 ADC的AN147-Altera Stratix IV FPGA接口

CTSD精密ADC:利用异步采样速率转换(ASRC)简化数字数据接口

FPGA与ADC数字数据输出接口的协议及标准

FPGA与ADC数字数据输出接口的协议及标准

评论