当我们为印刷电路板设计规划层配置时。尽管似乎更少的层意味着更低的成本,更多层会增加了成本,但这实际上并不是影响成本的全部因素。为了帮助您确定设计的平衡点,让我们看一下多层PCB堆叠计划中应考虑的一些细节。

计算多层PCB堆叠计划中的成本

一个简单明了的事实是,制造多层印刷电路板的基本成本将超过单面或双面板。通常,四层板的成本几乎是同尺寸单层或双层板的两倍。从那里开始,每增加一层,就会增加20%左右。但是,决定电路板总成本的不仅仅是层数。

为了确定电路板的总成本,您需要考虑许多其他问题:

l电路板的尺寸,形状和厚度。

l表面光洁度。

l铜重量。

l钻孔数量和不同的钻孔尺寸。

l电路密度。

所有的细节都需要考虑到,只有这样才能准确了解实际成本是多少。或许是为了在板上节省成本,您将增加钻孔数量和电路密度。但试图将更多的电路压入更少的层不一定是最佳选择,因为由于复杂性,它可能会增加设计和制造费用。

另一方面,在多层设计中坚持使用一定数量的层,而不是寻找减少层数的方法,最终也将使您花费更多。关键是要彻底分析需求,才能可以做出明智的决定。这也意味着在成本分析中还要考虑电路板的信号性能。

高速设计PCB堆叠注意事项

即使在最简单的设计上,PCB设计也随着越来越多的高速电路而不断发展。曾经与简单的单层或双层板配合使用的设计现在可能需要多层,以支持它们现在包含的高速电路。

在某些情况下,高速走线路由可能需要与其他走线隔离,以防止串扰。扩展路由以支持这种隔离可能需要在设计中添加其他路由层。

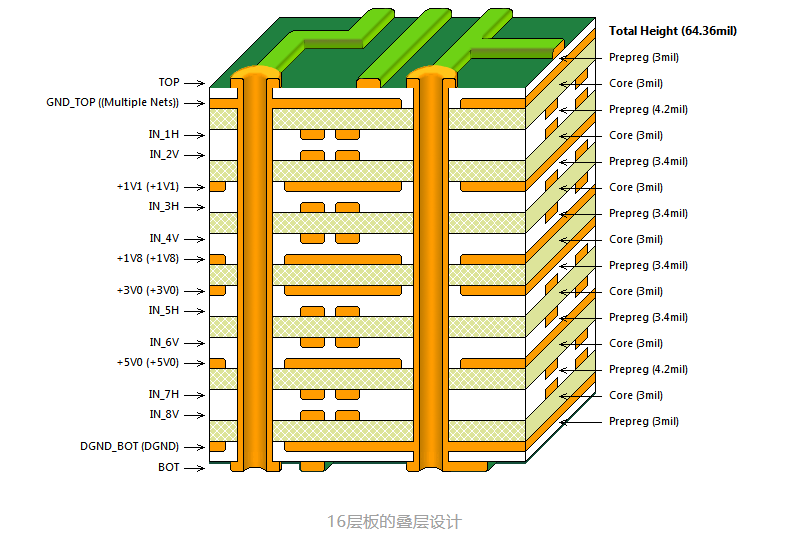

高速设计可能还需要非标准的电路板材料和特定的层厚度来进行阻抗控制的布线。为了适应带状线的布线要求,需要将信号层与高速传输线夹在两个接地层之间。

使用双带状线配置时,需要将两个相邻的信号层夹在一对接地层之间。如您所见,高速电路不仅需要额外的信号层来布线,而且还需要额外的电源层和接地层。

电源和接地层堆叠规划

当高速传输线在PCB的表面层上布线时,它们下方将需要一个坚固的接地层。这是微带路由配置,正如我们已经看到的,带状线路由要求信号路由层夹在两个接地层之间。

利用这些布线配置以及所有这些电路所需的不同电压,设计中电源层和接地层的数量最终可能会占据板层堆叠的主导地位。这是需要认真进行多层PCB堆叠计划的地方,以便仔细管理所需的层数。

有帮助的一件事是将多个电压组合到一个平面层上。分割电源平面或接地平面对于减少设计中所需的总板层数量很有帮助,但同时也会带来新的问题。最重要的是,避免在分开的接地面上布线高速走线。

如果您的路由要求在其下方有一个接地平面作为返回路径,则将该平面拆分成不同的电压会破坏返回路径,并可能导致各种信号完整性问题。这并不意味着您不应该使用拆分平面,只是在使用路由时要格外小心。

-

电路板设计

+关注

关注

1文章

127浏览量

16497 -

PCB设计

+关注

关注

394文章

4685浏览量

85573 -

PCB布线

+关注

关注

20文章

463浏览量

42053 -

华秋DFM

+关注

关注

20文章

3494浏览量

4495

发布评论请先 登录

相关推荐

使用瑞萨AnalogPAK SLG47001/03节省开发时间

快充电线:高效充电体验的必备神器

DNP3设备数据 转 CCLink IE Field Basic项目案例

iec61850设备数据 转 CCLink IE Field Basic项目案例

opc ua设备数据 转 CCLink IE Field Basic项目案例

电力IEC104设备数据 转 CCLink IE Field Basic项目案例

PCB多层板为什么都是偶数层?奇数层不行吗?

请问一下CMake和Make之间的区别有哪些?

PCB叠层设计优化ESD性能设计

多层PCB叠层细节规划:节省时间和成本的最佳选择

多层PCB叠层细节规划:节省时间和成本的最佳选择

评论