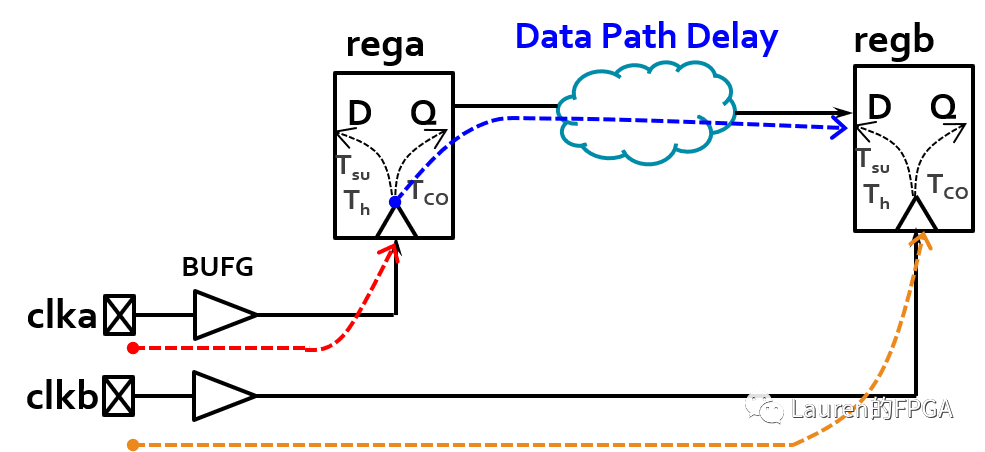

更为具体的时序报告信息如何从中获取,或者如何根据时序报告发现导致时序违例的潜在原因呢? 首先,我们要了解时序路径的构成,如下图所示。不难看出,对于一条典型的触发器+组合逻辑+触发器的时序路径,它由三部分组成:源时钟路径(发送时钟路径)、数据路径和目的时钟路径(接收时钟路径)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时序

+关注

关注

5文章

387浏览量

37330

原文标题:如何阅读时序报告

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA威廉希尔官方网站 驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一文详解信号的回流路径

最近在看JT大佬出的一本高速PCB设计书籍,看到回流路径这里,让我想到最近两个群里都提到关于这个知识点的问题。书籍很好,但是也会有一些疑问,带着这些疑问我也查找了相关资料,我想着尽可能的结合书中知识以及自己的理解,把这个问题能给

干货满满!一文了解AGV软件系统的构成

AGV系统由调度、车载控制、导航导引三部分构成,实现物流自动化智能化。调度系统分配任务,车载系统控制导航装卸,导航导引确保精确行驶。AGV采用双控系统,提高适应性,用户可实时查看运行状态。

时序逻辑电路中如何判断有效状态和无效状态

在时序逻辑电路中,有效状态和无效状态的判断是电路分析和设计的重要环节。有效状态是指电路在实际工作过程中被利用到的状态,它们构成了电路的有效循环;而无效状态则是指那些没有被利用到,或者虽然存在但不影响电路正常工作的状态。以下是对如何判断时

电源时序器的原理及使用方法是什么

电源时序器是一种用于控制多个电源设备按照一定顺序开启或关闭的电子设备。它广泛应用于音响、舞台灯光、电视广播、工业自动化等领域。本文将介绍电源时序器的原理及使用方法。

FPGA 高级设计:时序分析和收敛

结果当然是要求系统时序满足设计者提出的要求。

下面举一个最简单的例子来说明时序分析的基本概念。

假设信号需要从输入到输出在FPGA 内部经过一些逻辑延时和

发表于 06-17 17:07

TDK最新xEV解决方案,一文全知道!

TDK最新xEV解决方案,一文全知道! TDK致力于为各类xEV提供广泛的产品组合,进而推动未来汽车的发展。 TDK在汽车行业中发挥着至关重要的作用,尤其是在电动汽车时代,从先进的电力电子器件

求助,求大神帮忙解答下AN65974同步Slave FIFO的读时序

你好,在AN65974文档中,我看不懂同步Slave FIFO的读时序,你可以给我解读一下么? 下图中有我标注的我不懂的问题。非常感谢你!......

发表于 05-31 06:27

Xilinx FPGA编程技巧之常用时序约束详解

Register-to-Register Constraint

寄存器到寄存器约束往往指的是周期约束,周期约束的覆盖范围包括:

覆盖了时钟域的时序要求

覆盖了同步数据在内部寄存器之间的传输

分析一个单独的时钟域内的路径

分

发表于 05-06 15:51

FPGA工程的时序约束实践案例

详细的原时钟时序、数据路径时序、目标时钟时序的各延迟数据如下图所示。值得注意的是数据路径信息,其中包括Tco延迟和布线延迟,各级累加之后得到

发表于 04-29 10:39

•764次阅读

Xilinx FPGA编程技巧之常用时序约束详解

寄存器到寄存器约束往往指的是周期约束,周期约束的覆盖范围包括:

覆盖了时钟域的时序要求

覆盖了同步数据在内部寄存器之间的传输

分析一个单独的时钟域内的路径

分析相关时钟域间的所有路径

发表于 04-12 17:39

时序逻辑电路输出与什么有关 时序逻辑电路由哪两部分组成

组成:组合逻辑电路和时钟电路。组合逻辑电路是一种基本的逻辑电路,其输出仅仅取决于当前的输入信号,与时间无关。组合逻辑电路由门电路(如与门、或门、非门等)组成,通过门的组合和连接构成了复杂的逻辑功能。时序逻辑电路将

时序电路的分类 时序电路的基本单元电路有哪些

时序电路是一种能够按照特定的顺序进行操作的电路。它以时钟信号为基准,根据输入信号的状态和过去的状态来确定输出信号的状态。时序电路广泛应用于计算机、通信系统、数字信号处理等领域。根据不同的分类标准

FPGA设计的常用基本时序路径分析

该条路径包括了触发器内部clock-to-Q的延迟,触发器之间的由组合逻辑造成的路径延迟以及目标触发器的建立时间,其延时是数据从源触发器开始,在下一个时钟沿来到之前通过组合逻辑和布线的最大时间

一文知道时序路径的构成

一文知道时序路径的构成

评论