在我与客户交流时,常被问到这个问题。也许措辞并非完全如此,但大致是下面这样:“为什么我要升级到 VersalACAP?现在是时候这样做了吗?” 这是一个很好的问题,而且答案也很简单,那就是——“具体情况具体分析”。 好吧,也许这样的答案根本不简单!公正地说,有诸多因素需要考虑,包括设计要求/资源、设计能在多大程度上利用 Versal ACAP 中数量庞大的硬 IP、库和软 IP 可用性、芯片可用性、生产时限等。 因此,具体答案确实会随着相关因素的变化而发生改变。我们将在今后的博文中探讨这些主题,但今天,我想把重点放在“为什么升级到 Versal”这个问题上并提供具体的客户示例。

认识到所有硬 IP 的价值

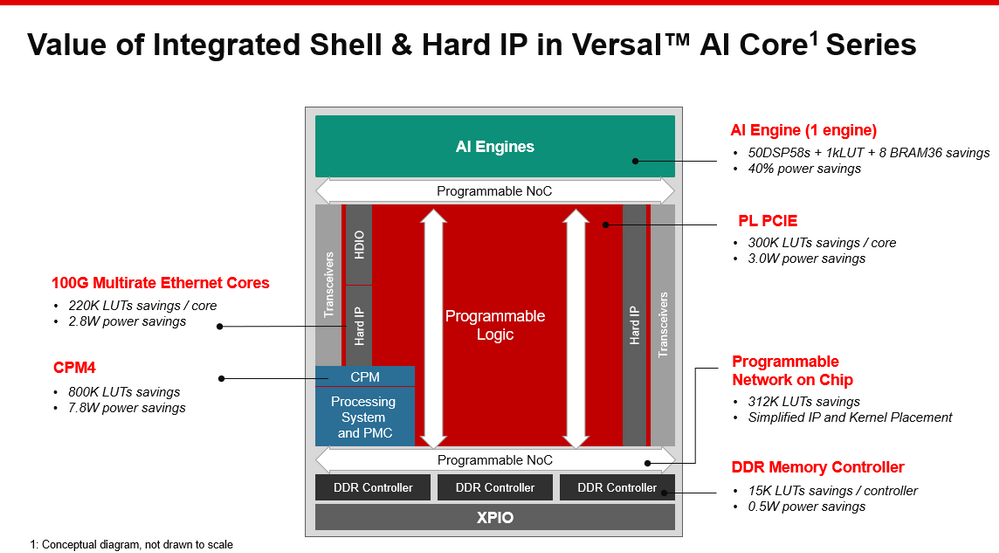

在探讨为什么要升级到 Versal ACAP 时,必须首先认识到所有硬 IP 的价值,包括存储控制器、PCIe、多速率以太网和片上可编程网络( NoC )等常用基础设施的价值,它可以减少对灵活应变的引擎或可编程逻辑的路由需求。

一些 Versal 系列还包含 AI引擎(一种非常适合高级信号处理和 ML 算法的新型矢量处理器)、高带宽存储器、直接 RF 和高速密钥。赛灵思将这些 IP 全部硬化的主要原因之一在于,赛灵思在多年前就意识到摩尔定律即将走向终点,仅靠缩小晶体管难以为客户在每个新的工艺节点上提供他们所期待的性能提升和功耗下降。

下图所示的是 Versal AI Core 系列器件中硬 IP 的价值。可以看出,与我们大获成功的 16nm UltraScale+产品相比,它拥有 LUT 占用大幅降低、功耗显著下降等多项优势。在 Versal AI Core VC1902 器件中,有望省下多达 360 万个 LUT。 当然,大多数设计并不能用到所有硬 IP ,但如果将一个类似设计移植到 Versal ACAP,就会看到 LUT 占用和功耗的实质性降低,而且还可以提供布局布线速度加快、日设计迭代次数增加等附加优势。

Versal AI Core 系列中集成外壳程序和硬 IP 的价值 借助 AI 引擎实现高级信号处理 今天我还想重点讲解一下 AI 引擎。AI 引擎由数十个到数百个(在最大型的 AI Core 系列器件 VC1902 中多达 400 个)专为线性代数和矩阵数学等数学功能优化的小型 VLIW SIMD 矢量处理器阵列构成。当人们听到“AI 引擎”一词时,往往会自然而然地想到人工智能。 然而,这些功能只是众多高级信号处理算法(如波束成型和大规模 MIMO )和机器学习推断算法(如用于图像分类的卷积神经网络( CNN ))的基本构建块。有鉴于这一原因,无论是信号处理还是推断,AI 引擎都能分别提供复数数据和实数数据支持。

AI 引擎的关键目标应用之一是 5G 无线系统信号处理。针对一个支持 200MHz 瞬时带宽 2 的 64 天线系统的波束成型威廉希尔官方网站 ,AI 引擎可为其提供 5 倍的计算密度并降低 50% 的功耗。这也引起了领先的 5G 测试测量设备提供商 Keysight 的关注。

此外,他们也十分注重开发生产力。诚然,他们拥有负责灵活应变的引擎硬件编程的专家,但是相比硬件布局布线需要耗费数个小时, AI 引擎的编译用时仅需要几分钟,这样一来,他们的 5G 无线算法的设计与开发生产力就会显著提高,每星期便能多完成几次设计迭代。

然而,从他们的实现方案原理图可以看出(参见下图),Versal ACAP 的系统级价值可谓是决定性的,因为他们能将 AI 引擎的功耗及生产力与灵活应变的引擎的灵活性相结合,创建出令人叹服的 EVM 演示。

点击查看大图 EVM 测量 Tx/Rx 性能及其 IQ 级联分析 这仅仅是客户采用 Versal ACAP 架构(特别是 AI 引擎)从而获得重大效益的示例之一。还有众多其他客户在 VC1902 上为 AI 引擎编程,用于 5G、数据中心推断、边缘推断原型设计、雷达、线缆接入等众多应用。

-

引擎

+关注

关注

1文章

361浏览量

22548 -

存储控制器

+关注

关注

0文章

23浏览量

9147 -

Versal

+关注

关注

1文章

158浏览量

7658

原文标题:是否采用 Versal?这是个问题……

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

为什么我要升级到Versal ACAP?

为什么我要升级到Versal ACAP?

评论