简介

UART核提供了一个Avalon存储器映射(Avalon-MM)的接口,这个接口使得Avalon-MM的主要周边设备(例如Nios II处理器)通过读和写数据、控制寄存器,就能实现和UART核通信的任务。所以在简介部分,我们会对常用的寄存器进行详细的介绍。

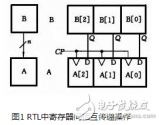

上图为一个典型系统中的UART核,它有两个用户可见的部分:

l可通过Avalon-MM从接口访问的寄存器

lRXD, TXD, CTS, and RTS等RS-232接口信号

图中可以看到,在RXD端口与rxdata寄存器之间、TXD与txdata寄存器之间存在着移位寄存器。在Qsys,我们只讲解UART核的工作原理,以及该核的使用方法。前面提到,我们是通过读、写相关的寄存器,实现的串口通信功能。那么接下来,我们将讲解主要的寄存器——状态寄存器、控制寄存器、数据寄存器。其中状态、控制寄存器与配置IRQ(中断请求)相关。

寄存器相关简介

下图为UART核的寄存器信息表,其中数据寄存器(rxdata、txdata)、状态寄存器(status)、控制寄存器(control)是重点,括号部分的注释内容在表的下部。

(1)这些位可能不存在,取决于数据位宽的硬件选项。如果它们不存在,读出的值为0。且如果对它们进行写操作,则没有意义。

(2)给status(状态)寄存器写0将清零dcts, e, toe, roe, brk, fe, and pe等位。

(3)这些寄存器可能不存在,取决于硬件配置选项。如果寄存器不存在,对它进行读操作会返回未定义的值,且进行写操作则无意义。

rxdata寄存器

rxdata寄存器用于存储RXD输入引脚接收的数据。当一个新的数据被RXD输入引脚完全接受后,会被传输并存储到rxdata寄存器,此时status寄存器(状态寄存器)的rrdy位会被置1。当rxdata寄存器中的值被读了之后,status寄存器中的rrdy位会被清零。当rrdy位为1时,又有一个新的字符传输给rxdata寄存器,则会产生溢出错误,状态寄存器的ROE位被置1。不管前一个字符是否被读出,新接收到的字符总是会被自动保存到rxdata寄存器。另外,对rxdata寄存器进行写操作无意义。

txdata寄存器

Avalon主控制器把要发送的字符写入到txdata寄存器中。当一个字符写入txdata寄存时,状态寄存器(status寄存器)的TRDY位会被置0;当字符从txdata寄存器传输到发送移位寄存器时,状态寄存器(status寄存器)的TRDY位被置为1。当TRDY位为0时,将字符写入txdata寄存器的结果是未定义的。读txdata返回未定义的值。

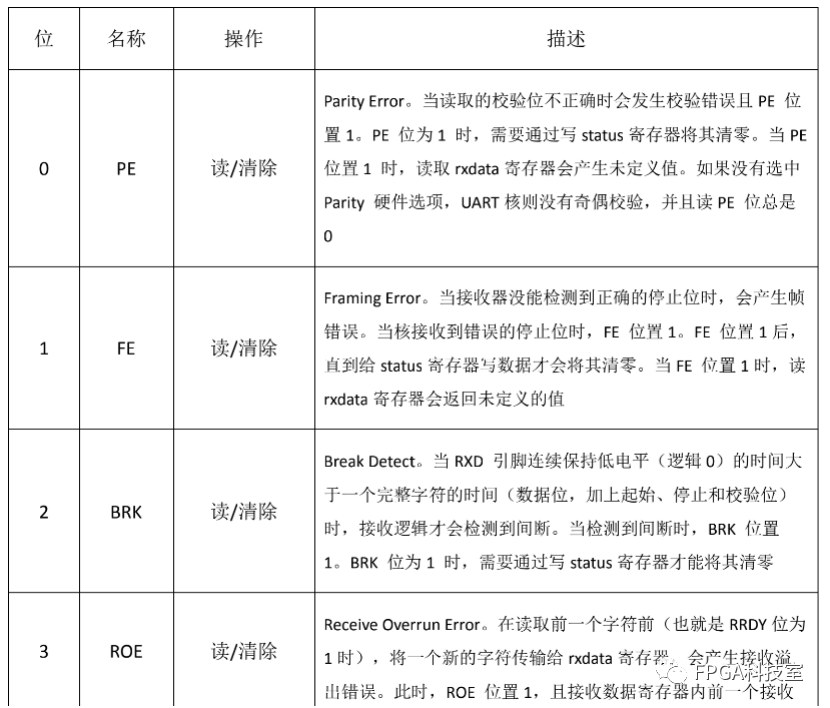

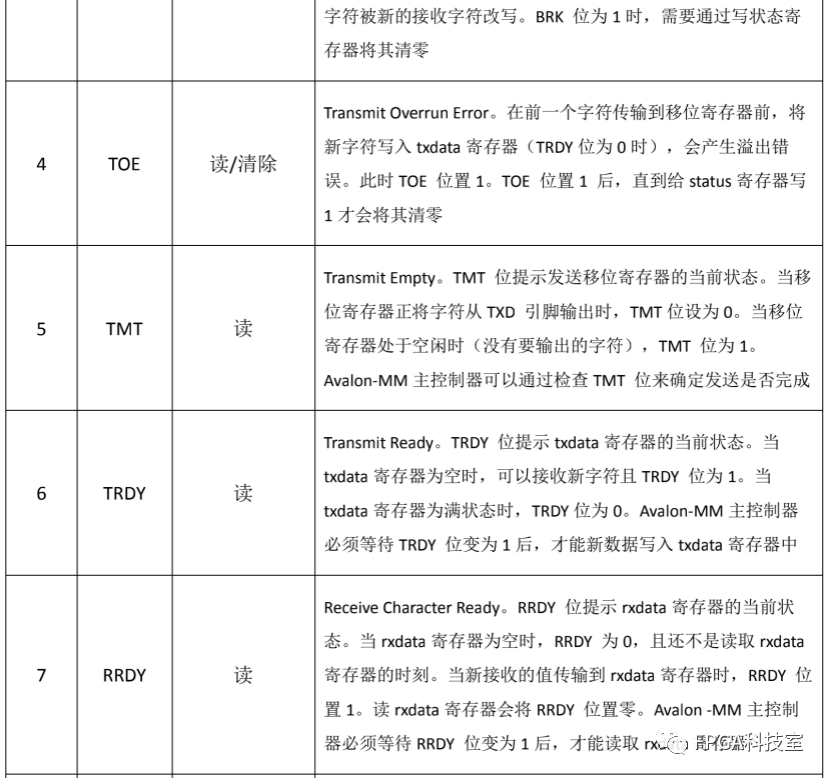

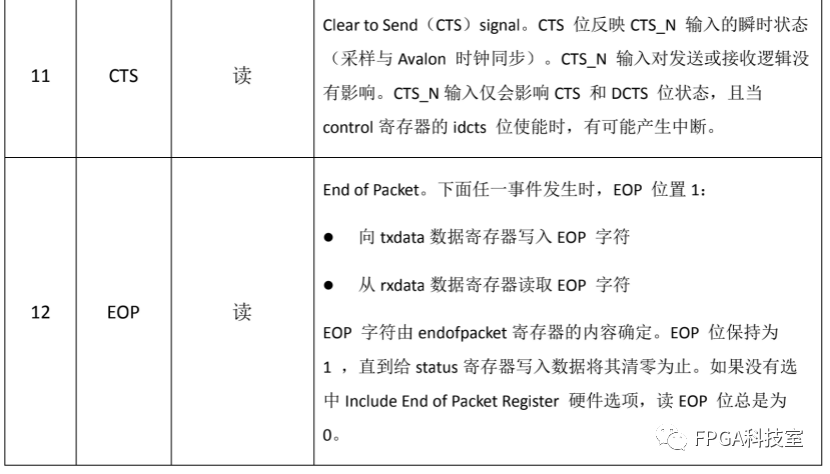

status寄存器(状态寄存器)

状态寄存器(status寄存器)由可以反应UART核状态情况的独立位组成。每个状态位和对应的控制寄存器中,能使能中断的位相联系。任何时候都可以读取状态寄存器。且读操作不会改变寄存器任何位的值。给状态寄存器写0,会清零DCTS、E、TOE、ROE、BRK、FE和PE位。状态寄存器的位相关信息在下表中列出:

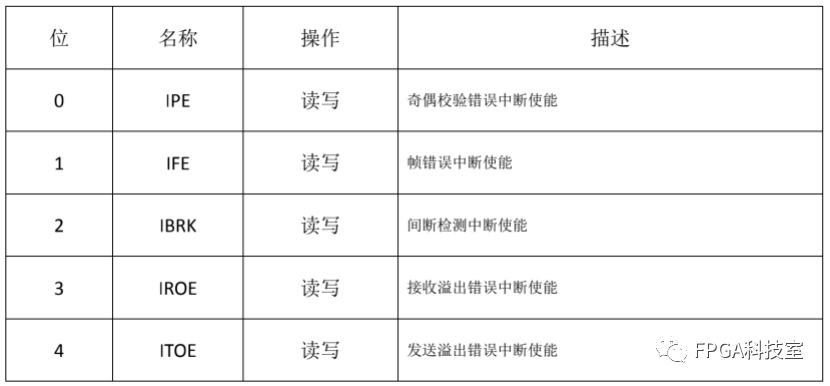

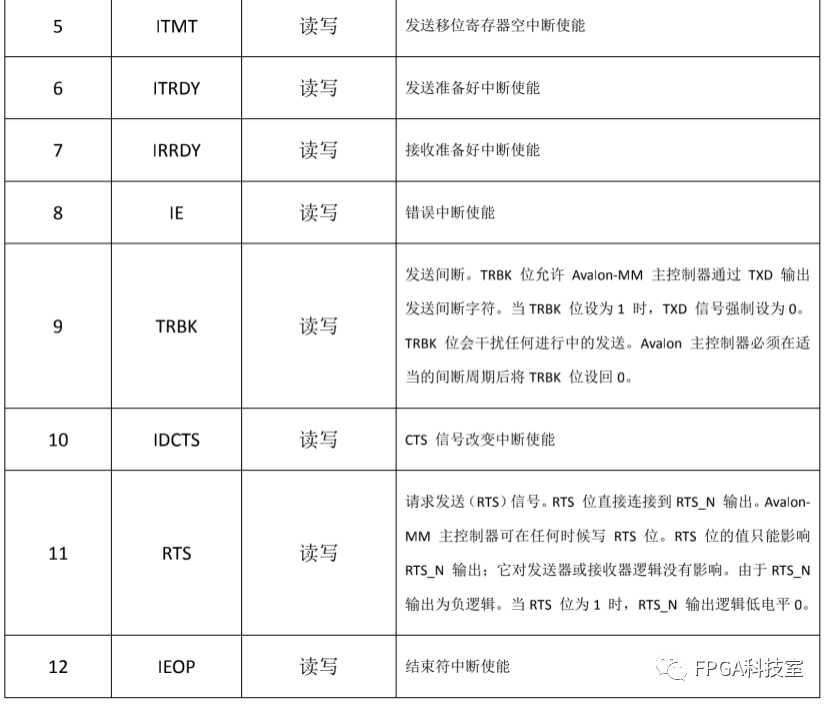

Control寄存器(控制寄存器)

控制寄存器由独立的各个位构成,每个位控制UART核操作的一个方面。我们在任何时间都可以读控制寄存器。每一个控制寄存器中与状态寄存器对应的位,都可以使能一个IRQ。当控制寄存器中与状态寄存器对应的位的值都为1时,就会触发一个IRQ。

divisor寄存器(可选)

divisor寄存器中的值是用来产生波特率时钟的。有效的波特率由这个公式决定:

波特率=(时钟频率)/(divisor+1)

divisor寄存器是一种可选的硬件功能。如果没有使能Baud Rate Can Be Changed By Software(波特率能被软件改变)这个选项,将不存在divisor寄存器。这种情况下,写divisor寄存器没有作用,读它返回一个未定义的值。

endofpacket寄存器(可选)

endofpacket寄存器中的值决定了可变长度DMA传输的结束字符。复位后,默认值是0,是ASCII码中的空值字符(�)。endofpacket寄存器是一种可选的硬件功能。如果没有使能Include end-of-packet register这个选项,将不存在endofpacket寄存器。这种情况下,写endofpacket寄存器没有作用,读它返回一个未定义的值。

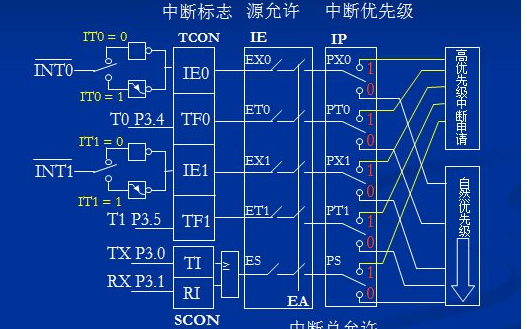

中断操作

UART核输出一个单独的IRQ信号给Avalon-MM接口。而Avalon-MM接口能连到系统中的任意一个主设备,例如Nios II处理器。主设备在对status寄存器进行读操作之后,才能确定中断产生的原因。每一个中断在status寄存器有相应的位,并在control寄存器中有一个使能位。当一个中断发生时,相关的status位置1,直到它被回应了(acknowledged)。当任意一个status位置1,且相应的中断使能位是1时触发IRQ。一个主设备可以通过清零status寄存器来回应(acknowledge)IRQ。复位的时候,所有的中断使能位置0。因此,核无法触发IRQ,直到主设备使一个或多个中断使能位置1。

这里总结一下:一个可以触发的中断与它相应的status和control(中断使能)位有关。

硬件配置内容

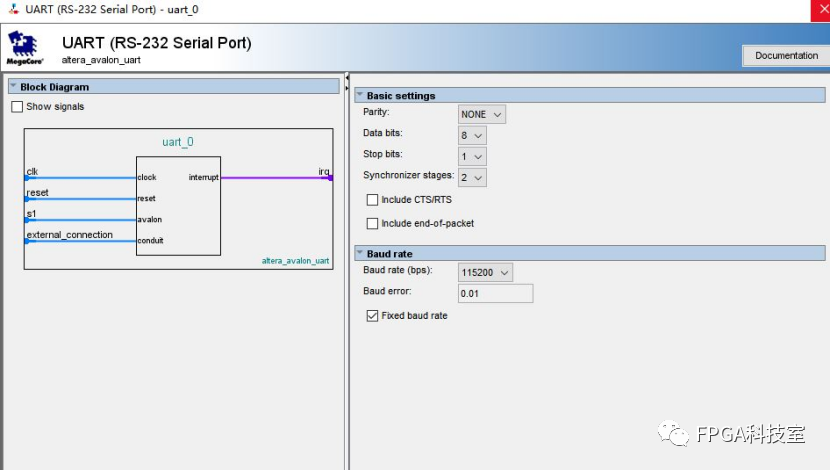

如图为UART核的配置界面:

UART核有Basic settings(基础设置)和Baud rate(波特率)这两个可以设置的部分。

1.Parity(奇偶校验)

Partity一栏有None(无)、Even(偶)、Odd(奇)这三个选项。这个设置用来确定UART是否发送有奇偶校验的字符,以及它是否期望接收到的有奇偶校验的字符。当Parity设为None时,发送逻辑发送不包含校验位的数据,且接收逻辑设定接收到的数据也不包含校验位。status寄存器中的PE(校验错误)位无效,其数值始终为0。当Parity设为Odd或Even时,发送逻辑计算并插入所需的校验位到将要输出的TXD数据流,且接收逻辑检验接收到的RXD位流中的校验位。如果接收器发现结果不正确,则status寄存器中的PE位会被置1.当Parity设置为Even(偶)时,字符中有偶数个1,则校验位为0;同样,当Parity设为Odd时,若字符中有奇数个1,则校验位为0。

2.Data bits(数据位)

Data bits一栏有7、8、9这三个可以设置的选项。这个设置决定txdata、rxdata、endofpacket这三个寄存器的位宽。

3. Stop bits(停止位)

Stop bits一栏有7、8、9这三个可以设置的选项。这个设置决定了核在传输每一个字符时,是有1还是2个停止位。UART核总是在接收到第一个停止位的时候,就停止接收操作,忽略掉附带的停止位,无论什么设置。

4. Synchronizer Stages

这个设置与寄存器的长度以及亚稳态事件相关,这里一般使用默认设置即可。

5. Include CTS/RTS

选择是否使用串口的“流控”功能,一般很少使用。

6. Include end-of-packet

选择是否设置数据流的结束标志(end-of-packet),一般很少使用。

7. Baud Rate(波特率设置)

UART内核可实现RS-232标准中的任意波特率。波特率可配置为以下方式中的一种:

l固定的波特率——波特率在系统生成时被确定,且不能通过Avalon从控制器端口改变它的值。

l可变的波特率——基于divisor寄存器中存储的时钟分频值,波特率是可变的。主控制器通过向divisor寄存器中写入新值来改变波特率。

波特率的计算依赖于Avalon-MM接口提供的时钟频率。在硬件改变系统时钟频率,却没有重新生成UART核会导致错误的信号。

Baud Rate设置决定了复位后的波特率。Baud Rate选项提供了标准的预设值。也允许用户输入任何非标准波特率。为了实现所需要的波特率,通常根据波特率计算时钟分频系数。

波特率与分频系数的关系如下:

除数=int((时钟频率)/(波特率)+ 0.5)

波特率=(时钟频率)/(除数+ 1)

当选择Fixed baud rate 时,UART 硬件中不再包括divisor寄存器。UART 硬件使用固定的波特率分频系数,且在系统生成后无法改变。这种情况下向地址偏移值4的地方写数据无作用,且读地址偏移值4的地址返回未定义的结果。当不选择Fixed baud rate 时,硬件中会在地址偏移值4生成一个16 位的divisor寄存器。divisor寄存器是可写的,所以可以通过向分频寄存器写入新值来改变波特率。

-

寄存器

+关注

关注

31文章

5336浏览量

120256 -

中断

+关注

关注

5文章

898浏览量

41474 -

uart

+关注

关注

22文章

1235浏览量

101358

原文标题:NIOS II处理器系统设计之异步收发传输UART(理论部分)

文章出处:【微信号:fpgaerZT,微信公众号:FPGA科技室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

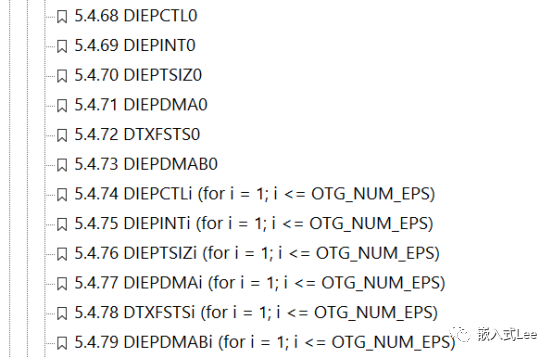

基于DWC2的USB驱动开发-发送相关的寄存器DMA寄存器详解

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途

Zynq uart软件中断hook的操作过程

ATMEL SAMC21的UART驱动寄存器操作和程序免费下载

UART寄存器介绍与中断操作详解(应用部分)

STM32的寄存器操作

UART寄存器介绍与中断操作详解

UART寄存器介绍与中断操作详解

评论