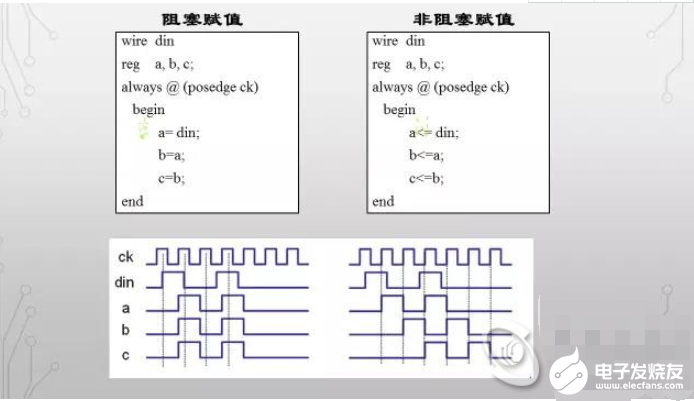

阻塞赋值对应的电路往往与触发沿没有关系,只与输入电平的变化有关系。

非阻塞赋值对应的电路结构往往与触发沿有关系,只有在触发沿时才有可能发生赋值的情况。

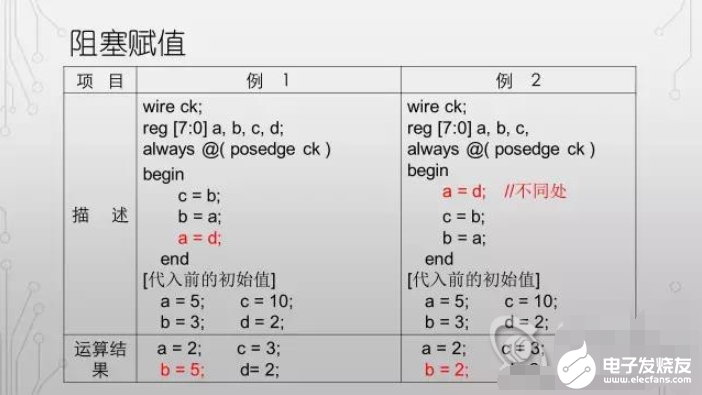

1、阻塞赋值操作符用等号(即 = )表示。“阻塞”是指在进程语句(initial和always)中,当前的赋值语句阻断了其后的语句,也就是说后面的语句必须等到当前的赋值语句执行完毕才能执行。而且阻塞赋值可以看成是一步完成的,即:计算等号右边的值并同时赋给左边变量。例如:

当执行“x=next_x;”时,x会立即的到next_x的值。而下一句“y=x;”必须等到“x=next_x;”执行完毕才能被执行。由于这两条语句都没有延迟(相当于导线),导致他们的等价语句为“y=next_x;”。

赋值是实时的,计算完右面的马上赋值给左边的,然后再执行下一句,操作时串行的,且在一个alway内完成。

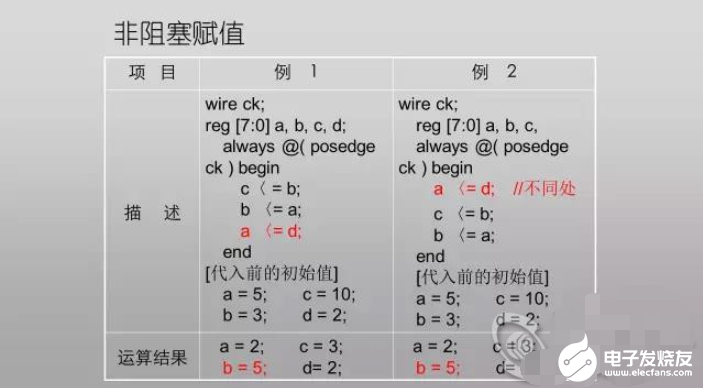

2、非阻塞赋值操作符用小于等于号 (即 《= )表示。“非阻塞”是指在进程语句(initial和always)中,当前的赋值语句不会阻断其后的语句。非阻塞语句可以认为是分为两个步骤进行的:

①计算等号右边的表达式的值,(我的理解是:在进入进程后,所有的非阻塞语句的右端表达式同时计算,赋值动作只发生在顺序执行到当前非阻塞语句那一刻)。

②在本条赋值语句结束时,将等号右边的值赋给等号左边的变量。

例如:

当执行“x《=next_x;”时,并不会阻断语句“y《=x;”的执行。因此,语句“y《=x;”中的x的值与语句“x《=next_x;”中的x的值不同:语句“y《=x;”中的x是第一个D触发器的初值(Q0)。而语句“x《=next_x;”中的x的值是D触发器经过一个同步脉冲后的输出值(Q1)。基于此这个进程产生了与阻塞赋值进程截然不同的结果,即:产生了移位寄存器的效果。

简单理解就是,阻塞赋值是按需执行,非阻塞赋值是并行执行。

为了更好地理解上述要点,我们需要对Verilog 语言中的阻塞赋值和非阻塞赋值的功能和执行时间上的差别有深入的了解。为了解释问题方便下面定义两个缩写字:

RHS – 方程式右手方向的表达式或变量可分别缩写为:RHS表达式或RHS变量。LHS – 方程式左手方向的表达式或变量可分别缩写为:LHS表达式或LHS变量。

IEEE Verilog标准定义了有些语句有确定的执行时间,有些语句没有确定的执行时间。若有两条或两条以上语句准备在同一时刻执行,但由于语句的排列次序不同(而这种排列次序的不同是IEEE Verilog标准所允许的), 却产生了不同的输出结果。这就是造成Verilog模块冒险和竞争现象的原因。为了避免产生竞争,理解阻塞和非阻塞赋值在执行时间上的差别是至关重要的。

-

Verilog

+关注

关注

28文章

1351浏览量

110077 -

阻塞赋值

+关注

关注

0文章

9浏览量

9157 -

非阻塞赋值

+关注

关注

0文章

10浏览量

9999

发布评论请先 登录

相关推荐

Verilog语言中阻塞和非阻塞赋值的不同

Verilog中阻塞赋值和非阻塞赋值的正确使用

verilog中阻塞赋值和非阻塞赋值

verilog中阻塞赋值和非阻塞赋值到底有什么区别

IEEE Verilog阻塞赋值和非阻塞赋值的区别

IEEE Verilog阻塞赋值和非阻塞赋值的区别

评论