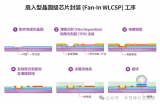

CES 2020大展上Intel首次公开了下一代移动平台Tiger Lake(或将命名为十一代酷睿)的部分细节,采用10nm+工艺,集成新的Willow Cove CPU核心、Xe LP GPU核心,IPC性能提升超过两位数,同时大大增强AI性能。

在会后的内部展示上,Intel首次拿出了Tiger Lake的晶圆供大家鉴赏。

事实上,Intel虽然官方称Tiger Lake使用的10nm是增强版10nm+,但严格来说将会是第三代(10nm++)。

在此之前,第一代10nm工艺的Cannonn Lake因为完全不合格而胎死腹中,只留下一颗双核心而且无核显的i3-8121U。目前的Ice Lake使用的已经是第二代(10nm+),频率仍然不过关,最高只能做到4.1GHz。

在工艺不达标的情况下,Ice Lake、Tiger Lake都只会出现在U/Y系列低功耗移动平台上,还有服务器。

从晶圆上可以清楚地看到Tiger Lake的内核,包括四个CPU核心(左侧上方和下方)、GPU核心(右侧)等,根据测量核心面积是13.64×10.71=146.10平方毫米,相比于11.44×10.71=122.52平方毫米的Ice Lake增大了约20%,其中宽度不变,长度增加2.2毫米。

增大的部分主要来自GPU核显,架构升级,执行单元也从64个增至96个。

搭载Tiger Lake的Intel史上最迷你主板

责任编辑:wv

-

晶圆

+关注

关注

52文章

4903浏览量

127958 -

intel

+关注

关注

19文章

3482浏览量

185960

发布评论请先 登录

相关推荐

硅晶圆的制备流程

PC应用中 Tiger Lake处理器的非隔离式负载点解决方案

无意发展至10nm以下,第二梯队晶圆代工厂的成熟工艺现状

晶圆级封装的五项基本工艺

Intel首次亮相Tiger Lake晶圆 基于增强版10nm+工艺

Intel首次亮相Tiger Lake晶圆 基于增强版10nm+工艺

评论