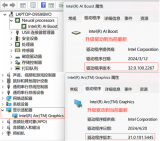

12月2日消息 根据WCCFTECH的报道,早在Skylake微架构发布时,英特尔就开始在HEDT系列处理器中调整其CPU的缓存结构。现在根据Geekbench的说法,英特尔即将发布的10nm Tiger Lake移动处理器也将进行类似的缓存结构调整。

据介绍,在Skylake-X的HEDT处理器中,英特尔减少了L3缓存而增加了低延迟的L2缓存。在Tiger Lake-Y系列处理器中,英特尔可能会在L1、L2和L3缓存上带来全面改进。以前,移动和桌面CPU采用的是相同的缓存结构,但是通过重新设计缓存,英特尔计划提高移动CPU的效率。

根据Geekbench的数据,Tiger Lake-Y 有4个核心和8个线程。该芯片的特点是大大改变了缓存结构,每个核心拥有1,280KB的L2缓存,L2缓存总量达到了5,120KB,相比前代实现了400%的提升,除此之外L3高速缓存也总共增加了12MB。

在L1高速缓存方面,英特尔已经将L1指令高速缓存的大小提高到了48KB,但是L1数据高速缓存仍然是32KB。外媒预测,Tiger Lake有望带来PCIe 4.0新特性和Intel Xe 核显。

-

英特尔

+关注

关注

61文章

9953浏览量

171704 -

cpu

+关注

关注

68文章

10855浏览量

211609

发布评论请先 登录

相关推荐

英特尔Panther Lake处理器或将2025年下半年亮相

英特尔Panther Lake处理器内部制造比例提升至70%

英特尔基于Intel 18A制程节点处理器样片成功出厂

英特尔发布新一代Lunar Lake处理器

英特尔Lunar Lake处理器即将上市

Arrow Lake-S英特尔处理器规格曝光,共计16款125W及65W产品

英特尔暂缓Arrow Lake处理器发布,AMD Zen 5处理器或将提前上市

英特尔Arrow Lake处理器更名酷睿Ultra

Cirrus Logic与英特尔和微软在全新的PC参考设计上进行合作

德国法院裁定英特尔芯片禁售,供应链面临影响

英特尔和AMD处理器的区别和特点

探索Qotom OPS嵌入式工业迷你电脑——英特尔第10代 Comet Lake 处理器搭载的小巧利器

英特尔Tiger Lake处理器缓存结构将调整

英特尔Tiger Lake处理器缓存结构将调整

评论