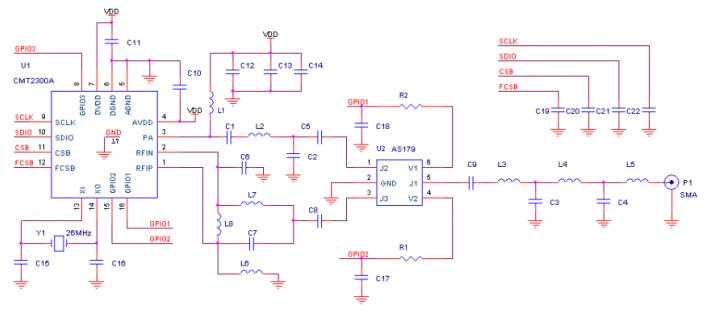

通常,在设计射频匹配网络时,需要兼顾几个方面:端口的阻抗匹配必须一致,插入损耗尽可能小,带外衰减尽可能大,PA功率与效率尽可能高,元件个数尽可能少。针对CMT2300A射频匹配网络设计,有DirectTie和SwitchType两种匹配方法。

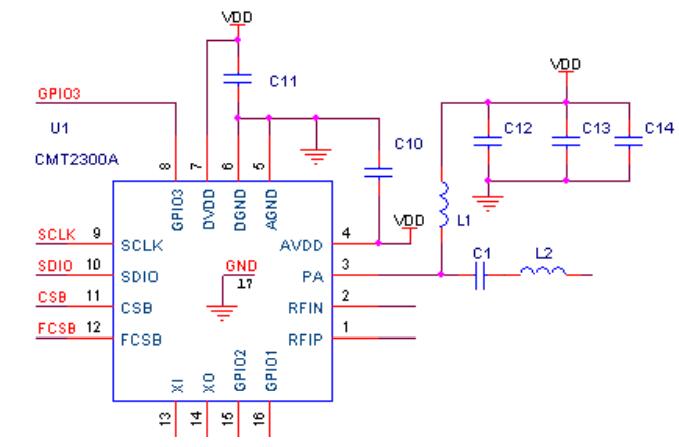

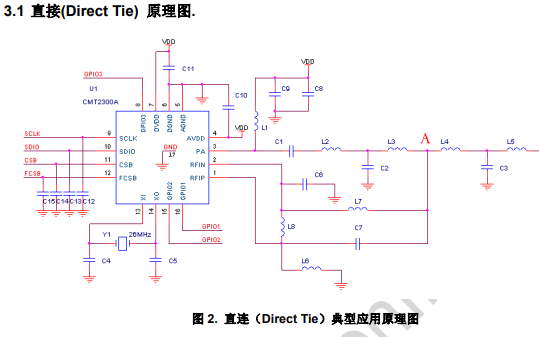

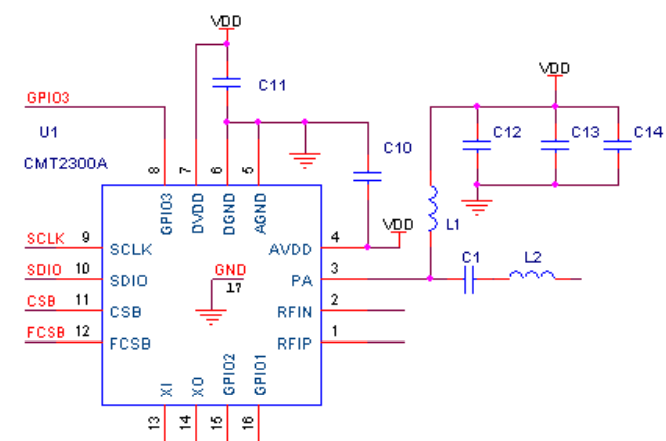

直连(DirectTie)匹配电路无需RF开关,TX和RX通路阻抗变换后直连到天线。CMOSTEKDirectTie匹配优化了电路结构,采用较少的元器件,既可满足CE/FCC规范,又实现高接收灵敏度,高效率和大功率输出。

1、L1是扼流电感。

2、C8-C11是电源退耦电容,用于减少PA输出对电源的影响。根据实际的应用需求要做适当调整。

3、C1是隔直电容,并且与L2的部分电感在工作频点形成谐振起到谐波抑制作用。

4、上图标识的A点为直连点,该点的阻抗是50Ω。

5、L2,C2和L3组成TX匹配网络,实现PA输出和直连点阻抗匹配。

6、C6,L6,C7,L7,L8组成RX巴伦匹配网络,实现接收机的输入阻抗和直连点匹配,并使得接收信号到达差分输入口RFIP,RFIN处时幅度相等,相位相差180度。

7、L4,C3,L5为50Ω到50Ω的T型低通滤波匹配网络。

8、Y1推荐用频率容差±20ppm的26MHz晶体,可接受的晶体频率容差取决于用户产品通讯系统的要求,如频率,信道,带宽等。

9、C4,C5为晶体负载电容(注意芯片内部已经集成了约4pF的负载电容,以CL=15pF的26MHz晶体为例,折合晶体相连走线分布电容2pF,C4和C5取值约15*2-4-2=24pF)。

10、C12-C15滤波电容,在布线不合理或走线太长情况下,串口CSB,FCSB,SDIO,SCLK管脚容易受到干扰,功率输出(20dBm)越大,工作频率越低,受干扰的概率越大,建议靠近四个管脚预留到地电容(27pF)滤除射频干扰。

推荐客户参考CMOSTEK直连(DirectTie)匹配的设计,TX和RX通路到直连点之间的网络尽量采用官方推荐的相同值的元件。而天线匹配滤波网络(L4,C3,L5),要根据天线阻抗,成本要求,是否要求满足CE/FCC规范等因素,来调整滤波器的阶数和元件值。如线路板面积受限,建议L1-L8,仍采用高Q值叠层0603电感(如SunlordSDCL1608系列),但电容都可采用0402封装。

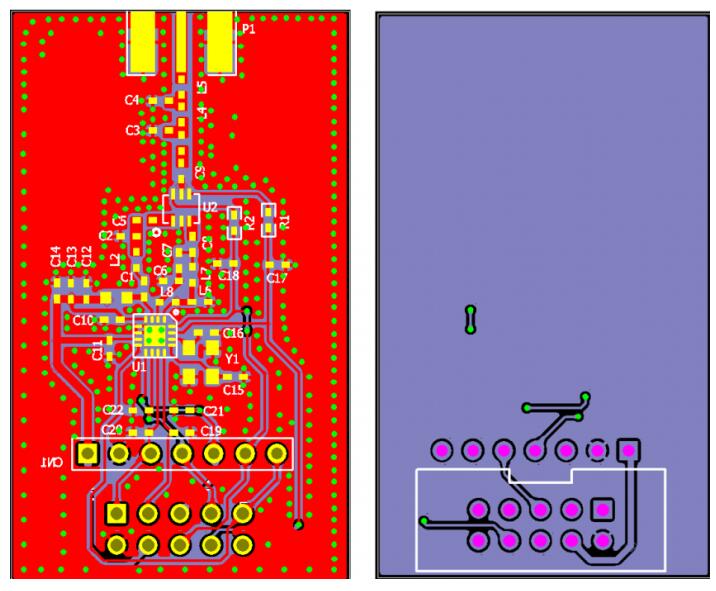

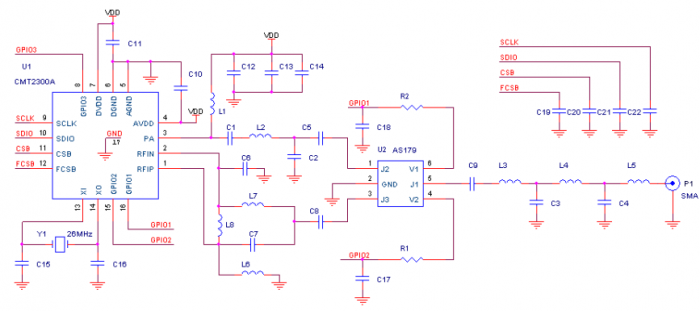

CMOSTEK直连(DirectTie)匹配PCBLayout为两层布线设计。

说明如下

1、射频信号路径尽量的直且短,减小射频信号输入与输出的的损耗。

2、射频走线应该尽量平整,以减小传输线上的阻抗波动而产生反射。在上图中L2到P1间走线为50Ω阻抗传输线。本参考设计中,双面板为FR4板材,介电常数Er=4.6,铜皮厚1oz,PCB板厚0.8mm,当取传输线宽度为1mm左右,且传输线与包地(GND)的间隙设定为0.35mm时,就可得到阻抗为50欧姆的传输线。

3、尽量不要有丝印落在射频路径上,丝印会影响传输线阻抗。

4、L1离PA管脚尽量近。相邻电感尽量正交摆放,可减少相互耦合。

5、直连结合点的分支网络(上图C2,L7和C7相连部分)要尽量短。

6、射频通路,晶振电路和IC的下方相邻层要有完整的铺地(GND)。

7、TX和RX通路间要有GND网络进行隔离。

-

射频

+关注

关注

104文章

5575浏览量

167699 -

电路设计

+关注

关注

6673文章

2451浏览量

204197

发布评论请先 登录

相关推荐

天线和射频匹配电路设计-培训教程下载

【下载】《射频电路设计》——快速掌握射频电路的基本设计方法和原则

差分匹配电路设计和双频匹配电路设计培训教程

CMT2300A无线数据收发模块资料

为什么说CMT2300A是Sub-1GHz超低功耗的射频收发器

超低功耗Sub-1GHz性价比首选方案:CMT2300

超低功耗Sub-1GHz性价比首选方案:CMT2300

CMT2300A 超低功耗Sub-1GHz射频收发器的详细中文资料免费下载

使用CMT2300A芯片设计射频匹配网络的数字信号和电源滤波电路与铺地

CMT2300A的开关射频匹配网络电路设计

射频和天线匹配电路设计中LC器件选择

CMT2300A 433MHz无线收发芯片

CMT2300A的直连射频匹配网络电路设计

CMT2300A的直连射频匹配网络电路设计

评论