高速信号不遵循阻力最小的路径;他们遵循阻抗最小的路径。本系列文章介绍了下一个项目的PCB设计布局。

昨天的电子产品非常宽容。糟糕的原理图设计和糟糕的PCB布局仍然会产生功能板。技能可以随着时间的推移而增加,但运气最终会耗尽。

当工程师第一次开始使用固态电子产品时,芯片的工作电压更高,上升时间比现在制造的芯片更慢。但是,为了使PCB和微芯片更小,我们还降低了工作电压,降低了噪声容限。随着我们继续推动降低和降低IC工作电压,工程师需要越来越多地考虑他们的选择,以确保他们的设计无需昂贵且耗时的重新设计。

那么什么类型的噪声要注意,以及如何改进设计以避免它们?

本文是受到主题演讲启发的几篇文章之一,由Eric Bogatin博士在Altium Live 2018上发表。

故意路线返回路径!传播延迟

电磁场沿着并围绕导体并渗透其附近的物体。这些场中存在的能量将被转移到你想要的位置。

电磁场的变化以快速但有限的速度传播,并且需要一些时间。现场变化到达电路的远端。

当玩简单的电路并查看页面上的原理图时,很多人会想象电路中的变化立即发生:按下开关并出现指示灯瞬间闪耀。很容易产生一种错误的直觉,即开关状态的变化会立即改变光的状态。

误解的发生是因为状态的变化超过了人类感知的极限,达到了很多个数量级。当处理传播变化的时间(传播延迟)与改变状态所需的时间(上升时间/下降时间)相当或超过的电路时,您必须澄清您的思维过程以适应传播延迟。/p》

电磁场的变化将以光速的一小部分传播到整个电路中。 PCB走线上的状态变化(逻辑低至逻辑高)沿着产生电流的长度建立电势。该电流在导体周围产生电磁场。但由于电磁场的变化需要时间传播,因此迹线的两端可能处于两种不同的状态,其中一个过渡点沿着长度移动。

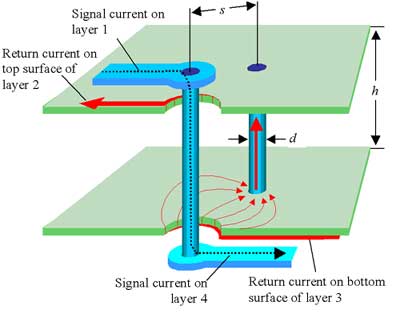

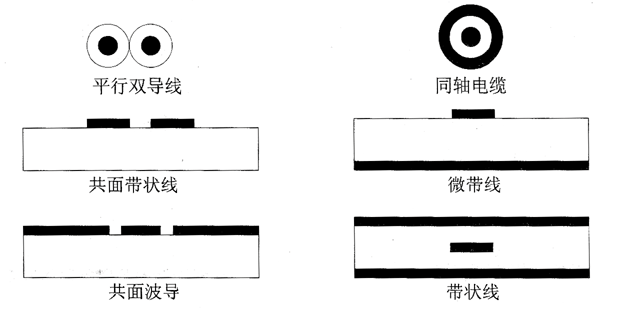

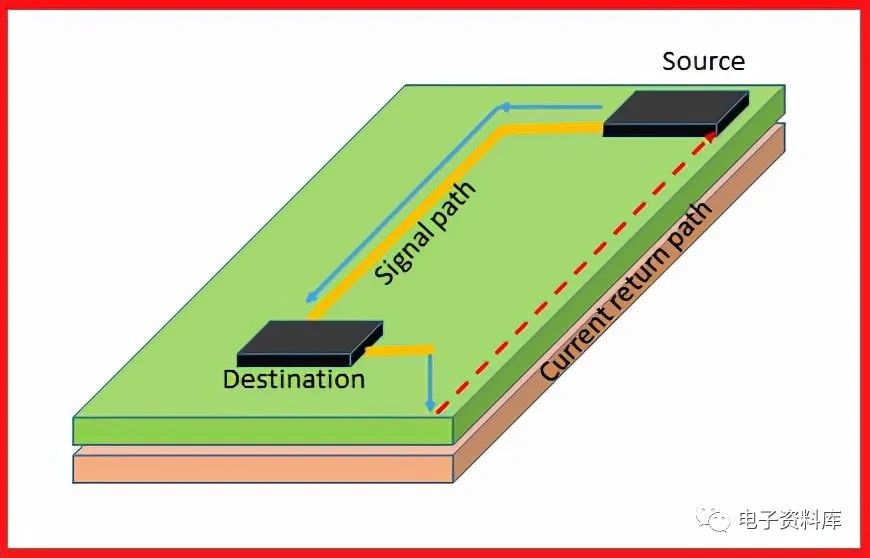

此图显示两个导电PCB两侧的迹线。当电流开始在顶部迹线中流动时,在底部迹线中立即建立返回电流。

如果您没有提供立即返回路径您的走线和过孔,不需要的电流将在附近的导体中形成,特别是如果您有快速转换(《1ns)。

最佳实践规定如下:始终在同一层或相邻层中提供接地返回路径用于单端信号,差分对和电源层的层。

始终在同一层或相邻层中为单端信号,差分对和电源层提供接地返回路径。

地面返回途径。来自“高速信号传播”的Howard Johnson博士的图片,图5.33,第353页,来自Signal Consulting,Inc。

高速信号和最小阻抗路径

高速信号不遵循阻力最小的路径;它们遵循阻抗最小的路径。

当新工程师设计PCB时,他们倾向于完全忘记电路返回路径中阻抗的无功部分,并严格关注电阻。当老工程师设计PCB时,他们倾向于做同样的事情。谁又能责怪他们呢?很少有人能够使用电磁模拟器,使他们可以看到电路在不同频率下的行为。

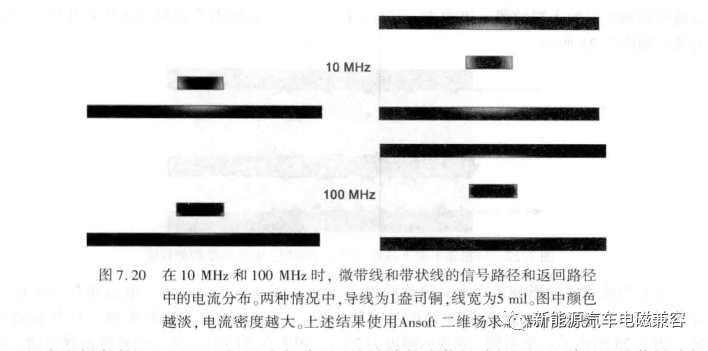

在考虑返回路径时,请记住,随着频率的增加,阻抗的无功部分变得越来越重要,随着上升/下降时间减少。

在均匀的适度频率下,电流的返回路径将尝试直接在导体下方流动。如果你没有提供这条路径,它会发现一条不太理想的路径通过电路的其他部分 - 也许是沿途创建天线。

返回电流寻找阻抗最小的路径。在低频时,地平面中的大部分返回电流直接从负载流到源。负载和源之间的这条直线表示最小电阻的路径,并且在低频时表示最小阻抗的路径。随着频率的增加,走线和走线正下方铜线之间的互感会产生一个低阻抗路径,导致接地层中的返回电流跟随信号层上的走线。

如何在PCB设计中使用返回路径

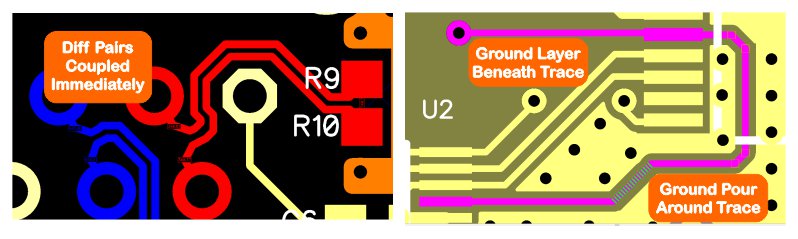

在PCB上,路由快速变化的信号,并在其附近有返回路径。差分走线应从封装引脚出来并立即紧密接近。时钟信号和其他快速上升时间/下降时间信号应由地面浇注包围和/或在其下方具有完整的,不间断的接地平面,以最大限度地减少辐射EMI噪声。如果您的设计需要FCC测试,您甚至可能需要路由两个接地层之间的快速变化信号,并用通孔缝合环绕它们。

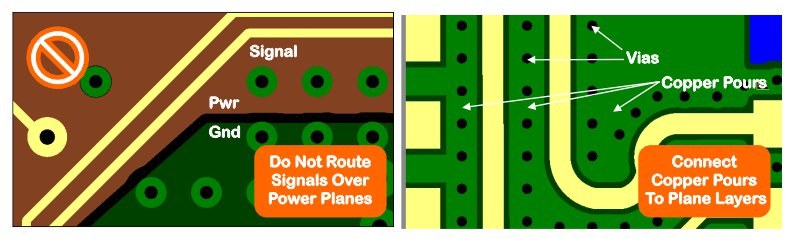

以下两个图像展示了PCB布局示例,展示了两种降低接地噪声的方法:

通过整个路径将差分对保持在一起

在信号线的正下方或旁边提供接地返回路径

耦合在一起的差分对

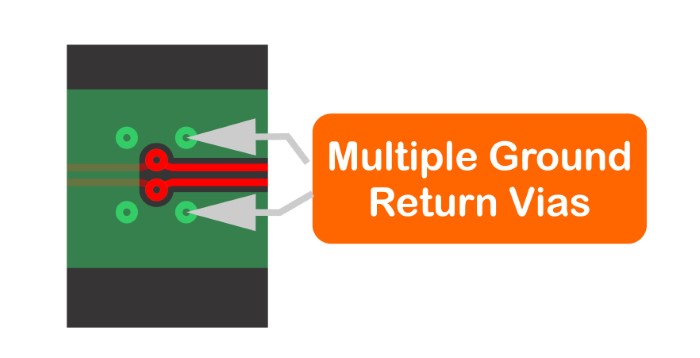

在差分对过孔附近放置接地回路过孔,为信号在层与层之间传播时提供接地回路。

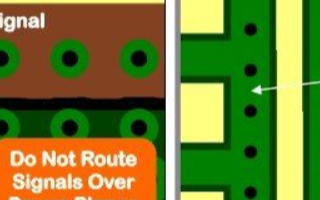

在下面的例子中,左边的PCB la您将从上方(信号,电源,接地,信号)显示多个PCB层,并演示通过电源层布线。在到达接地层之前,移动电源的信号将与电源平面共享其电场,并且平面的噪声会在信号线中产生噪声。

右侧的PCB部分显示了接地浇注和缝合两个信号线附近。如果铜线没有连接到下面的地平面,则铜线在互连线周围会变成辐射元件。

结论:利用地面返回通孔和接地回路

仔细而有意地规划接地回路,可以防止不必要的电流在电路的某些部分形成。为所有信号提供有意的接地回路过孔和接地回路 - 尤其是高速开关信号。

-

电路

+关注

关注

172文章

5909浏览量

172228 -

pcb

+关注

关注

4319文章

23095浏览量

397788

发布评论请先 登录

相关推荐

高速电路PCB “地”、返回路径、镜像层和磁通最小化

高速PCB设计——回流路径分析

浅谈建模返回路径阻抗效应

PCB EMC问题:最常见的返回路径不连续资料下载

返回路径平面宽度不同的情况VS完整返回路径平面S参数情况

PCB设计之平衡铜威廉希尔官方网站 介绍

高速电路PCB“地”、返回路径、镜像层和磁通化

使用返回路径实现更好的PCB设计步骤概述!

使用返回路径实现更好的PCB设计步骤概述!

评论