引言

PCI(PeripheralCompornentInterconnect,即外围部件互连)总线是一种先进的高性能32/64位地址数据复用局部总线,该总线是以INTEL为首的多家集团设计的,PCI总线可以同时支持多组外围设备,且处理器和时钟频率无关,可以提供高达132MB/s的数据传送速率,PCI总线具有严格的规范,只要符合PCI规范的扩展卡,那么,插入任何PCI系统就能可靠地工作,是当今PC领域中流行的总线。

PCI总线协议非常复杂,目前实现PCI接口的有效方案分为两种:即使用可编程逻辑器件和使用专用总线接口的器件,可编程逻辑器件实现PCI接口比较灵活,可以利用的器件比较多,现在有许多生产可编程逻辑器件的厂商(如Xilinx的Logicore和Alerra的AMPP)都提供经过严格测试的PCI接口功能模块,用户只要进行组合设计即可,但这种方法难度较大,设计周期较长。而采用专用接口器件实现完整的PCI主控模块和目标模块的功能,则可将复杂的PCI总线接口转换为相对简单的用户接口,用户只要设计转换后的总线接口即可。但这种方法难度较大,设计周期较长,而采用专用接口器件实现完整的PCI主控模块和目标模块的功能,则可将复杂的PCI总线接口转换为相对简单的用户接口,用户只要设计转换后的总线接口即可。虽然这种方式不够灵活,但由于其对PCI协议的良好支持,以及提供给设计者的良好接口,都大大减少了设计开发的难度和周期,现有的PCI接口芯片主要有AMC公司的AMCCS59xx系列和PLX公司的PCI9805x系列。PLX公司的PCI9052就是一款较常用的总线接口芯片。

PCI9052芯片介绍

PCI9052是PLX威廉希尔官方网站 公司继PCI9050之后推出的低成本、低功耗、高性能总线接口芯片,通过该芯片可以使多种局部总线快速转换到PCI总线上。

◇主要特点

(1)兼容PCIV2.1协议特性。PCI9052芯片与PCI协议V2.1版兼容,可支持低成本的从模式适配设备,也支持从ISA适配卡向PCI适配卡的转换。

(2)采用直接从(目标)模式传送数据。支持突发存储器映射和I/O映射方式,可从PCI总线到局部总线上存取数据。读写FIFO(先入先出)寄存器使得局部总线和PCI总线具有高性能的突发方式,PCI总线总是工作在突发方式,但是局部总线可以设置成突发方式或者连续单周期方式。

(3)带有中断发生器,可以从两个局部总线中断输入中生成一个PCI中断。

(4)PCI9052局部总线接口运行于TTL时钟,并可生成必要的内部时钟,局部TTL时钟与PCI时钟异步工作,并允许局部总线独立于PCI时钟工作,其缓冲PCI总线时钟(BCLKO)可与局部总线时钟(LCLK)相连。

(5)PCI9052局部总线配置可编程。支持复用或非复用的8/16/32bit局部总线,芯片有4字节使能(LBE[3:0]#)、26根地址线(LA[27:2])和32/16/8bit数据线(LAD[31:0])。

(6)支持先读模式、即预取数据可从PCI9052内部的FIFO寄存器读取,用以代替局部总线,但地址必须是前一条地址的后续地址,且应为32位宽度(下一地址=当前地址+4)。

(7)所有控制、地址和数据信号都可由PCI9052直接生成,用于驱动PCI和局部总线,而无需额外驱动电路。

(8)带有串行EEPROM接口,可用于加载配置信息,这对于装载一个特定的适配设备信息(网络节点号、厂商类型码和片选等)是很有用的。特别是将PCI9052转换为ISA接口模式时,串行EEPROM是必需的。

(9)提供了四个局部片选信号,其基地址和每一个片选的范围可由串行EEPROM配置,也可由主控制器在线编程。

(10)具有五个局部地址空间,基地址和每一个局部地址空间的范围可由串行EEPROM配置或由主控制器在线编程。

(11)支持BigEndian和LittleEndian字节间的转换。当局部总线是16位宽度或8位宽度时,PCI9052同时支持BigEndian字节模式转换为字或字节宽度。

(12)为了匹配以前的接口读/写(RD#/WR#)信号,可以从时钟周期的开始延时(例如ISA总线接口)。

(13)附加的LRDYi#(localreadyinput)握手信号可用于产生各种等待状态,PCI9052内有等待状态发生器(读/写地址到数据、数据到数据和数据到地址之间)。

(14)局部总线预锁存计数器可以编程为(无预锁存)4、8、16或连续值(预锁存计数器关闭)模式,如果使用了连续地址(必须是32位),则预锁存数据可以作为缓冲数据来使用。

(15)PCI9052兼容PCIV2.1协议延时读的4种模式,即PCI读和写刷新模式、PCI读无刷新模式、PCI读无写模式和PCI写模式。

(16)带有一个可编程PCI读写重试延迟计时器,可以为PCI总线产生一个重试信号。

(17)带有ISA逻辑接口模式,支持PCI总线到ISA总线的单周期存储器(8位或16位)读写和I/O访问。

(18)支持PCI目标锁定机制,PCI主控设备可以通过锁定信号独占对PCI9052的访问。

(19)PCI总线传输速率达132MB/s。

◇结构组成

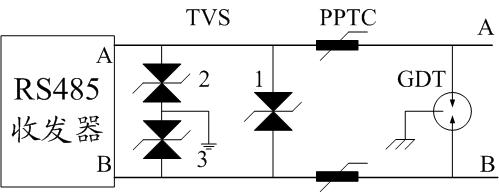

图1所示是由PCI总线接口芯片、局部总线接口和串行总线接口组成的接口电路。

◇器件功能

PCI9052作为总线目标接口芯片,可为非PCI设备与PCI总线提供数据通道,PCI9052的主要功能如下:

(1)初始化

上电时,PCI9052的内部寄存器将由PCI总线的RST信号复位成默认值,并在局部总线上输出LRESET信号,以检验串行EEPROM,如果安装了串行EEPROM且第一个16位字不全为1,则PCI9052用串行EEPROM中的值来配置片内寄存器,否则使用缺省值。

(2)复位

当PCI总线输入复位信号时,PCI总线全部输出呈高阻态,此时PCI9052整体复位并输出LRESET信号,PCI总线上的主控设备也可以通过软件设置杂项控制寄存器(CNTRL:50h)的第30位为1,来使PCI9052复位并输出LRESET信号,此时PCI和局部配置寄存器的值不变,PCI9052将一直保持复位状态,而且此时主设备只能访问配置寄存器,而不能访问局部总线。当CNTRL[30]=0时,系统将清除PCI9052的复位状态。

(3)串行EEPROM

复位后,PCI9052将检查串行EEPROM是否存在,一个有效的低电平START位表示串行EEPROM存在,START位为1表示串行EEPROM不存在,串行EEPROM的第一个字如不全为“1”,PCI9052便可用它进行配置,而如果串行EEPROM不存在或为空,PCI9052则采用缺省值配置,PCI9052总线上的主机可以对串行EEPROM进行读写,杂项控制寄存器(CNTRL:50h)的[29:24]位控制着PCI9052对串行EEPROM的位进行读写,将杂项控制寄存器位CNTRL[29]置1可以用串行EEPROM重新配置PCI9052。

(4)内部寄存器访问

PCI9052的内部寄存器为总线接口的设计与实现提供了最大的灵活性,这些寄存器可以分为两类:PCI配置寄存器和局部配置寄存器,两类都可以通过PCI总线或串行EEPROM来配置。

(5)直接数据传输模式

PCI总线上的主设备能直接访问局部总线上的从设备。PCI9052内部的配置寄存器可译码和映射这些要访问的局部地址空间,读写先入先出寄存器可支持PCI和局部总线之间的高性能突发传输方式。

(6)PCI中断(INTA)

通过局部中断输入(LINTil和LINTi2)或软件中断(CNTRL寄存器30位)可以产生一个PCI中断(INTA)通过PCI9052中断控制/状态寄存器可以禁止或使能某种中断,PCI9052中断控制/状态寄存器同时可提供各个中断的状态指示。

(7)局部中断(LINTi[2:1])

PCI9052提供有2个局部中断输入(LINTi[2:1],通过寄存器INT[2:1]),通过寄存器INTCSR;4Ch可将局部中断设置成沿触发或电平触发方式,局部中断能产生PCI中断。

(8)系统出错

如果PCI命令寄存器中的使能奇偶校验位,检测到一个地址奇偶校验出错时,PCI9052将产生一个SERR信号。

PCI9052的应用

PCI9052接口芯片作为通用PCI接口,其应用场合和范围是非常广泛的。随着PC机的发展,PCI扩展槽已成为PC机主板的基本配置,而带ISA扩展槽的PC机已经越来越少,ISA扩展槽在PC机中彻底地消失的日子即将到来,在作者所在公司设计生产的火灾报警控制系统中原有的ACTNET网络接口卡是基于ISA总线的插件,现在则要利用PCI9052芯片的ISA模式来对原来的板卡进行升级改造,以使原来的板卡在做少量改动的情况下可以插在PCI总线插槽中正常工作。

这种PCI插卡的借口示意图如图2所示,它主要由一片PCI9052、ARCNET网络控制器以及一些外围器件构成。

PCI9052的内部结构中包含了一个独立的ISA逻辑接口,用于为ISA总线到PCI总线提供一种简单的转换。它支持8位和16位数据宽度的ISA从设备,也可以是内存映射或I/O映射。同时可直接从先读模式来提高读取数据的吞吐量,一旦ISA接口模式被使能,PCI9052将只执行单个周期操作,应当特别注意的是,ISA接口模式下,串行EEPROM是必需的。

具体设计时,可以使用两种方法配置PCI9052以用于ISA接口模式:一是烧写串行EEPROM方法,即使用烧写器将数据写入串行EEPROM;二是热配置方法,也就是从PCI总线通过PCI9052芯片来烧写串行EEPROM。

配置注意事项

当为ISA接口模式进行配置时,必须注意以下几点:

(1)存取ISA接口引脚时,要参照PCI9052引脚的C/ISA模式引脚图来连线。

(2)空间0分配给ISA接口的内存存取。

(3)空间1分配给ISA接口的I/O存取。

(4)无论在空间0还是在空间1,ISA访问都是有效的。

(5)标准从周期能够用于访问空间2、空间3和串行EEPROM。

在设计电路板时,要严格遵循PCI规范,电源和地线要尽可能宽且电源滤波要良好,在芯片的每个电源引脚,最好接0.01-0.1μF的滤波电容,一般来说,PCI编码推荐做4层板,其实只要布线合理,做两层板也是可以的,在连线时,要注意PCI规范中提到的反射波信号,由于驱动信号的一半要靠反射波来提升,所以对信号线的长度要求为:64位卡的32位信号具备的最大连线长度是1500mil,64位扩展信号的附加信号的连线长度为2000mil,PCI的CLK长度2500mil±100mil,这些条件一定要严格遵守,尤其是CLK信号线长度的要保证在要求的范围内,否则,PCI插件工作将不正常,并会出一些怪现象,另外,PCI卡上最好在从槽上引的电源上多加几个电容,所有电源都必须退藕。用作上拉或下拉的电阻一般取值2.2KΩ即可。

还有一个要注意的是,PCI信号中prsnt1和prsnt2必须至少有一个接地,否则,系统肯定找不到卡,主板就是靠这两个信号来判断这个插槽上是否有卡,而其接法同PCI卡使用的功率有关,具体的含义如下(Open表示悬空,Ground表示接地):

prsnt1prsnt2含义

OpenOpennocard

GroundOpen25w

ObenGround15w

GroundGround7.5w

最后,由于PCI9052没有提供符合工业标准IEEE1149.1边界扫描接口,PCI规范中涉及到的5个边界扫描信号中的TRST、TCK、TMS要悬空、TDI和TDO在板上要短接,以免扫描链被打断。

结束语

实践证明,PCI9052是一款优秀的PCI接口芯片,该芯片对基于ISA总线的接口向PCI的转换提供了极大的方便,设计者用它可避免直接面对复杂的PCI总线协议。因为,用PCI9052开发的产品,可减少外围器件,降低了开发难度,同时也缩短了开发周期,延长了产品的生命期。

-

PCI

+关注

关注

4文章

666浏览量

130251 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43035

发布评论请先 登录

相关推荐

PCIe接口的工作原理 PCIe与PCI的区别

通过PLX PCI9080桥接芯片实现TMS320C6000扩展总线与PCI总线的接口

pci总线可以直接与cpu连在一起吗为什么

EN Power Bus二总线接口转接485方案芯片-485接口芯片

探索 PCI 转 PMC 载板转接卡:连接不同接口的桥梁

PCI 接口的反射内存卡

在哪里可以下载opa197和opa4180的符号和封装?

片上集成TVS器件保护总线接口芯片

XIO2001 PCI Express至PCI总线转换桥接器数据表

can总线中继器是安装在哪里的

如何通过Jlink查看GD32芯片跑飞后程序死在哪里?

PCI总线接口芯片可以在哪里应用

PCI总线接口芯片可以在哪里应用

评论