2019年8月7日,中国,北京 —— 自适应和智能计算的全球领先企业赛灵思公司(Xilinx, Inc.,(NASDAQ:XLNX))今天宣布推出 Alveo™ U50,进一步扩展其Alveo 数据中心加速器卡产品组合。Alveo U50 卡是业界首款可以支持第四代PCIe ( PCIe Gen 4) 的轻量级自适应计算加速卡, 专门为扩容各种不同关键计算、网络和存储工作负载而特别设计,而且所有的加速都在同一个可重配置 FPGA 平台之上实现。

Alveo U50 -面向任意服务器和各种云的业界首款自适应计算、网络和存储加速器卡

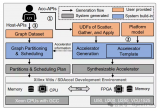

Alveo U50为客户提供了小尺寸、低功耗的可编程加速器平台,专门为不同规模、不同类型的系统架构及领域特定的加速应用而打造,面向任意类型的服务器部署,包括本地、云端和边缘。为了应对不断变化的云微服务等新兴工作负载的挑战,Alveo U50在更大吞吐量、更低延迟和更高功耗效率方面实现了10-20倍的大幅提升。对于加速网络和存储工作负载,U50卡可帮助开发人员通过将数据更接近计算的方式来识别并打破时延和数据移动的瓶颈。

Alveo U50 卡采用赛灵思 UltraScale+™ 架构,率先使用半高半长的外形尺寸和低于75 瓦的低包络功耗。该卡支持高带宽存储器(HBM2)、100Gbps的网络连接,并支持第四代 PCIe 和 CCIX 互联标准。通过支持标准的 PCIe 服务器插槽并用仅为现有 Alveo 卡1/3的功耗, Alveo U50大幅扩展了自适应加速威廉希尔官方网站 可以部署的范围,从而为要求严苛的计算、网络与存储工作负载带来了前所未有的高吞吐量与低延时。8GB HBM2 提供了超过 400 Gbps 的数据传输速率, QSFP端口提供了高达每秒100 Gbps的网络连接。此外,高速网络 I/O 还支持各种前沿应用, 如NVMe-oF™解决方案(NVM Express over Fabrics™),解耦计算存储(Computionial Storage)和专业金融服务应用

从机器学习推断、视频转码和数据分析到计算存储,再到电子交易和金融风险建模,Alveo U50 可以将 Alveo 平台的灵活性、高吞吐量和低时延等性能优势,扩展到任意服务器的部署中。与固定架构的其他解决方案不同,Alveo U50的软件和硬件可编程能力,使客户能够在工作负载和算法不断演进的同时,满足不断变化的需求并随时优化应用性能。

Alveo U50加速解决方案可在广泛的跨领域应用中提供重要的客户价值,其中包括:

Ø 深度学习推断加速(如语音翻译):时延降低高达25倍,吞吐量扩大10倍,同时在语音翻译的性能方面,相比仅使用GPU,每节点的功耗效率实现了显著的提升1;

Ø 数据分析加速(如数据库查询):运行 TPC-H Query 基准测试时,Alveo相比存储器内的 CPU,每小时吞吐量提升 4 倍,运营成本降低 3 倍2;

Ø 计算存储加速(如压缩):将压缩/解压缩吞吐量提高了 20 倍,实现了更快的Hadoop 和大数据分析,同时相比仅CPU节点将每节点成本降低了 40%3;

Ø 网络加速(如电子交易):相比仅 CPU 的 10微妙延时,能将时延降低 20%,交易时间不到 500纳米4;

Ø 金融建模(如网格计算):运行蒙特卡洛(Monte Carlo)interwetten与威廉的赔率体系 时,Alveo U50 的功耗效率相比 GPU 提升7 倍,能够更快速分析并做出判断,实现确定性时延和运营成本的降低5。

赛灵思执行副总裁兼数据中心事业群总经理 Salil Raje 先生表示:“对数据中心永无止境的需求,正在将现有数据中心基础设施的性能推向天花板,行业需要灵活应变的解决方案来优化广泛应用领域工作负载的性能,以延长现有基础设施的生命周期,并最终降低总拥有成本(TCO)。新款 Alveo U50 面向数据中心工作负载带来了优化的外形尺寸,以及前所未有的高性能与灵活应变能力。我们将持续与不断壮大的应用合作伙伴进行合作完善生态环境,共同构建解决方案堆栈,为众多行业提供此前不可想象的新功能。”

业界支持:

AMD 应用工程副总裁兼CTO Raghu Nambiar 表示:“即将面世的AMD 第二代 EPYC 处理器系列理想适用于Alveo U50 这样的数据中心优先加速器,可将计算、网络和存储加速功能整合在单个平台上。借助 AMD 即将率先推出的 x86 服务器级支持第四代 PCIe CPU 的领先优势,Alveo U50 将成为业界首款可以支持第四代 PCIe 的自适应加速器卡。我们期待着与赛灵思不断展开合作,一同将融合 Alveo 加速威廉希尔官方网站 的 AMD EPYC 解决方案的优势提供给超大规模数据中心及企业用户。”

IBM Power Systems首席架构师Steve Fields表示:“ IBM对赛灵思Alveo 系列产品新增Alveo U50 自适应加速卡的扩展感到非常兴奋,我们相信,小尺寸的外形、HBM2内存性能和PCIe Gen 4速度与IBM Power处理器的结合,将使得整个OpenPower生态系统在为业界提供尖端的自适应加速解决方案方面领先一步。”

Moor Insights & Strategy高性能计算和深度学习高级分析师Karl Freund 表示:“凭借Alveo U50的小型化设计和先进功能,赛灵思进一步巩固了其通过可配置逻辑扩大加速市场的战略。借助在高增长用例中所展现出的显著性能优势,新的Alveo U50可以助力赛灵思进一步突破市场噪音(market noise)。”

西部数据公司 (Western Digital)数据中心系统业务部产品管理高级总监Scott Hamilton表示:“我们非常高兴能够在FMS(Flash Memory Summit,全球闪存大会)上与赛灵思合作,共同展示Alveo U50和我们的OpenFlex NVMe-oF可组合平台的灵活性和高性能。赛灵思正在利用NVMe-oF引领基于架构的计算存储,以实现服务器资源的完全解耦。因为我们采用了真正的解耦方法来处理SDS(软件定义存储)基础设施,我们相信新的Alveo U50将成为西部数据生态系统的重要组成部分。”

-

赛灵思

+关注

关注

32文章

1794浏览量

131271 -

加速卡

+关注

关注

1文章

60浏览量

10946

原文标题:这些神问答,也许让你豁然开朗!

文章出处:【微信号:gongkongworld,微信公众号:工控资料窝】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

易灵思FPGA产品的主要特点

U50的AMD Vivado Design Tool flow设置

思尔芯赛题正式发布,邀你共战EDA精英挑战赛!

赛思快讯 | 发展新质生产力问道赛思?赛思如何下好“创新棋”?

中科爱毕赛思红外光电探测威廉希尔官方网站 ,打破高端市场“卡脖子”困境

安赛思半导体与新加坡三福半导体达成战略合作

FPGA版通用图形处理架构创新解决方案

水晶头50u和30u区别大吗

解析FPGA竞争格局背后的驱动因素

赛灵思Alveo™ U50面世

赛灵思Alveo™ U50面世

评论