SAN JOSE - Cadence Design Systems Inc.今天宣布推出基于块的设计(BBD)和基于平台的设计(PBD) )方法和工具流向苏格兰的阿尔巴中心。 BBD和PBD是用于片上系统(SoC)开发的一套完全编码和验证的设计方法。

“BBD和PBD设计方法,以及之前由Cadence提供的时序驱动设计TDD方法,代表完整SoC设计环境的重要组成部分,“Cadence方法论服务高级副总裁Adriaan Ligtenberg说。

这三种SOC设计方法是Alba中心工科学生课程的一部分。系统级集成研究所(ISLI),其中Cadence是主要参与者(参见4月在线出版物的故事)。 “我们感谢Cadence为该研究所及其成员大学提供的帮助,为我们的课程开发最先进的SOC威廉希尔官方网站 设计课程和项目,”ISLI主任Steve Beaumont教授说。

BBD和PBD方法建立在Cadence的TDD方法基础之上,用于快速创建IP核。

BBD是一种通过流片输出进行寄存器传输级(RTL)设计的分层方法。它包括项目管理,时序驱动的块创作,分层芯片规划,顶级芯片组装和分层验证。它还包括测试,块级验证,基于总线的设计和设计重用的方法。

PBD是一种基于平台的SoC设计方法,建立在BBD的基础之上,增加了功能用于嵌入式软件设计,interwetten与威廉的赔率体系 模块设计,高级系统设计,快速原型设计和IP管理。它还包括一个参考多媒体设计平台。

-

PCB打样

+关注

关注

17文章

2968浏览量

21699 -

华强PCB

+关注

关注

8文章

1831浏览量

27749 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43036

发布评论请先 登录

相关推荐

Cadence和PADS安装后无法启动Cadence的解决方法

Cadence Allegro添加盲孔报错

Cadence Allegro 17.X 手动添加元件与元件引脚添加编辑网络的方法

向固件添加网格有多难?

Cadence推出首个TLM驱动式设计与验证解决方案

Cadence/allegro V16.0的安装方法

用于SoC验证的(UVM)开源参考流程使EDA360的SoC

Cadence解决方案助力创意电子20纳米SoC测试芯片成功流片

智原科技采用Cadence数字实现与验证解决方案,提升最大型SoC设计的性能

Wind2将在苏格兰建设28兆瓦无补贴风电场

Cadence演示面向PCI Express 5.0系统的SoC硅芯片

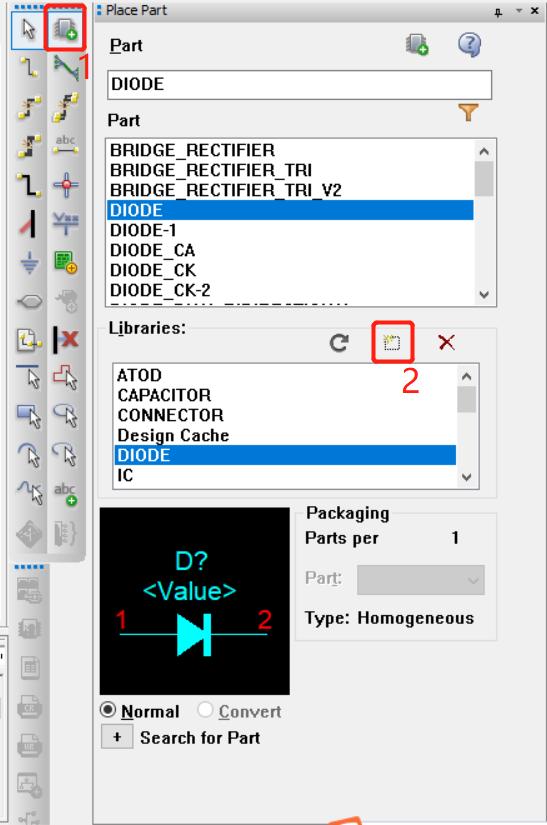

Cadence添加logo的软件

cadence如何添加和导出原理图封装库

Cadence:以 AI 威廉希尔官方网站 驱动数字验证的变革

Cadence 与 Arm Total Design 合作,加速开发基于 Arm 的定制 SoC

Cadence向苏格兰设计中心添加新的SoC方法

Cadence向苏格兰设计中心添加新的SoC方法

评论