负偏压温度不稳定性[NBTI]是不希望的老化效应。每当PMOS晶体管被负偏置时,它表现为 V th 的幅度的增加。它主要在65nm以下的威廉希尔官方网站 上展出。在亚20nm节点处,效应变得更加突出。

在PMOS晶体管的负偏压下,这是PMOS的正常操作,发生Si-H键的解离。这种键的解离在高温和施加的负偏压的持续时间内加速。这种Si-H键的解离产生界面陷阱。这种接口陷阱的产生增加了PMOS的阈值电压。阈值电压的增加表现为PMOS开关周期的增加。

当PMOS用于AC模式(动态开启和关闭)时,在应力状态(PMOS ON状态)期间产生的接口陷阱由于退火影响而减少。因此,与PMOS的静态应力操作相比,PMOS的动态操作在 V th 中经历相对较少的退化。在今天的时代,我们有数字电路,其中电路中的一些PMOS可能在一定时间开启而其他PMOS关闭。因此,在整个芯片中发生不对称NBTI退化,这可能导致各种块中的定时故障。今天,由于缺乏有效的NBTI测量模型,设计工程师将NBTI边缘作为基于经验数据的软糖因子。因此,他们最终可能会增加比实际NBTI要求更多的悲观情绪。

NBTI对逆变器的影响

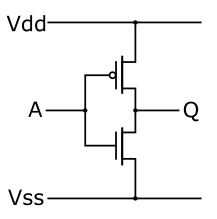

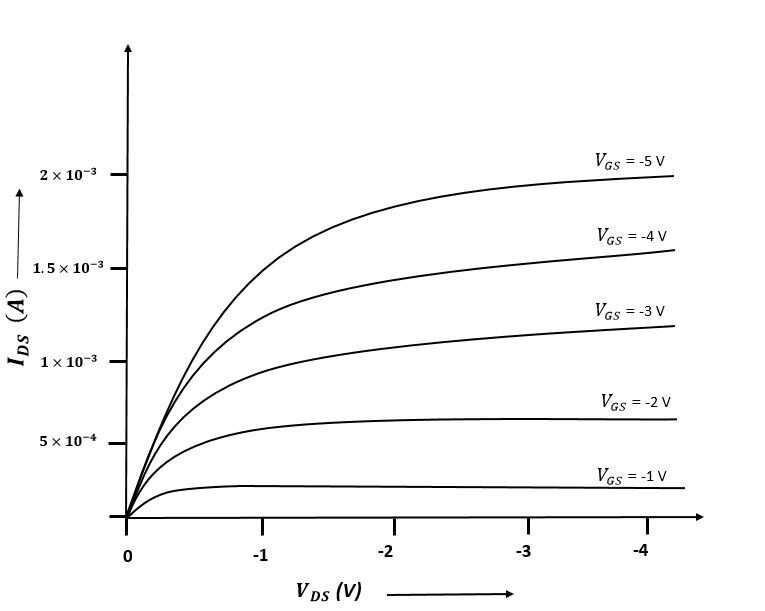

在这一部分中,我们将分析NBTI如何通过使用导致电路明显延迟最简单的开关CMOS电路,即逆变器。图1显示了CMOS反相器,图2显示了其PMOS特性。

图1. CMOS逆变器

图2. PMOS特性

输出电流可通过以下2个方程式计算得出。等式1对于线性区域有效( V DS GS - V tp )和公式2对饱和度有效( V DS > V GS - V tp )。

其中 I D 是漏极电流,μ是空穴迁移率, ε ox 是介电常数, T ox 是氧化物厚度。 W 和 L 是晶体管的有效栅极宽度和长度。 V tp 是pmos的阈值电压,并且 V GS & V DS 分别是栅极 - 源极和漏极 - 源极之间的电压。

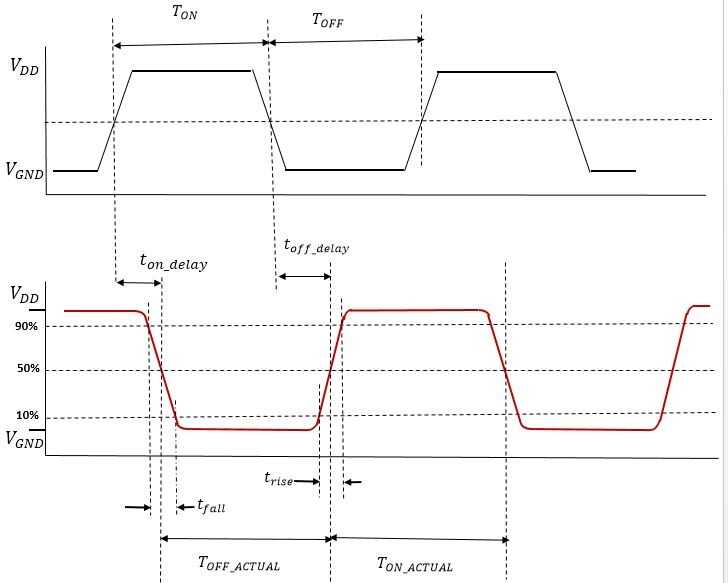

图3.逆变器的输入输出波形

图3显示了逆变器的输入及其输出。在PMOS中,阈值电压的改变将影响漏极电流。因为,在NBTI的情况下,阈值电压变得更负,即,其绝对值增加,因此漏极电流减小,这将导致上升时间和下降时间的增加,这又将增加开启延迟。 。当这样的缓冲器/逆变器放置在数据路径中时,NBTI通过增加额外的延迟来影响数据的到达,从而产生可能破坏我们设计的潜在设置故障。

分析

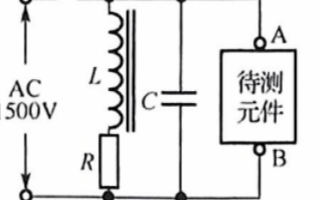

各种研究表明,FinFET中的NBTI会导致阈值电压偏移50至100毫伏,具体取决于芯片的工作条件和工作寿命。图4显示了interwetten与威廉的赔率体系 设置。动机是计算NBTI对整体延迟的影响。我们将数据路径命名为P1。它是从启动触发器的输出(Q)到捕获触发器的数据输入(D)的典型数据路径。该路径包括逆变器和缓冲器的组合。该路径在相同定时路径中的不同门之间展现出各种抵消效果,从而与路径的预期延迟相比减小了总延迟。在逻辑深度较大的数据路径中,此效果变得更为显着。

图4.模拟设置

下图显示了NBTI在16nm处引起的延迟变化以及Vdd对延迟的影响。我们在3个典型电源电压(Vdd)下完成了模拟。 0.72V,0.8V和0.88V。这些电源电压值通常用于这种低威廉希尔官方网站 节点。

图5显示了带电源(x轴)的逆变器新鲜和老化样品的延迟变化(y轴)。从上述方程式来看,电源的影响是显而易见的,电压的增加会增加漏极电流,从而减少延迟。图6显示了缓冲区的类似行为。在这些数字中可以清楚地看到延迟的增加。

图5.逆变器的延迟变化

图6.缓冲区的延迟变化

图7.数据路径延迟

图7显示了数据的延迟变化路径P1。 NBTI模拟的数据显示在0.72V下的最大降级。如前所述,0.72电压也表征比其他比较电压更多的延迟,这种电路中的NBTI可能构成严重威胁。在我们的模拟中,由于NBTI导致的延迟增加在路径P1中几乎为11ps。

以下等式显示了设置裕度和时钟偏差对因老化而可能发生变化的各种因素的依赖性:

设置余量=时钟周期 - 数据路径延迟 - 时钟偏移 - 设置时间

时钟偏移=启动路径延迟 - 捕获路径延迟

如果启动路径的缓冲区多于捕获路径,则时间偏差将因NBTI而增加,并且设置余量将减小。由于NBTI,数据路径也会提供更多延迟,这将进一步降低设置余量并可能导致设置违规。同样,如果捕获路径具有更多缓冲区,则可能导致保持违规。这就是为什么必须在设计阶段包括老化的影响,否则它会在使用几年后导致芯片故障,这在汽车等应用中可能是灾难性的。

减少NBTI影响的措施

时钟门控检查:时钟门控后的路径应尽可能小。如果大部分路径相同,则两条路径的老化影响几乎相似,对时钟偏差的总影响将非常小。

增加边距:设计师应该采取额外保持和设置边距,具体取决于老化影响。应避免过度优化,因为它会降低工作频率。

自适应体偏置:由于NBTI的主要影响是增加PMOS晶体管的阈值电压幅度,因此正向偏置源体结可以补偿变化。使用正向体偏置进行老化所涉及的折衷是未老化的PMOS晶体管的阈值电压幅度减小,因为这会导致泄漏功率增加。

结论

在高功能频率下,NBTI在数据路径和时钟路径中引起的延迟会产生建立和保持违规。这种电路很可能在高应力老化操作期间或未来5到10年内失效。在汽车和医疗应用中,零DPM正在成为一项要求而不仅仅是一项成就,在计算时钟路径和数据路径延迟时,计算NBTI的紧密匹配不确定性已变得绝对必要。这些计算有助于实现最大可能的工作频率,而不会有任何失败的风险。

-

电源电路

+关注

关注

48文章

997浏览量

65196 -

PCB打样

+关注

关注

17文章

2968浏览量

21701 -

华强PCB

+关注

关注

8文章

1831浏览量

27750 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43038

发布评论请先 登录

相关推荐

请问零偏稳定性(bias stability)与零偏不稳定性(bias instability)指的是同一个指标吗?

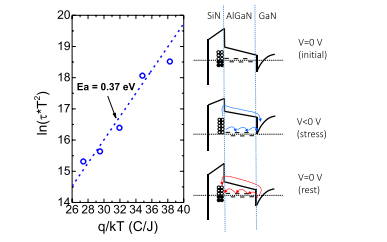

用直接隧道栅电流在线表征PMOSFET负偏压温度不稳定性

能量原理及其应用--理想磁流体(IMHD)不稳定性

不稳定性和烧录不良率很高的改善方法

Gan-ON-SI中负偏压引起的阈值电压不稳定性的论文免费下载

机器视觉检测系统的不稳定性因素有哪些

网络变压器耐压检测时的不稳定性现象

负偏压温度不稳定性对电路的影响

负偏压温度不稳定性对电路的影响

评论