得益于这两年资本市场和政策对集成电路产业的发展,今年的ISSCC也格外引人关注,最近陆陆续续在网上看到了一些大牛对于ISSCC2019上各个领域细分文章的解读,其中包括了PLL、PA、ADDA、CPU architecture等等,但对于ISSCC上占比很高的一个领域—DCDC电源类,却始终没有看到大神出来解读,可能是电源太基础太底层,不能向AI, 5G, 人工智能这些风口靠拢,但是也正因为基础,每个系统都需要电源供电,所以才更多样化的需求,正好最近囫囵吞枣地看完了这部分的slides,试着基于自己的理解做个总结,希望能起到抛砖引玉的效果。

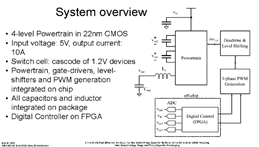

INTEL的文章这篇文章的主要特色是在22nm工艺下实现了高效率低压大电流的输出(峰值效率达到了93.8%),通过多级多相位的架构选择,提高了开关频率,从而提高了load-transient的响应速度,并减小了电感面积,同时采用片上集成电容电感缩减了供电模块所占面积。

先进工艺下能量传输所面临的挑战也是在如下几个方面进行的Trade-off : efficiency <-> size <-> transient response。这篇文章所采用的flyingcapacitor multiple converters结构,通过以下特点使DCDC的几个主要特性参数得到了优化:

1.利用flying cap,在传统BUCK的基础上加入两个FLYING开关电容,构成了混合型开拓扑(Hybird topology),并采用三相PWM控制,减少功率传输路径上单个MOS FET的压降,从而使用低压器件完成高压传输,低压器件也节约了power MOS的面积,减小了Rdson,减小了功率管栅端的寄生电容,提高了效率;

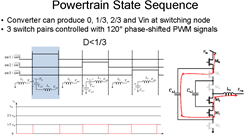

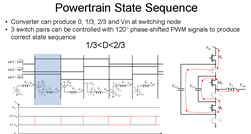

2.两个FLYING电容,三相PWM控制,SW端就有0, 1/3, 2/3, 1这四种电平的可能性,即三相四电平变换器;

3.4电平传输进一步降低了每个功率管的耐压需求,电路中将每个管子上分担的输入电压除以三,分担了每个管子上的压降;

4.6个开关管需要三个相位差为120°的,相同驱动能力的驱动信号,等效开关频率提高至之前的3倍,因此可以有效地减小所需要的电感;

三组PWM驱动和两个FLYING电容的结构选择,使得功率级开关管有多种驱动控制的组合来获得更宽的输出电压范围。上面左图为占空比D<1/3的条件下,6个phase阶段开关管M1~M6的导通状态,由上图可得,电感左侧SW端的电压为0~1/3VIN的方波,SW开关频率为控制开关频率的3倍。右图为1/3

仔细分析开关导通过程中开关管分担的压降,因为电容上电压不能突变,所以要实现上图的效果,需要保证电容Cx1上的电压为2/3Vin,Cx2上电压为1/3VIN,不知你们有没有疑惑,刚开始看的时候我其实很纳闷这个值是怎么来的,带着这个疑惑往下看,就会恍然大悟,这里会涉及多相位开关架构的一个关键威廉希尔官方网站

—FLYING电容的预充电。当由下图可得在该方案中,开关switch之前,通过在VBUS上电过程中对其检测,系统对电容Cx1和Cx2进行了预充电,并且Cx1上电压为2/3VIN, Cx2上电压为1/3VIN。当VIN<1/3*5V时,同时对两个FLYING电容充电,当1/3*5V

结合上面两图试着解读一下该方案变换器的整体架构,数字部分是基于FPGA的数字控制,个人推测应该是因为预研和验证采用FPGA比较方便,验证成功之后应该会将控制部分集成进芯片。其控制思路为,ADC采样VOUT和VIN计算出当前占空比,再与目标占空比进行比较,如果小于目标占空比,则增大当前占空比d,然后通过DAC转换去调制DLL的延时,从而生成相位差固定三路驱动的PWM波形,该波形经过level-shift转换后去驱动开关管SW1~SW6。

该文章的测试结果可得,其在3A时效率达到了93.8%,得益于高频和高环路带宽,0-6A的瞬态响应达到了Vpp=150mV。总结下这种三相位控制的混合拓扑结构,从这篇文章来看,优势是频率更高,因此瞬态响应和纹波更好,同时用低压管耐高压,减小了rds_on,从而提高了效率。同时频率的提高减小了所需的电感值,该文章采用FCCSP的方案集成了Die、电感、片外电容,进一步减小了模块在PCB上的面积,提高了集成度。

最后想总结一下该方案在电路设计时可能会遇到难点,欢迎大家补充:

1.三相位PWM控制信号的产生,DLL环路对三相信号锁频和锁相的设计;

2.控制信号转为叠管栅端驱动信号的设计,驱动电平转换的处理以及时序关系设计;

3. FLYING电容预充电时功率管耐压处理和时序关系设计;

4.高集成度封装和散热之间的trade-off;

5. 占空比变化时不同控制模式切换的过渡处理。

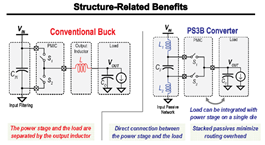

第二篇来自UCSD大学,他们的思路是通过变形的CUK converter架构实现高密度的功率集成。即将传统BUCK变换器的输出电感分成两个放在了输入端,这样做有如下优势:

1.将电感放在输入端,利用电感电流不能突变的原理,可以实现输入电流连续,这样在开关频率比较高,功率比较大的时候可以减小输入滤波器的设计难度,减小片外输入电容的取值和面积;

2.对于BUCK变换器来说,输入电流小于输出端电流,因此相比于输出电流,输入电流流过同样的电感上时由寄生DCR产生的功耗更小;

3.这种架构所实现的BUCK变换器在EMI特性、功率密度和效率方面都优于传统的变换器,另外,右二的图也说明,相比于传统BUCK,这种变换器把电感放在输入端,这样PCB上就只剩下输入滤波、PMIC、输出负载这三部分,PCB的布局方面会更有优势。

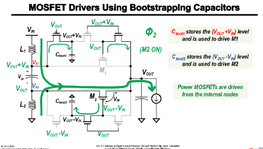

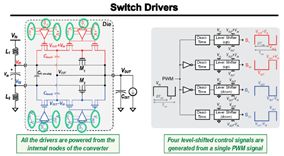

下面结合上图的原理图介绍一下这种架构的工作原理,图中,M1和M2为主功率管,在驱动相位φ1期间,M1的gate端为VOUT+VIN,M2的gate端为VOUT,M1导通,M2截止,输入电压将电容CIN两端电压充至VIN,CBOOT2两端的电压被充至VOUT-VIN,使其可以在φ2驱动M2导通;在φ2期间,M1的gate端为VOUT,M2的gate端为VOUT-VIN,M1截止,M2导通,输入电容CIN的上极板电压VX1的电位为VOUT+VIN,因此会将电容CBOOT1上电压充至VOUT+VIN,使其可以在φ1驱动M1导通。

但从这一页的原理图来说,个人认为有如下难点:

1.高端驱动和低端驱动的电源轨都不固定,需要特别去考虑和设计驱动信号的电平转换;

2.用VIN-VOUT驱动源端为VOUT的PMOS管,就决定了其占空比不能太大,文章采用的0.18um工艺,文章后面的summary里面总结可以在VIN=1.8V的条件下输入0.5V~1.5V,这一点我持怀疑态度,除非在电路中做了特殊的设计;

3.驱动电路中需要大量的隔离器件,因此在LAYOUT的时候要慎重考虑latch up、noise方面的影响。

总体而言,这篇文章是本次ISSCC会议上DC-DC session里极具创新的一篇文章,不同于INTEL那篇,这篇文章在0.18um的工艺下实现,同时给出了功率管驱动耐压和驱动电平转换的解决方案,并且也从工业界的应用角度考虑了将BUCK的输出电感拆分成两个放在输入端对于PMU整体面积和效率产生的影响和对比。相比于今年来比较火的10mA~100mA功率段的SC converter,这篇文章给出了大电流下(2.5A)高功率密度集成的PMU解决方案,未来应该会有很广阔的应用市场。

ADI的文章第三篇想介绍的是来自ADI的一篇文章。近几年来,随着汽车充电器和移动电源的市场越来越大,BUCK-BOOST架构的升降压电源在业界应用变得很火。

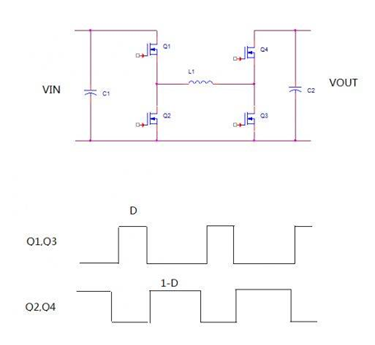

传统的四开关Buck-Boost电路,Vo=Vin*D/(1-D),输出电压的极性与输入电压相同。如下图,

如上图所示,Q1和Q3同时工作,Q2和Q4同时工作,并且两组MOS交替导通。对于这种控制方式,在CCM情况下我们可以得到公式:

VIN×D=VOUT ×(1-D)

这个电压转换比和我们常见的buck-boost是一样的,这种控制方式的优点是控制方式简单,没有模态切换。但是缺点是,四个管子都在一直工作,损耗大,共模噪音也大。

ADI的这篇文章就是针对传统BUCK-BOOST四个开关管轮流导通共模噪声大的痛点,提出了更优的控制方式和模式切换方案。

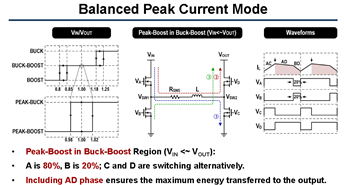

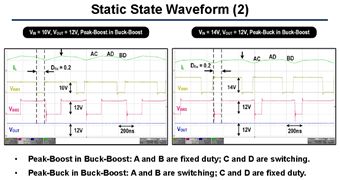

其思路就是当Vin>>Vout的时候,SC管常关,SD管常开,把这个拓扑当纯粹的BUCK来用,当Vin<

本文的思路是,在VIN>>VOUT,即BUCK工作模式下,当VOUT逐渐升高,占空比逐渐增大至80%时,VIN≥VOUT,开关管SC和SD不再常开或者常关,其也会导通从而切换至BOOST/BUCK模式,即前半周期为BOOST模式,后半周期为BUCK模式。同理,在VIN<

不知道大家有没有这样的疑问?在占空比比较接近时芯片还是工作在BUCK-BOOST模式,那么是不是在这种条件下,共模噪声的问题就不会有很大改善?这个问题我是这么理解的,如果全程在BUCK-BOOST模式下,四个开关管SA/SC,SB/SD轮流导通,那么电感两端在整个周期内的都有VIN/VOUT的电压差,会产生较大的dv/dt干扰,如果采用这篇文章所提的控制模式,那么芯片控制方式在BUCK和BOOST之间切换,其EMI特性与单独的BUCK芯片或BOOST芯片接近,产生的EMI干扰会远远小于BUCK-BOOST的工作模式。

本次会议DC-DCconverters部分收录了8篇文章,总体的发展趋势是向着高效率,高能量密度的方向,各路大神对于新的拓扑架构进行了的多样化探索。特别可以看出,对于大功率的应用,混合型(Hybrid)拓扑在效率方面更具有优势,而对于中小型功率(Io=10mA~100mA)的需求,SC Converter因为其高能量密度(PD)的特点,得到了学术界的火热探索。个人认为,之后DC-DC Converter领域内,不会再像之前那样,被电压模/电流模拓扑一统天下,而是会根据应用的不同,在架构方面出现百花争艳的局面,之前的DC-DC 在trade-off设计时可能做到没有短板就行了,而之后的设计,更多的是在此基础上对个别进行极限的挑战。比如低噪声、低EMI、高效率、高能量密度、快速瞬态响应、高PSRR等待,每一个性能可能都需要从架构上做优化。这里面的挑战和乐趣可能会颠覆很多人对于DC-DC Converter门槛低、架构固化、新的挑战少的观点。所以,不管在企业做产品还是在高校做学术研究,还是有很多东西可以做的。

因为最近太懒工作太忙,将这8篇囫囵吞枣地过了一遍之后,挑了自己觉得比较精彩的三篇做个简单分享,其中可能有很多不妥或者考虑不够深入之处,欢迎各位同仁拍砖过来一起探讨。

-

电路

+关注

关注

172文章

5907浏览量

172211 -

MOS

+关注

关注

32文章

1269浏览量

93720 -

Buck-Boost

+关注

关注

4文章

74浏览量

19553

原文标题:ISSCC2019 DC-DC converter浅析

文章出处:【微信号:yaliDV,微信公众号:模拟混合信号设计验证】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

联电宣布22nm威廉希尔官方网站 就绪

透视IVB核芯 22nm工艺3D威廉希尔官方网站 终极揭秘

功率和成本减半 Achronix交付先进22nm Speedster22i 系列FPGAs

22nm平面工艺流程介绍

22nm工艺下如何实现高效率低压大电流输出

22nm工艺下如何实现高效率低压大电流输出

评论