本文将对源同步定时如何优化高速接口时序裕量进行讨论。时序预算是对系统正常工作所需时序参数或时序要求的计算。

2012-03-20 10:46:32 2444

2444

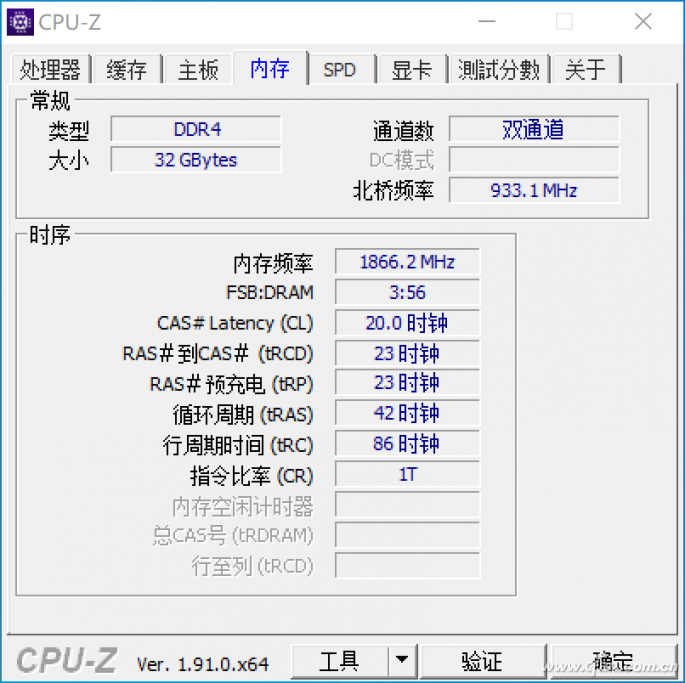

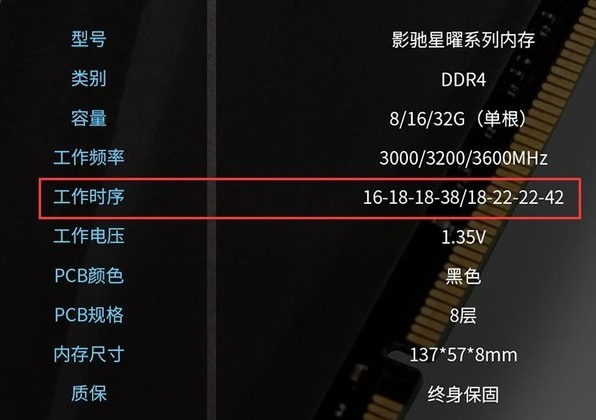

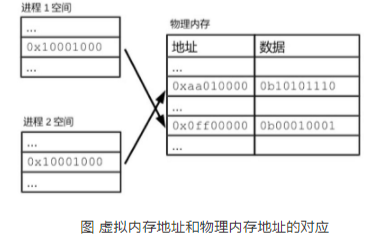

很多小伙伴都知道在挑选内存的时候不光要看频率,还要看时序,或者叫延迟。也就是经常标注在内存表面,在测试软件中也能看到的那些中间的带短线连接的两位数。不过要问它们到底具体代表什么意思,相信很多小伙伴

2020-08-12 16:24:10 3616

3616

时序路径 典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。 对于所有的时序路径,我们都要明确其起点和终点,这4类时序路径的起点和终点分别如下

2020-11-17 16:41:52 2768

2768

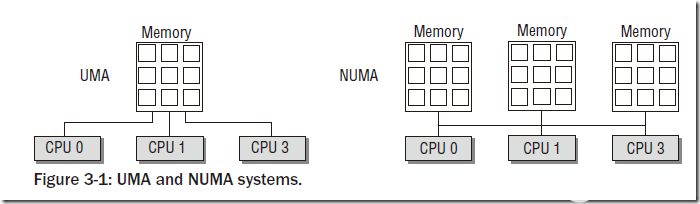

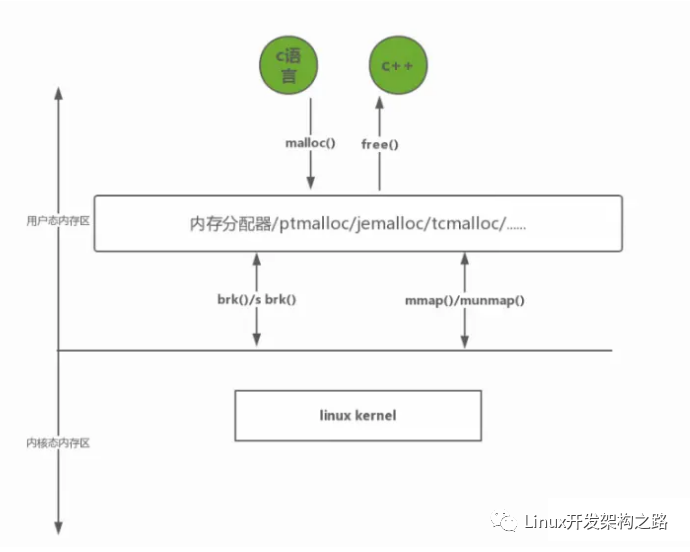

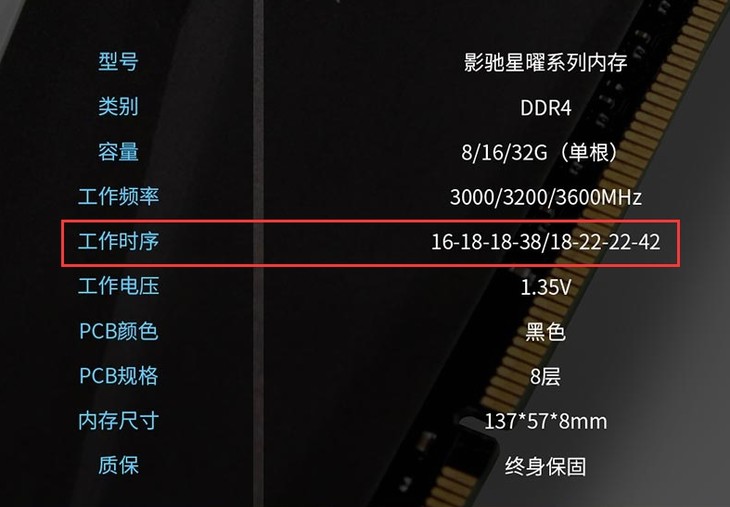

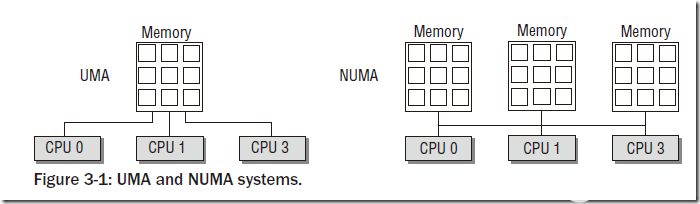

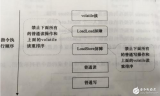

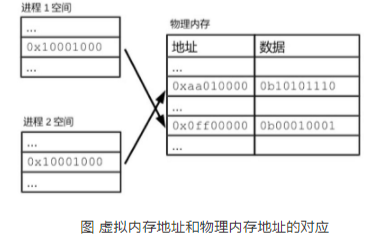

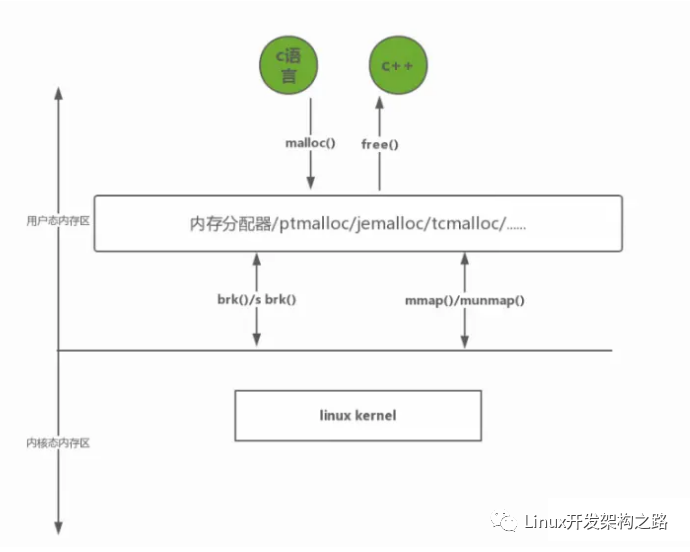

Linux的内存管理 Linux的内存管理是一个非常复杂的过程,主要分成两个大的部分:内核的内存管理和进程虚拟内存。内核的内存管理是Linux内存管理的核心,所以我们先对内核的内存管理进行简介

2022-05-11 17:54:17 5183

5183

同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最坏情况下满足时序要求,我们需要进行静态时序分析,即不依赖于测试向量和动态仿真,而只根据每个逻辑门的最大延迟来检查所有可能的时序违规路径。

2023-06-28 09:35:37 490

490

的工作原理 DDR芯片内存的工作原理可以分为两部分, 一部分是时序,一部分是数据传输 。 控制DDR内存的时序,是由内存控制器控制的,它负责管理内存的读写操作。内存控制器会向DDR内存发送时钟信号,这个时钟信号被称为 系统时钟 。 DDR内存的数据传输,是通过前沿和下降沿来实现的

2023-07-28 13:12:06 1891

1891

时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50:02 452

452

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 842

842

OCXO在时序中提供了顶级性能,是所有通信网络可靠运行的关键。和5G之前OCXO基本被部署在良好受控的环境中不同,5G时代的计算、核心网络和无线电都将被整合到一个系统内并有可能被部署到诸如塔楼、屋顶或灯柱等非受控环境中,这种变化将使得系统设计对MEMS时序威廉希尔官方网站

和石英时序威廉希尔官方网站

的各自优势重新进行评估。

2018-11-05 09:15:09 1999

1999 内存时序究竟有多重要呢?究竟该如何去选择内存条呢?DDR内存时序是高一些好还是低一些好?

2021-06-18 08:20:11

目录片选引脚CS内存控制器是否需要我们手动设置片选引脚?内存控制器是如何知道地址对应哪个片选引脚呢?内存的计算读写位宽不同位宽外设的接线方式16位32位接线总结如何确定访问地址内存控制器的时序

2022-01-12 07:59:10

内存的原理和时序,学习哦!

2016-01-04 10:16:06

什么是内存呢?内存的工作原理是什么?内存(RAM或ROM)和FLASH存储有哪些区别呢?

2021-11-09 06:11:02

什么是中断?为什么CPU要用时序电路?时序电路与普通逻辑电路有什么区别呢?

2021-10-29 07:03:45

CPLD有内存这一说吗?例如51单片机有4K的内存。如果有,内存都有多大的?如果没有,是否是根据使用了多少相应的逻辑资源的情况来判断的?

2023-04-23 14:32:37

如图Labview性能和内存信息能看出来内存泄露吗?如上图,未命名1.vi是否存在内存泄露?

补充内容 (2016-2-23 21:03):

Labview自带的工具能检查出内存泄露吗?

2016-02-23 14:33:55

Authentication Code (PAC)一起使用,来减少允许攻击者控制栈指针的gadget存在的可能性。MTE和内存安全MTE实现对内存访问的lock和key。lock可以设置在内存上,在内存访问时提供key

2022-08-22 15:28:28

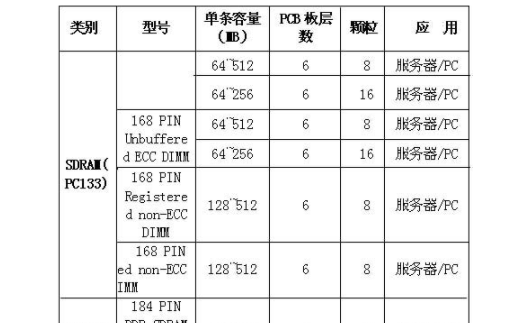

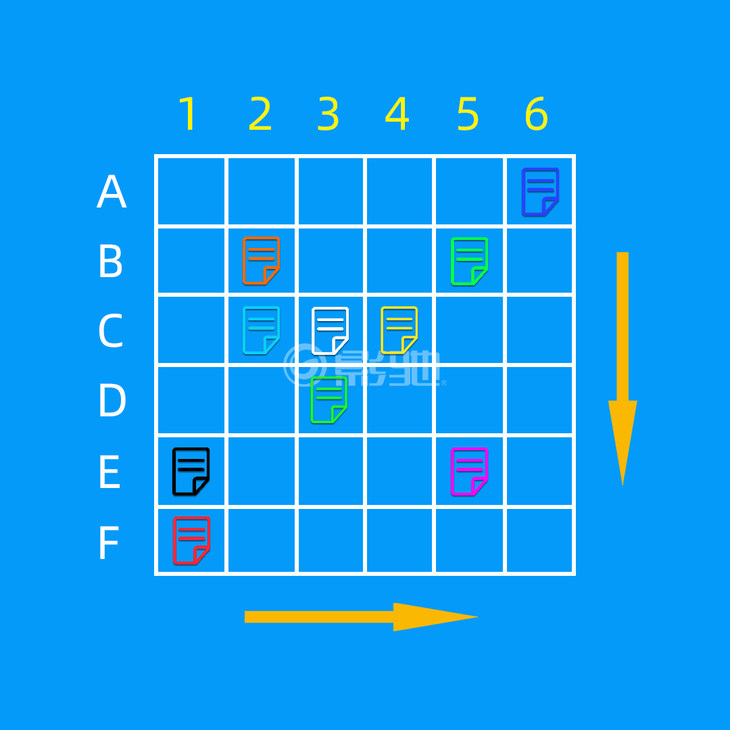

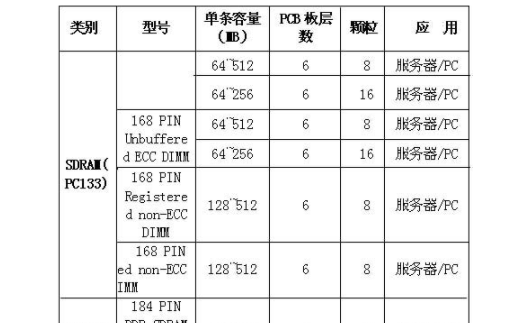

Card被分为A-F六个版本,各个版本之间的差异在表格中可以清楚看出来。差异主要在:条上内存颗粒数量、内存颗粒的位宽、内存条的Rank。这个版本的意思其实是内存条的不同组织形式,每个版本的特征与将来PCB布局布线、和内存条的频率时序都有关系,设计之初就要确定好。

2019-05-28 07:28:13

的,应注意主板支持的最大参数,内存条的性能/大小超过该参数将造成浪费。内存注意内存条接口看一下你的主板的内存条接口是什么,别使用DDR4内存条的主板结果图便宜买了个DDR3的内存条,那可是用不了的。内存条的时序其实不用管什么时序,自己用的话时序多少都差不多,无需特别注重。内存条的品牌其实

2021-12-29 07:07:22

剖析决定内存性能强弱的因素1. 内存芯片 内存条最重要的部件就是芯片了,它的好坏对整个内存模组的影响几乎是举足轻重的。由于建造内存晶圆厂需要花费数十亿美元巨资,加上生产制程非常精密,所以目前

2011-02-24 17:28:35

嵌入式系统中对内存分配有什么要求?静态分配与动态分配有何不同?一次分配多次使用的内存分配方案有什么特点?

2021-04-27 06:01:50

监控内存空间大小,当小于某个值时可以提示信息,求助,谢谢

2013-09-21 20:37:43

nRF24L01+ 2.4GHz无线收发器的主要特性有哪些?如何使用SPI?如何对SPI的操作时序进行读写呢?

2021-12-20 06:32:33

本文利用C-NOVA公司数字电视MPEG-2解码芯片AVIA9700内置的SDRAM控制器所提供的时序补偿机制,设计了一个方便使用的内存时序测试软件工具,利用这个工具,开发测试人员可在以AVIA9700为解码器的数字电视接收机设计和生产中进行快速诊断,并解决SDRAM的时序问题。

2021-06-07 06:19:01

内存对整机的性能有什么影响?影响内存性能的主要指标有哪些呢?

2021-06-18 08:05:22

DVD-ROM标签中,可以直接调节系统用多少内存作为DVD-ROM光盘读写的高速缓存。 2.监视内存 系统的内存不管有多大,总是会用完的。虽然有虚拟内存,但由于硬盘的读写速度无法与内存的速度相比

2011-02-24 17:29:38

1、时序不同也就是响应时间不同,单位为时钟周期。2、性能不同其他条件相同的情况下,数字越小性能越好。3、价格不同其他条件相同的情况下,数字越小价格越高。4、颗粒不同内存中使用的颗粒不同,数字越小颗粒

2021-07-29 07:24:59

最近在使用Nordic的最新蓝牙芯片nRF52832开发过程中,因为做一些测试涉及到对内存地址的操作,有(*(volatil...

2022-02-28 07:05:54

内存申请接口返回的内存可以直接使用, 正确性由操作系统/平台来保证,没必要判断返回结果。答案:错误在嵌入式系统中,由于没有虚拟内存的概念,内存申请不一定成功,如果不对申请内存的返回值进行判断,会出现对无效指针的操作。...

2021-12-17 06:30:46

我是一个FPGA初学者,关于时序约束一直不是很明白,时序约束有什么用呢?我只会全局时钟的时序约束,如何进行其他时序约束呢?时序约束分为哪几类呢?不同时序约束的目的?

2012-07-04 09:45:37

干下来,发现方法总比困难多,有一种太极生两仪,两仪生四象,四象生八卦,八卦生万物的赶脚。借用三十六计来总结,一点也不夸张。怎么说呢?时序的本质就是delay的控制,控制在setup和hold都满足

2020-12-10 07:37:31

影响内存的关键因素是哪些?频率和时序,你是否真的了解呢?时序与频率有什么区别?哪个对内存性能影响大?

2021-06-18 07:15:39

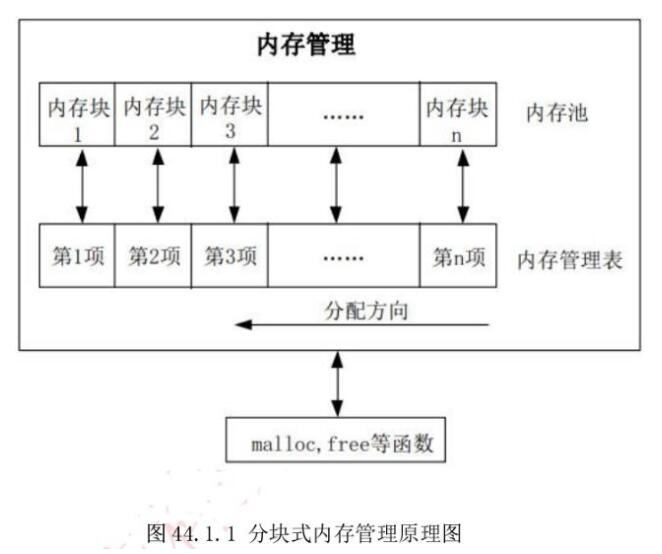

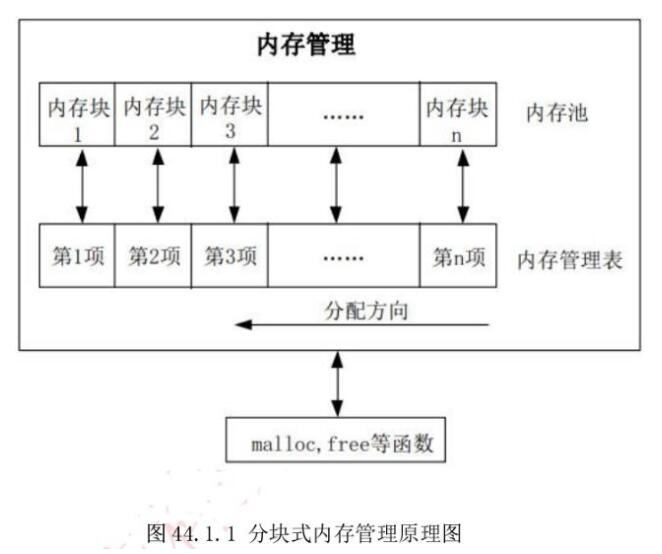

通过对内存管理的分析,提出了内存优化算法。该算法解决了通信设备中由于大量消息的发送导致内存管理的问题,建立了用户定义的内存管理区域,设计了新的内存管理队列,

2009-02-21 11:42:35 22

22 SDRAM的原理和时序

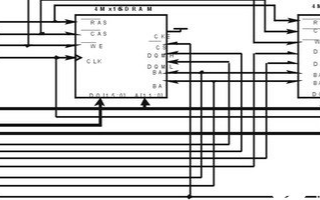

SDRAM内存模组与基本结构 我们平时看到的SDRAM都是以模组形式出现,为什么要做成这种形式呢?这首先要接触到两个概念:物理Bank与芯片位宽

2010-03-11 14:43:26 167

167 时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 如何提高内存稳定性

问:在升级内存、对内存做了优化设置之后,我感觉系统有些不稳定,主要表现为长时间下载偶尔会死

2010-02-25 11:35:11 1541

1541 CPU时序

2016-12-15 22:15:22 1

1 基于时序路径的FPGA时序分析威廉希尔官方网站

研究_周珊

2017-01-03 17:41:58 2

2 小技巧和帮助来设置时钟;使用像Synopsys Synplify Premier一样的工具正确地设置时序约束;然后调整参数使之满足赛灵思FPGA设计性能的目标。 会有来自不同角度的挑战,包括: •更好的设计计划,例如完整的和精确的时序约束和时钟规范 •节约时间的

2017-02-09 01:59:11 264

264 内存是CPU与硬盘之间的桥梁。高性能CPU、SSD,依赖内存的高性能表现。而影响内存性能最直接的因素---“频率”!原则上,频率越高,内存性能越强。(当然,这也不是绝对的,内存时序也有影响)。

2017-07-04 09:32:50 1567

1567 时序图是描述设备工作过程的时间次序图,也是用于直观分析设备工作过程的一种图形。如电子威廉希尔官方网站

中的触发器、定时器、计数器等均用时序图来描述其工作原理。在plc顺序控制设计法编制梯形图程序时往往是先画出时序

2017-10-23 08:40:45 84666

84666

内存屏障,也称内存栅栏,内存栅障,屏障指令等, 是一类同步屏障指令,是CPU或编译器在对内存随机访问的操作中的一个同步点,使得此点之前的所有读写操作都执行后才可以开始执行此点之后的操作。

2017-11-14 09:43:44 6190

6190

现有的工具和威廉希尔官方网站

可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而优化设计的能力,还取决于设计人员指定前方目标,诊断并隔离下游时序问题的能力。

2017-11-18 04:32:34 2951

2951 时序图在有些教材上,又被翻译为顺序图,两者在表述上虽然有一些差别,但是大体都是准确的,可能称之为时序图会更加书面语话,听起来高大上的感觉。其实是一样的,重在理解,个人偏向于时序图,也就是时间顺序的意思。

2017-12-11 19:31:03 165730

165730

传统的基于模拟退火的现场可编程门阵列( FPGA)时序驱动布局算法在时延代价的计算上存在一定误差,已有的时序优化算法能够改善布局质量,但增加了时耗。针对上述问题,提出一种基于事务内存( TM)的并行

2018-02-26 10:09:04 0

0 FPGA时序收敛让你的产品达到最佳性能!

2018-04-10 11:38:48 18

18 本文利用C-NOVA公司数字电视MPEG-2解码芯片AVIA9700内置的SDRAM控制器所提供的时序补偿机制,设计了一个方便使用的内存时序测试软件工具,利用这个工具,开发测试人员可在以AVIA9700为解码器的数字电视接收机设计和生产中进行快速诊断,并解决SDRAM的时序问题。

2020-03-13 07:59:00 1596

1596

组合电路和时序电路是计算机原理的基础课,组合电路描述的是单一的函数功能,函数输出只与当前的函数输入相关;时序电路则引入了时间维度,时序电路在通电的情况下,能够保持状态,电路的输出不仅与当前的输入有关,而且与前一时刻的电路状态相关,如我们个人PC中的内存和CPU中的寄存器,均为时序电路。

2018-09-25 09:50:00 24779

24779 通常来说,为了保证内存条的使用稳定性和兼容性,内存直接插到主板上都是以JEDEC标准上的基础频率和时序运行,但是对于最求极致游戏性能的玩家来说,高频内存是必不可少的。

2018-10-17 16:18:02 9617

9617 根据西部数据官方的消息,西数发布了新款Ultrastar® DC ME200 内存扩展固态盘,可优化内存系统容量/性能,从而运行对内存有着高要求的应用,满足当今实时分析和业务洞察的需求。

2018-11-14 17:02:38 970

970 游戏玩家装机首先看显卡,其次看处理器,这两个部件是影响游戏性能最关键的。在处理器、显卡之外呢?内存也很重要,要考虑频率、时序以及容量,理论上频率越高、容量越大当然是越好了,但还是要考虑到现实合理性

2018-12-25 14:53:42 4692

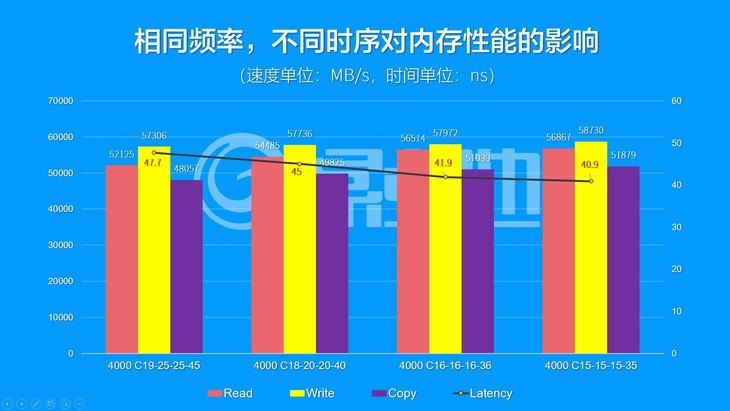

4692 最近是跟内存耗上了,其一是手里没有其它硬件可测,更重要的是想趁着这段时间,把内存与性能之间的影响都慢慢测一下。今天测的就是时序与内存性能之间的关系了。时序很重要吗?答案是肯定的,但是时序对内存性能的影响到底有多大呢?下面就详细的测试一下。

2019-01-14 15:09:13 23311

23311 在PC领域,一直以来内存都是计算机中重要的组成部件,在我们日常使用过程中,内存起到与CPU沟通,并保证程序的正常运行,可以说内存的“性能”对计算机的影响非常大。

2019-02-20 10:50:45 10477

10477

本文档的主要内容详细介绍的是C51中两种对内存空间地址写数据的方法说明。

2019-08-01 17:34:00 1

1 为提高带宽,很多类型的 Memory 都采用了 Double Data Rate(DDR)interface,它对在内存控制器(memory controller)设计过程中的时序收敛和后仿真提出了挑战。

2019-08-03 10:36:40 3356

3356 电脑内存不足怎么办,虚拟内存能起到多大作用?我们可以看到下图网友反映"电脑内存有12GB内存,但是玩大型游戏的时候,经常弹出内存不足的窗口,导致游戏经常崩溃"。

2019-08-23 16:39:52 1982

1982 三星B-die颗粒的内存条,能够保持较低的时序,运行3866-4266MHz或更高频率,兼容性和超频性能深受电脑发烧友们的喜爱。

2019-09-26 11:17:40 4133

4133 32位系统支持多大内存呢?有些朋友在重装系统时就比较纠结了,32位系统与64位系统哪一个更适合自己的电脑呢?系统位数的选择你不仅与电脑位数有关,内存也占据着重要地位。接下来,我就带大家了解一下32位系统支持多大的内存

2019-10-26 12:08:36 37428

37428 内存管理,是指软件运行时对计算机内存资源的分配和使用的威廉希尔官方网站

。其最主要的目的是如何高效,快速的分配,并且在适当的时候释放和回收内存资源。前面我们有介绍过如何使用FSMC外扩SRAM,实现内存容量的扩展

2019-11-02 10:04:03 17424

17424

很多用户购买内存,往往会把主要的关注度,集中在内存容量、频率、时序、价格,甚至灯效、外观等方面,却很少有人会留意到【内存的兼容性】。但是我想说,买内存最大的坑,莫过于内存与主板的兼容性。

2019-11-08 15:37:07 3826

3826 近日,技嘉推出了Designare DDR4-3200 64GB套条,由2条单条32GB内存组成。Designare内存开启XMP之后,它能在3200MHz频率达成18-18-18-38的时序,远远

2020-02-06 14:11:09 2722

2722 目前,英特尔的十代酷睿处理器采用了全新的内存控制器,提高了对内存频率的支持,支持LPDDR4-3733MHz内存以及DDR4-3200MHz内存(前者用于移动端,后者用于桌面端),这对提升专业应用以及游戏的加载速度都有帮助。

2020-04-12 10:50:19 7277

7277 内存是电脑必不可少的组成部分,CPU可通过数据总线对内存寻址。历史上的电脑主板上有主内存,内存条是主内存的扩展。以后的电脑主板上没有主内存,CPU完全依赖内存条。所有外存上的内容必须通过内存才能发挥作用。

2020-06-09 10:44:34 6373

6373 内存超频有一定几率损坏内存。内存超频涉及到修改内存的电压、主频、时序等内容,如果内存体质不佳且修改的范围超过了内存能够承受的上限,内存很容易因此而烧坏。即便超频的内存能够点亮并且通过压力测试,但也容易加速内存寿命老化。以下是对内存超频的详细说明:

2020-06-15 10:38:44 9092

9092 这些数字表示延迟,也就是内存的反应时间。当内存接收到CPU发来的指令后,通常需要几个时钟周期来处理它,比如访问某一块数据。所以,时间越短,内存性能越好。

2020-09-03 16:29:46 4445

4445

更为具体的时序报告信息如何从中获取,或者如何根据时序报告发现导致时序违例的潜在原因呢?

2020-09-04 10:24:29 1607

1607 静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯片的时序进行约束,然后通过时序分析工具给出

2020-11-11 08:00:00 58

58 内存是电脑以及其它相关设备的重要组成,缺少内存,电脑的处理结果将无法保存。在往期文章中,小编对内存的基本知识有所介绍。为增进大家对内存的认识,本文将对服务器内存予以介绍。如果你对内存或者内存相关知识具有兴趣,不妨继续往下阅读哦。

2020-12-06 17:43:00 2468

2468

我们每天都在同内存打交道,但大家对内存真的了解吗?上篇文章中,我们对服务器内存以及服务器内存威廉希尔官方网站

有所介绍,为增进大家对内存的认识,本文将为大家介绍高频率内存的优势。此外,小编还将对虚拟内存加以探讨。如果你对内存及其相关知识具有兴趣,不妨继续往下阅读哦。

2020-12-06 17:43:00 5856

5856

内存是重要器件之一,很多厂商致力于生产高性能内存。但是,大家对电脑内存的作用真的了解吗?如果你对内存作用存在疑惑,本文即可为您解惑。此外,本文还将对内存适用类型予以探讨。小编相信,通过本文对内存的介绍,大家必定可以增进对内存的认识。那么,和小编共同往下阅读吧。

2021-01-03 17:32:00 3671

3671 完成本模块后,您应该对内存测试和内存BIST概念。

2021-03-26 10:48:03 8

8 的,应注意主板支持的最大参数,内存条的性能/大小超过该参数将造成浪费。内存注意内存条接口看一下你的主板的内存条接口是什么,别使用DDR4内存条的主板结果图便宜买了个DDR3的内存条,那可是用不了的。内存条的时序其实不用管什么时序,自己用的话时序多少都差不多,无需特别注重。内存条的品牌其实

2022-01-06 15:34:12 10

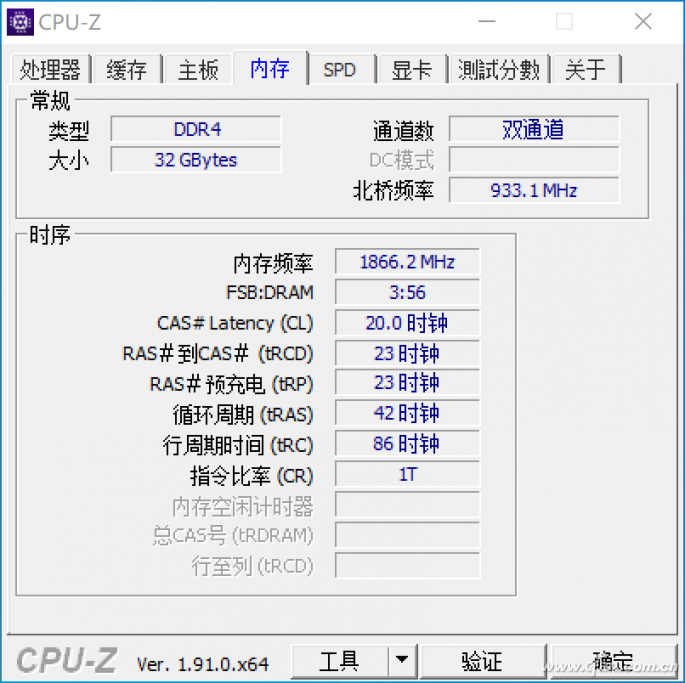

10 内存时序是描述内存条性能的一种参数,一般存储在内存条的SPD中。内存时序和我们的内存频率一样,同样代表了一款内存性能的高低。一般数字“A-B-C-D”分别对应的参数是“CL-tRCD-tRP-tRAS”。

2022-02-06 12:57:00 15256

15256 本文介绍了在低功耗系统中降低功耗同时保持测量和监控应用所需的精度的时序因素和解决方案。它解释了当所选ADC是逐次逼近寄存器(SAR)ADC时影响时序的因素。对于Σ-Δ(∑-Δ)架构,时序考虑因素有所不同(请参阅本系列文章的第1部分)。本文探讨了模拟前端时序、ADC时序和数字接口时序中的信号链考虑因素。

2022-12-13 11:20:18 1057

1057

引言 在同步电路设计中,时序是一个非常重要的因素,它决定了电路能否以预期的时钟速率运行。为了验证电路的时序性能,我们需要进行 静态时序分析 ,即 在最坏情况下检查所有可能的时序违规路径,而不需要测试

2023-06-28 09:38:57 714

714

本文主要介绍了时序设计和时序约束。

2023-07-04 14:43:52 694

694 本文继续讲解时序约束的第四大步骤——时序例外

2023-07-11 17:17:37 417

417

时序约束出现时序违例(Slack为负数),如何处理?

2023-07-10 15:47:06 3098

3098 今天主要介绍的时序概念是时序库lib,全称liberty library format(以• lib结尾),

2023-07-07 17:15:00 1645

1645

时序:字面意思,时序就是时间顺序,实际上在通信中时序就是通信线上按照时间顺序发生的电平变化,以及这些变化对通信的意义就叫时序。

2023-07-26 10:06:03 1644

1644 8月10日, 三星半导体在本次第五届OCP China Day 2023(开放计算中国威廉希尔官方网站

峰会)上分享了两大应对内存墙限制的创新威廉希尔官方网站

解决方案和开放协作的业务战略。

2023-08-10 14:16:26 685

685 电源时序器有稳压功能吗?电源时序器是干什么用的? 电源时序器并不一定有稳压功能,但是在某些情况下,电源时序器可以具有这种功能。 首先,让我们来了解一下电源时序器是什么以及它的作用。简单来说,电源时序

2023-10-16 16:16:27 1862

1862 SDRAM的结构、时序与性能的关系

2022-12-30 09:20:51 1

1 1. 内存管理功能问题 由于C++语言对内存有主动控制权,内存使用灵活和效率高,但代价是不小心使用就会导致以下内存错误: • memory overrun:写内存越界 • double free

2023-11-10 15:29:11 578

578

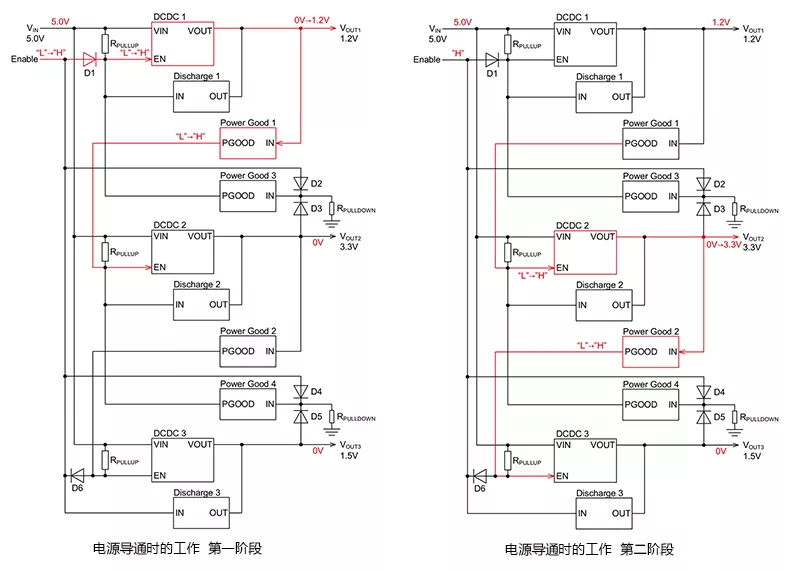

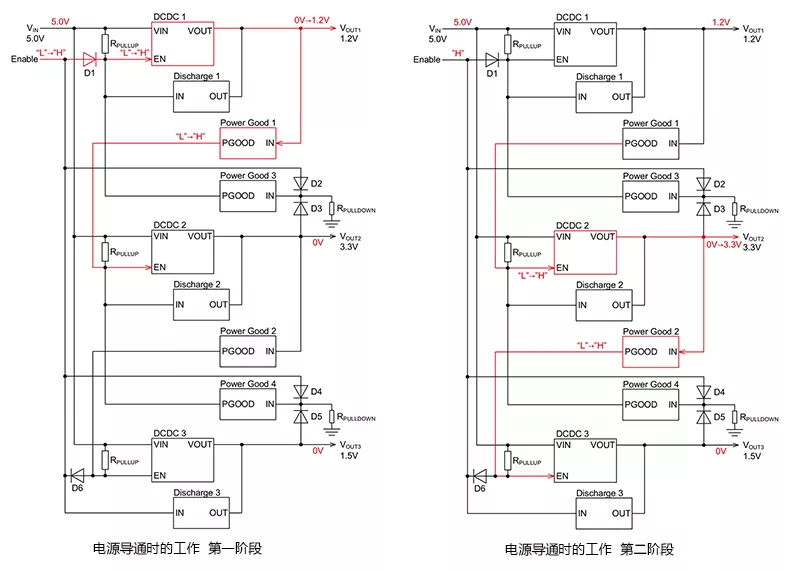

电源时序规格:电源导通时的时序工作

2023-12-08 18:21:43 326

326

电子发烧友网站提供《磁隔离对延迟时序性能的改善.pdf》资料免费下载

2023-11-27 09:44:05 0

0 LPDDR5和DDR5是两种不同类型的内存,它们在时序和性能方面有一些差异。尽管它们都是最新一代的内存标准,但它们面向不同的应用场景,并且在设计上有一些不同。 首先,让我们来了解一下LPDDR5

2024-01-04 10:22:06 1166

1166 DDR6和DDR5内存的区别有多大?怎么选择更好? DDR6和DDR5是两种不同的内存威廉希尔官方网站

,它们各自在性能、功耗、带宽等方面都有不同的特点。下面将详细比较这两种内存威廉希尔官方网站

,以帮助你选择更适合

2024-01-12 16:43:05 2881

2881 站群服务器的内存需求取决于网站的数量和流量,以及服务器需要运行的应用和服务。RAKsmart小编为您整理发布站群服务器需要多大内存以及站群服务器内存需求的考虑因素。

2024-03-04 09:48:08 131

131

电子发烧友App

电子发烧友App

评论