基于AES算法硬件优化及IP核应用

大小:0.90 MB 人气: 2017-11-02 需要积分:1

标签:AES(33108)

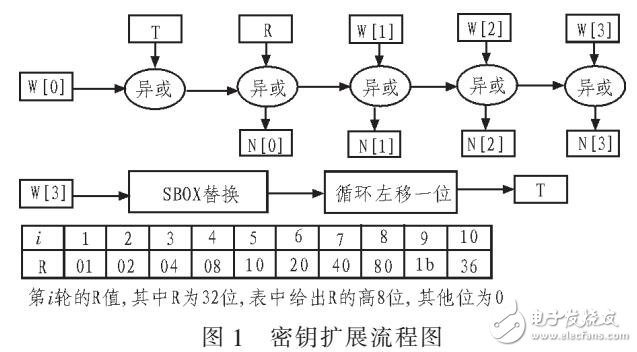

根据AES算法的特点,从3方面对算法硬件实现进行改进:列混合部分使用查找表代替矩阵变换,降低算法实现的运算复杂度,采用流水线结构优化关键路径一密钥拓展,提升加密速度,利用FPGA定制RAM (BRAM)预存查找表进一步提升加密速度。优化后的AES算法在Virtex -6xc6vlx240T(速度等级-3)FPGA上实现,结果发现,AES算法共占用1 139个Slice,最大频率达到443.99 MHz,通量达到56.83 Gbit/s,效率达到49.89 (Mbit/s)/Slice;然后,对AES算法进行接口逻辑声明,将优化后AES算法封装成自定制IP核;最后,采用基于NIOS II的SOPC威廉希尔官方网站 ,构建了一个嵌入式AES算法加密系统,实现了数据通信中的高速加密。

非常好我支持^.^

(0) 0%

不好我反对

(0) 0%

下载地址

基于AES算法硬件优化及IP核应用下载

相关电子资料下载

- 安科瑞用电精灵AESP100--末端多回路智慧用电监控装置 153

- 安科瑞AESP110-2P配电箱多回路智慧用电监测 110

- 基于FPGA的AES256光纤加密设计案例实现 1035

- Molex荣获UAES联合电子“供应商最佳商务合作奖” 279

- 亚马逊推出个性化AI歌单功能Maestro,进军音乐市场 418

- AES加密协议是什么?AES加密协议的应用 403

- 国芯科技近日成功推出了新一代指纹芯片CCM4101 593

- 俄歇电子能谱分析威廉希尔官方网站 150

- 微星新款MEG MAESTRO 700L PZ"海神"机箱,搭载270°整片式曲面钢化玻璃 241

- 韩国上市PCB企业Haesung DS公布2023年的财报数据:下跌49.9% 757