一、半导体封装威廉希尔官方网站 简介

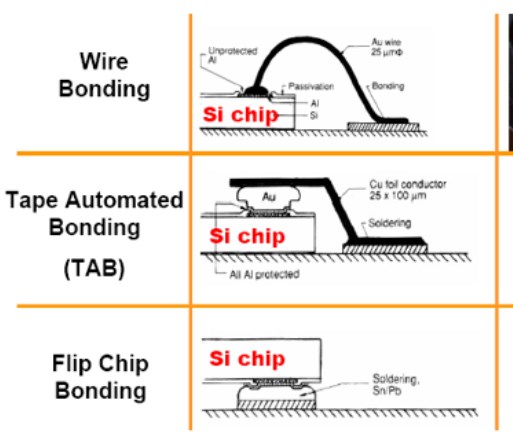

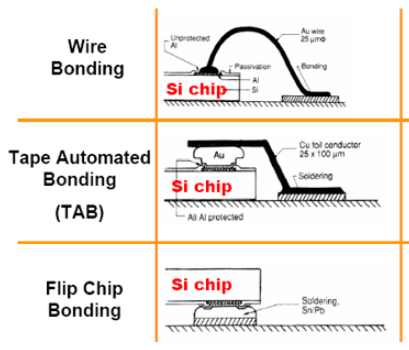

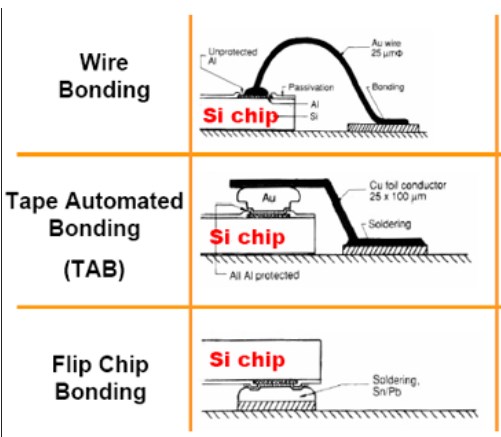

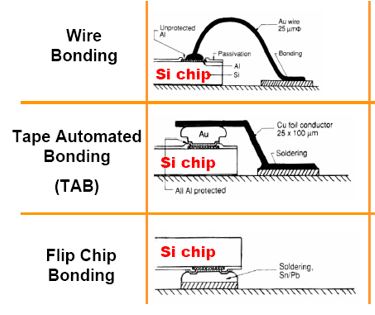

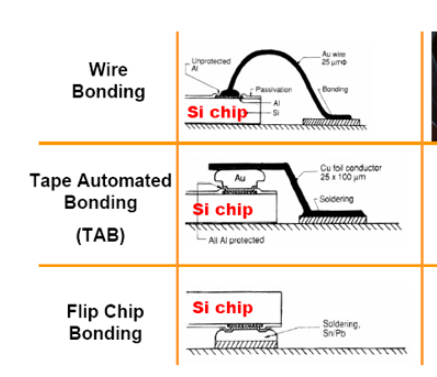

从事半导体行业,尤其是半导体封装行业的人,总绕不开几种封装工艺,那就是芯片粘接、引线键合、倒装连接威廉希尔官方网站 。

尤其以引线键合(Wire Bonding)及倒装连接(Flip Chip Bonding)最为常见,因为载带连接威廉希尔官方网站 (TAB)有一定的局限性,封装上逐渐淘汰了这种威廉希尔官方网站 。

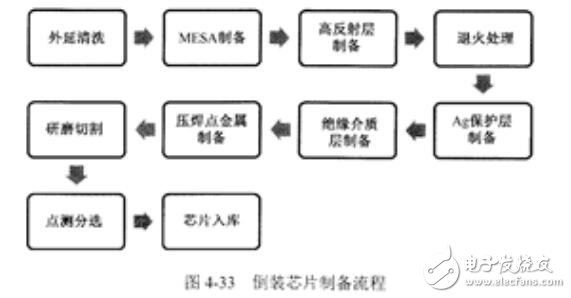

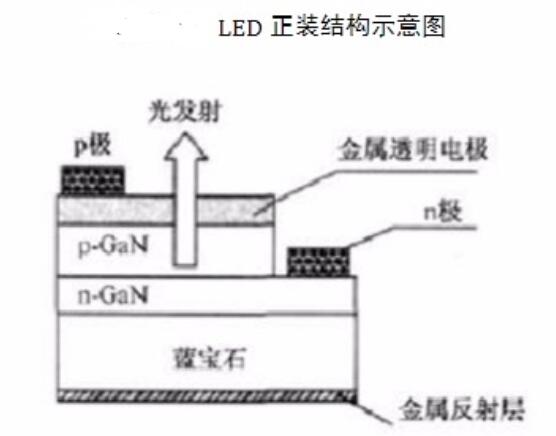

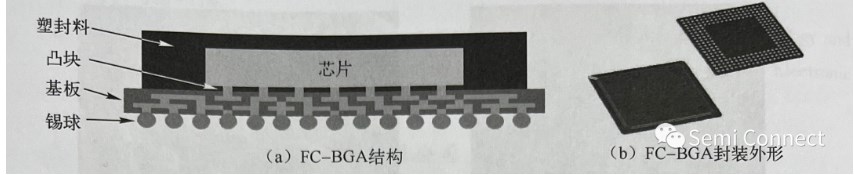

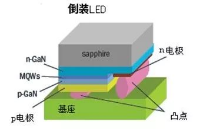

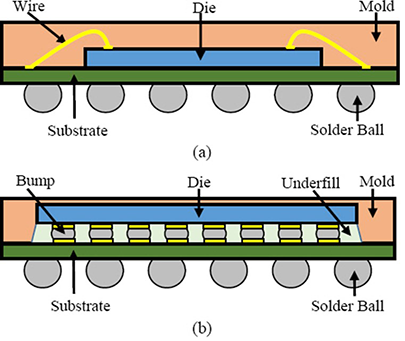

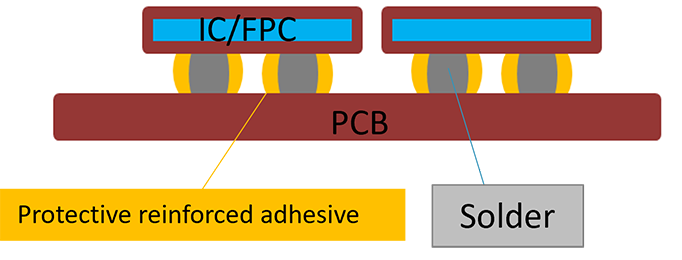

倒装芯片威廉希尔官方网站 是通过芯片上的凸点直接将元器件朝下互连到基板、载体或者电路板上。引线键合的连接方式是将芯片的正面朝上,通过引线(通常是金线)将芯片与线路板连接。

引线键合、载带连接、倒装连接各有特点。其中倒装连接以结构紧凑,可靠性高在封装william hill官网 越来越广泛。

二、什么是倒装芯片威廉希尔官方网站 ?

倒装芯片威廉希尔官方网站 起源于IBM,IBM公司在1960年研制开发出在芯片上制作凸点的倒装芯片焊接工艺。以95Pb5Sn凸点包围着电镀NiAu的凸球。后来制作PbSn凸点,使用可控塌焊连接(Controlled collapse Component Connection, 简称C4威廉希尔官方网站 ),该威廉希尔官方网站 最初为自己的大型计算机主机所开发的一种高可靠的封装威廉希尔官方网站 。C4芯片具有优良的电学、热学性能,封装疲劳寿命至少提高10倍以上。

自从IBM研制并成功应用C4威廉希尔官方网站 后,随后的威廉希尔官方网站 发展中,一些半导体公司又对C4威廉希尔官方网站 进行了优化升级,其中包括Fairchild公司研制了Al凸点,Amelco公司研制了Au凸点威廉希尔官方网站 。

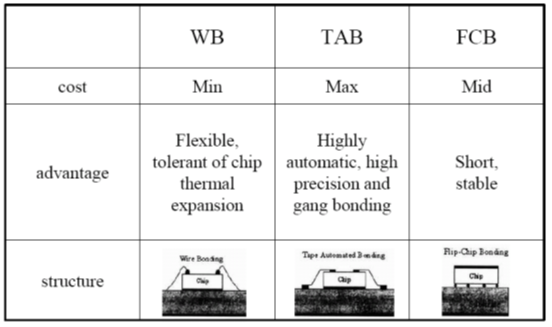

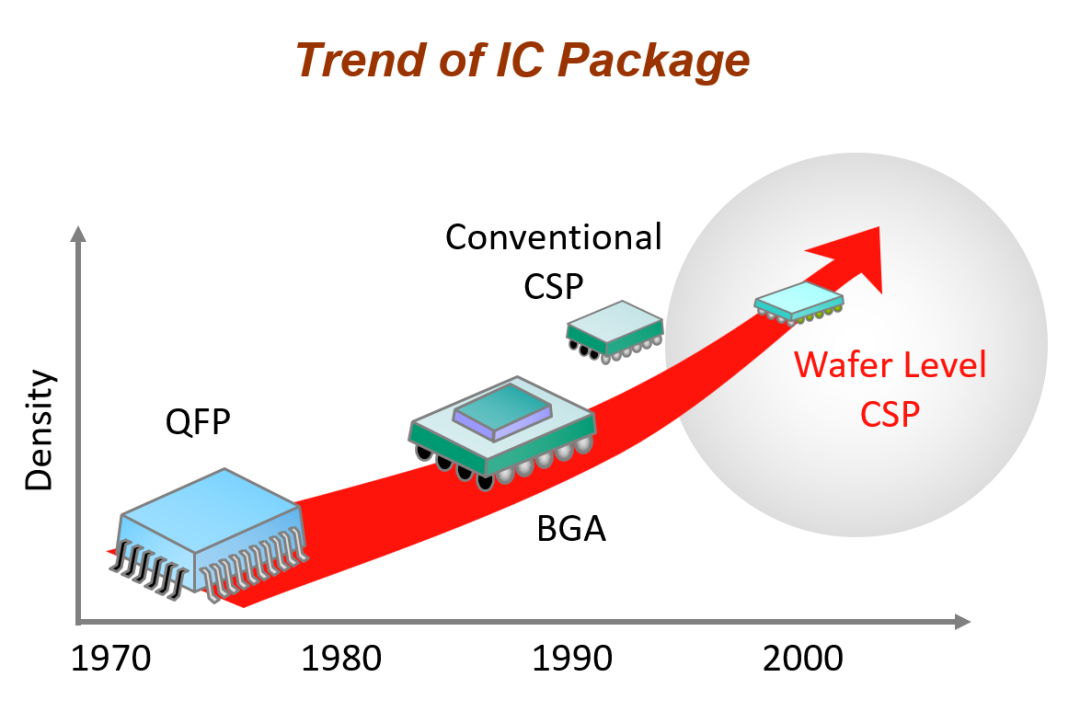

半导体封装威廉希尔官方网站 也从QFP(Quad Flat Package方形扁平式)封装工艺发展到BGA(Ball Grid Array球状引脚栅格阵列)封装,到最新的CSP(Chip Scale Package晶圆级)封装。

伴随半导体芯片体积的逐渐减小,对芯片封装威廉希尔官方网站 要求越来越高,封装威廉希尔官方网站 向着晶圆及封装发展。

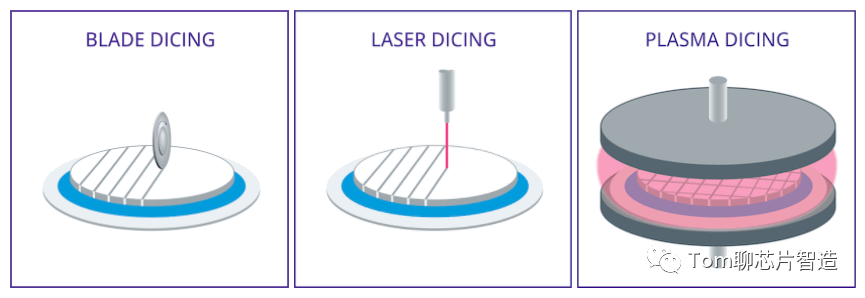

在对传统芯片进行封装时,通常是将晶圆进行切割成Die,再对每一个Die进行封装,伴随封装威廉希尔官方网站 的成熟,在最新的半导体封装中,将封装工艺与半导体工艺进行融合,在晶圆上对芯片进行统一封装,再切割形成可靠性更高的独立芯片。

随着倒装威廉希尔官方网站 的成熟应用,目前全世界的倒装芯片消耗量超过年60万片,且以约50%的速度增长,3%的晶圆封装用于倒装芯片凸点威廉希尔官方网站 ,几年后可望超过20%。

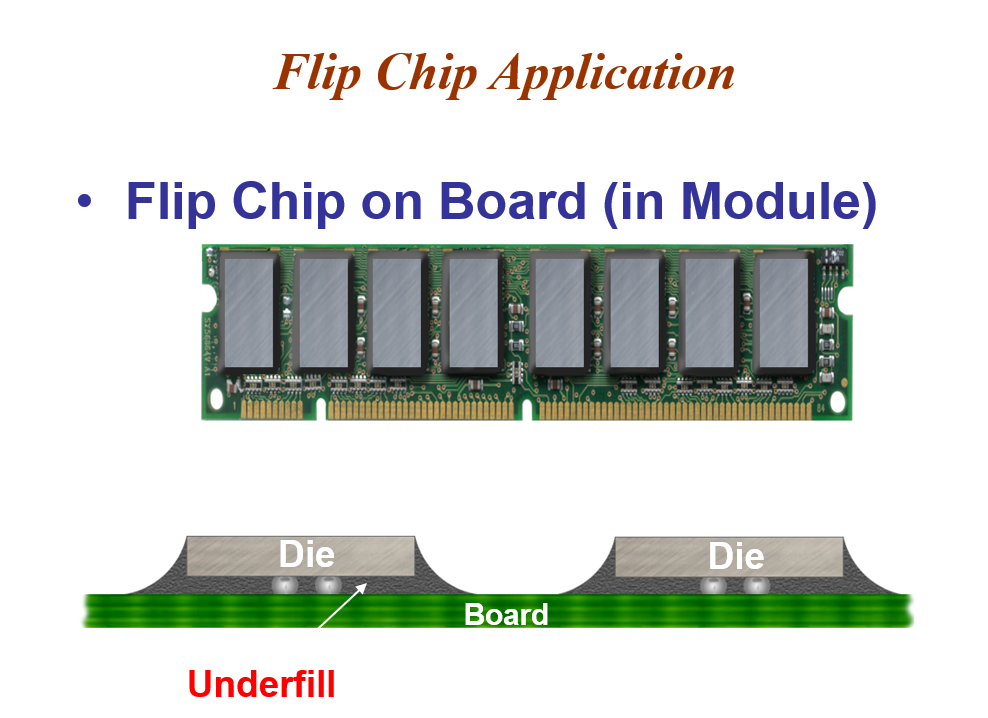

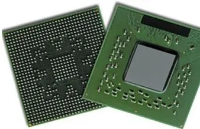

倒装芯片元件主要用于半导体设备,有些元件,如无源滤波器,探测天线,存储器装备也开始使用倒装芯片威廉希尔官方网站 ,由于芯片直接通过凸点直接连接基板和载体上。因此,更确切的说,倒装芯片也叫DCA(Direct Chip Attach),下图中CPU及内存条等电子产品是最常见的应用倒装芯片威廉希尔官方网站 的器件。

下图是内存条中存储芯片通过倒装威廉希尔官方网站 与线路板连接,芯片与电路板中间通过填充胶固定。

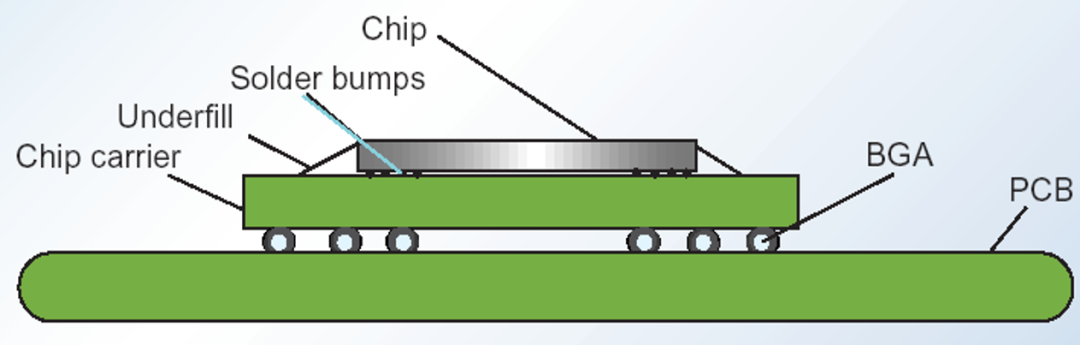

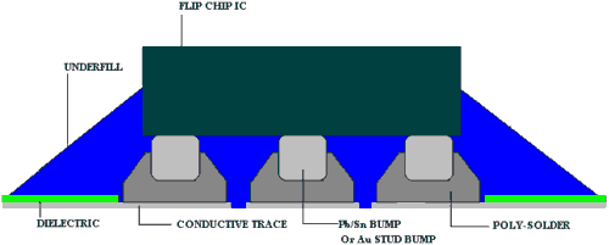

在典型的倒装芯片封装中, 芯片通过3到5个密耳(1mil=25um)厚的焊料凸点连接到芯片载体上,底部填充材料用来保护焊料凸点。

下图是一张典型的倒装连接图,芯片与下方的基板采用倒装方式连接:

三、倒装威廉希尔官方网站 威廉希尔官方网站 细节

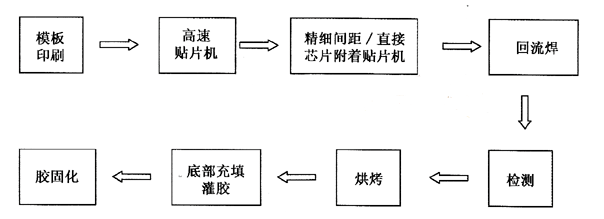

在半导体芯片倒装连接的过程中,有许多前后处理的工序,以下详细介绍倒装工艺的相关细节:

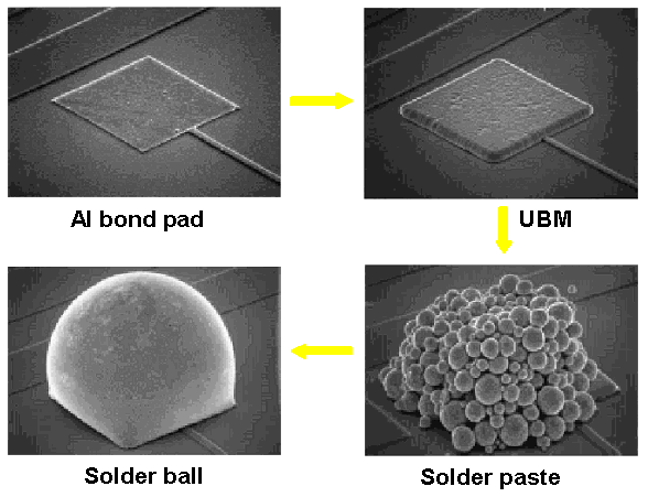

第一步:凸点下金属化(UBM,under bump metallization)

倒装连接第一步需在芯片表面制作凸点威廉希尔官方网站 ,倒装连接的本质是芯片上的凸点与基板上的凸点(凹槽)连接,半导体表面的金属化有以下几种方式:

(a)溅射:用溅射的方法一层一层地在硅片上沉积薄膜,然后通过照相平版威廉希尔官方网站 形成UBM图样,然后刻蚀掉不是图样的部分。

(b)蒸镀:利用掩模,通过蒸镀的方法在硅片上一层一层地沉积。这种选择性的沉积用的掩模可用于对应的凸点的形成之中。

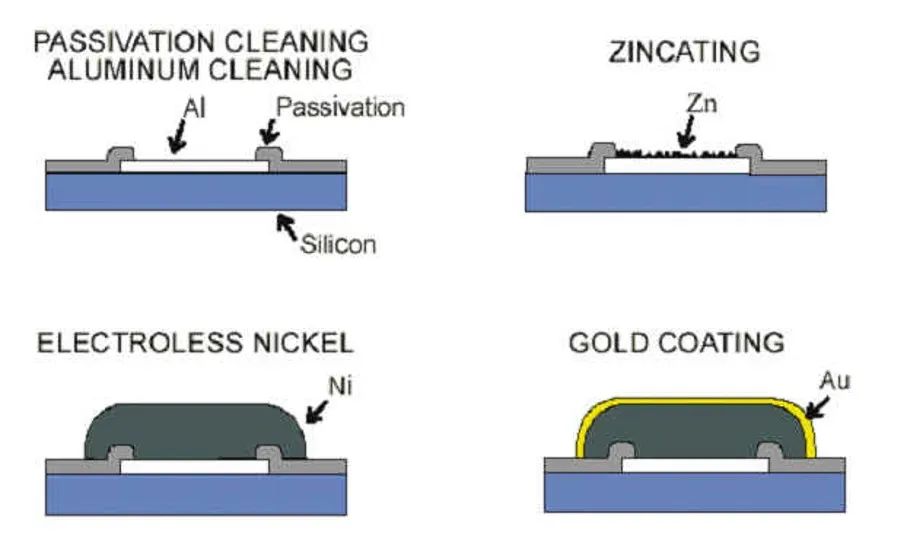

(c)化学镀:采用化学镀的方法在Al焊盘上选择性地镀Ni。常常用锌酸盐工艺对Al表面进行处理。无需真空及图样刻蚀设备,低成本。

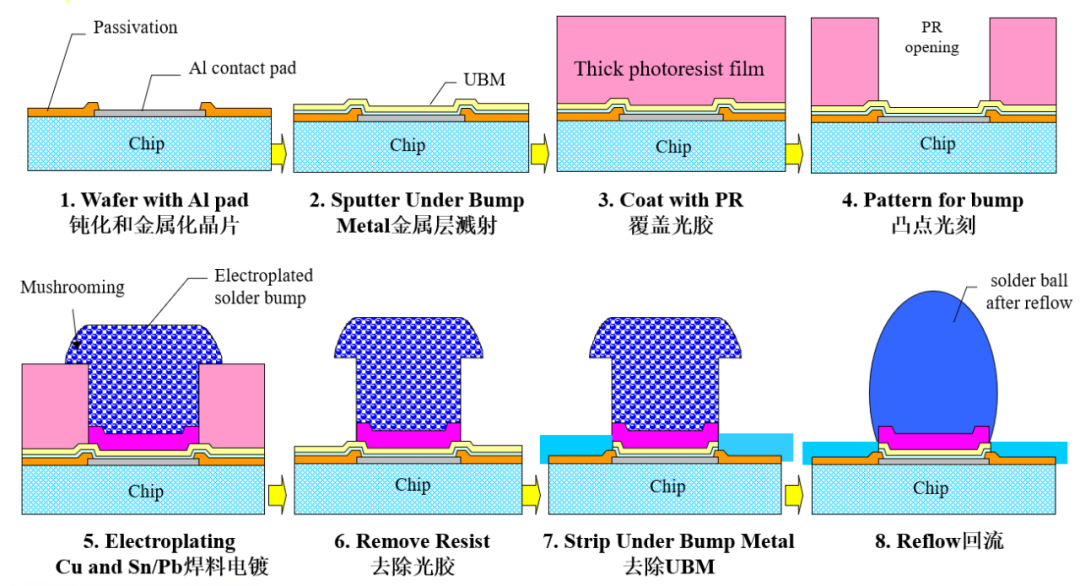

下图是半导体芯片进行凸点金属化(UBM)的流程:

由于铝焊盘表面有一层氧化物,镀层金属无法粘附在氧化的表面上,因此要对铝表面进行适当的处理以清除氧化物层。

一般的方法是在铝焊盘上采用锌酸盐处理(zincation),该威廉希尔官方网站 是在铝的表面沉积一层锌,防止铝发生氧化,镀锌工艺的一个缺点是铝也会被镀液腐蚀掉,因此需要采用二次镀锌工艺,在进行镀锌工艺中,有0.3-0.4mm厚的铝将被腐蚀掉。在镀锌过程中,锌沉积在铝表面,而同时铝及氧化铝层则被腐蚀掉。锌保护铝不再发生氧化,锌层的厚度很薄。

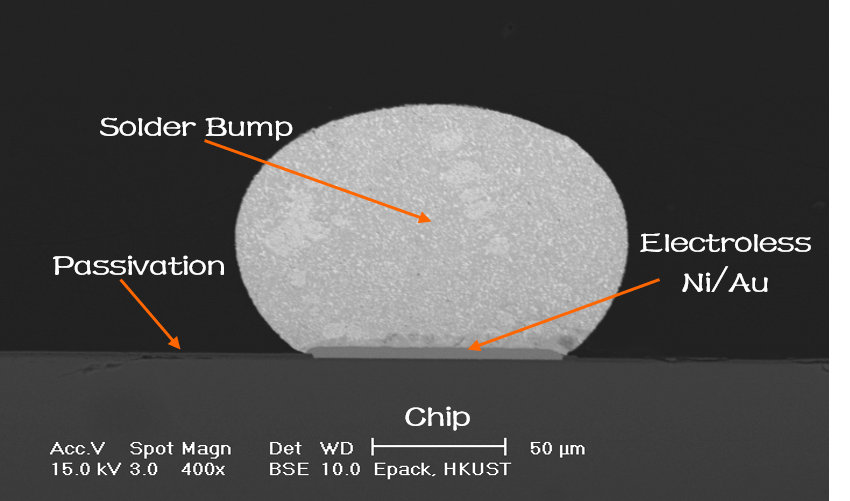

在进行镀锌工艺后,进一步采用化学镀镍用作UBM的沉积,金属镍起到连接/扩散阻挡的作用。镍的扩散率非常小,与焊料也几乎不发生反应,它仅与锡有缓慢的反应,因此非常适合作为共晶焊料的UBM金属。化学镀镍既可以用于UBM金属的沉积,也可以用来形成凸点。在部分倒装凸点的表面会进一步镀金,由于金导电性能好,且不易氧化,可增加倒装连接的可靠性。

第二步: 回流形成凸点

焊料凸点方法有蒸镀焊料凸点、电镀焊料凸点、印刷焊料凸点、钉头焊料凸点、放球凸点、焊料转移凸点等不同工艺,其中电镀焊料及印刷焊料工艺使用较广泛。

在半导体表面凸点金属化后,通过回流炉将金属化部分形成倒装球。

回流形成凸点的大致过程如下图所示:

其中电镀焊料凸点的具体形成过程如下图:

凸点常用的材料是Pb/Sn合金,因为其回流焊特性好,适合工业化生产。

除了常见的Pb/Sn合金,凸点也有Au/Ni合金等凸点材料,为了保证可靠的互连,UBM必须与用于凸点的焊料合金相容。适合高铅的UBM不一定适合高锡焊料。例如Cu润湿层合适于含锡3-5%的高铅焊料,但是不适合于高锡焊料,因为Cu与Sn反应迅速而生成Sn-Cu金属间化合物。如果Cu被消耗完毕,焊料将与焊区不润湿。

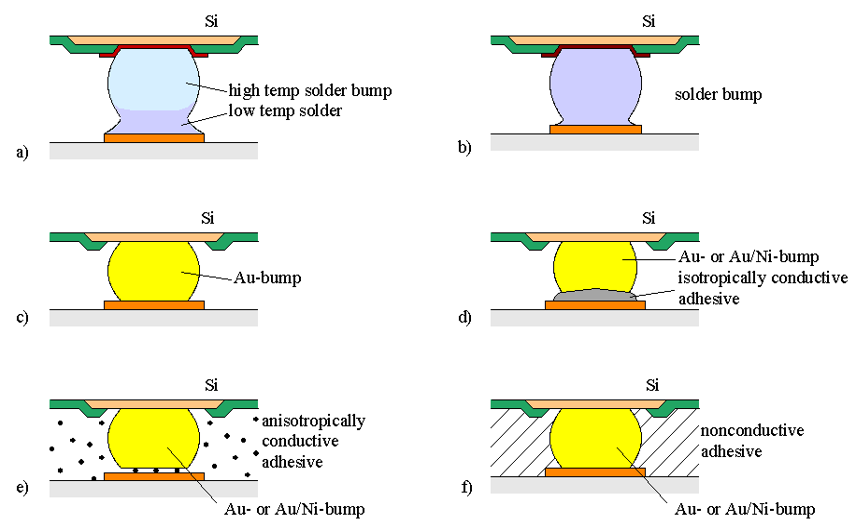

下图是不同的凸点材质件的倒装连接:

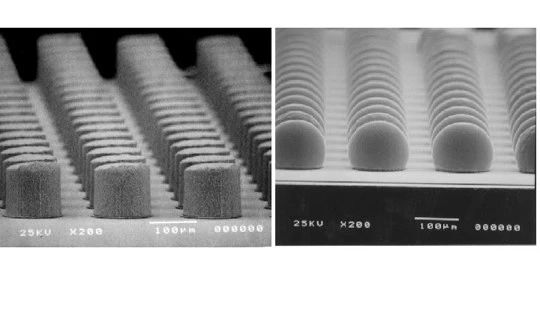

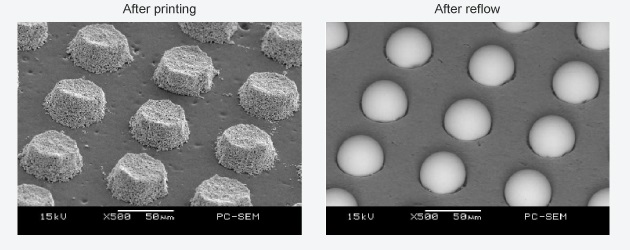

下图中的左图是回流(高温)前的凸点状态,右图是经高温后的凸点状态,经高温后凸点融化成球形。

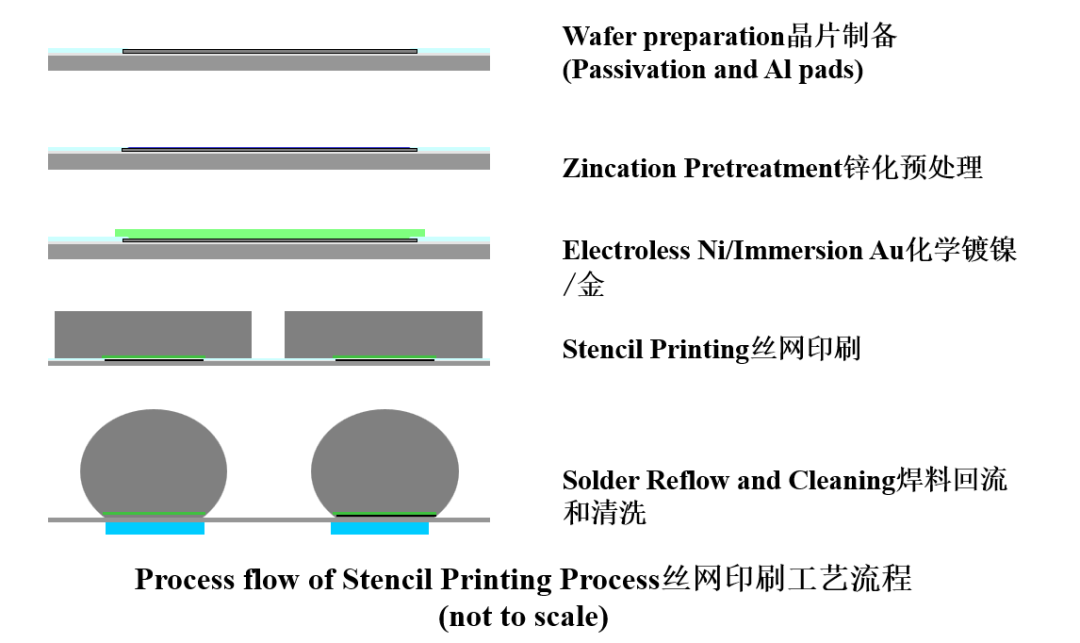

化学镀UBM和丝网印刷工艺(Electroless UBM and Stencil Printing)是工业应用中低成本倒装焊凸点制备方法。

以下是丝网印刷凸点制作流程(Stencil Printing Process Flow)及完成后的凸点形貌:

第三步:倒装芯片组装

此工序是将完成凸点制作的芯片与载板进行倒装互联。

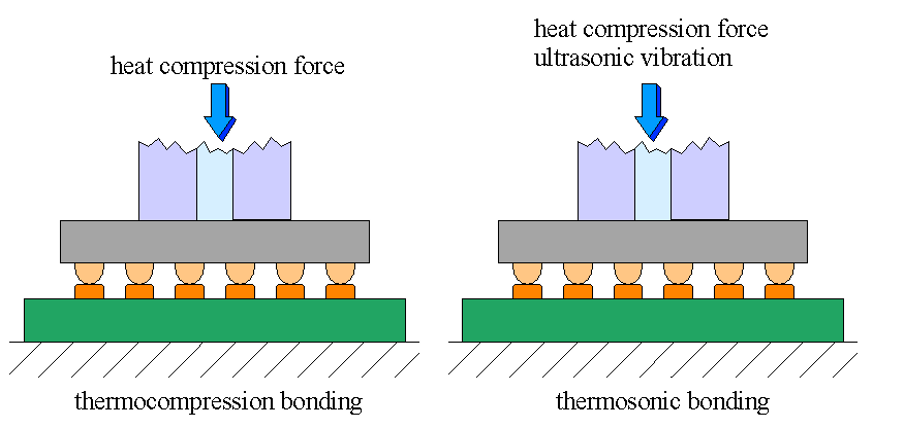

热压倒装威廉希尔官方网站 是芯片与载板连接的常用方法,最合适的凸点材料是金,凸点可以通过传统的电解镀金方法生成,或者采用钉头凸点方法,后者就是引线键合威廉希尔官方网站 中常用的凸点形成工艺。

对于热压倒装威廉希尔官方网站 ,由于压力较大,温度也较高,这种工艺仅适用于刚性基底,如氧化铝或硅。另外,基板必须保证较高的平整度,热压头也要有较高的平行对准精度。为了避免半导体材料受到不必要的损害,施加压力时应该有一定的梯度。

第四步:底部填充与固化

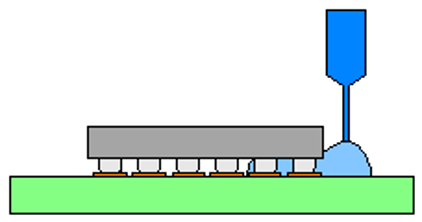

倒装连接后已完成了芯片与基板的连接,为了提高倒装稳定性,会在倒装后的芯片与基板之间采用填充胶加固,填胶工艺如下图所示:

芯片与基底之间的底部填充材料使连接抵抗热疲劳的性能显著提高,如果没有底部填充,则热疲劳将是倒装芯片主要的可靠性问题。

(a)底部填充材料将集中的应力分散到芯片的塑封材料中去。

(b)可阻止焊料蠕变,并增加倒装芯片连接的强度与刚度。

(c)保护芯片免受环境的影响(湿气、离子污染等)。

(d)使得芯片耐受机械振动与冲击。

四、倒装芯片威廉希尔官方网站 总结

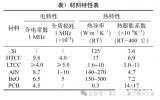

与一般的焊点连接一样,倒装芯片连接的可靠性也要受到基板与芯片的热膨胀系数(CTE)失配的影响,此外焊点的高度、焊点之间的最大间距亦会对可靠性造成影响。连接区的裂纹多是在从连接温度冷却下来的过程中产生的。

由于金的熔点温度高,因此它对疲劳损伤的敏感程度远小于焊料。因此,如果在热循环中应力没有超过凸点与焊盘之间的连接强度,那么可靠性不会存在太大问题。

芯片与基底之间的底部填充材料使连接抵抗热疲劳的性能显著提高,如果没有底部填充,则热疲劳将是倒装芯片主要的可靠性问题。

倒装芯片组装非常适用于高频应用领域,因为在这种组装结构中,芯片与基底之间的连接通路非常短。倒装焊点的串连阻抗为1mW左右,串连电感为0.025nH,远小于引线键合中的5-10nH。

正是由于倒装芯片组装的这种优点,信号的传输时延可以显著降低。

五、倒装芯片威廉希尔官方网站 的优点与缺点

(1)倒装连接威廉希尔官方网站 优点:

(a)小尺寸: 小的IC引脚图形 (只有扁平封装的5%)减小了高度和重量。

(b)功能增强: 使用倒装芯片能增加I/O的数量。I/O不像导线键合处于芯片四周而受到数量的限制。面阵列可以在更小的空间里进行更多信号、功率以及电源等互连。一般的倒装芯片焊盘可达400个。

(c)性能增加: 短的互连距离减小了电感、电阻以及电容,保证了信号延迟减少、较好的高频率、以及从晶片背面较好的热通道。

(d)提高了可靠性:大芯片的环氧填充确保了高可靠性。倒装芯片可减少三分之二的互连引脚数。

(e)提高了散热能力:倒装芯片没有塑封,芯片背面可进行有效的冷却。

(f)低成本:批量的凸点降低了成本。

(2)倒装连接威廉希尔官方网站 的缺点:

(a)裸芯片很难测试;

(b)凸点芯片适应性有限

(c)随着间距地减小和引脚数的增多导致PCB威廉希尔官方网站 面临挑战;

(d)必须使用X射线检测设备检测不可见的焊点;

(e)和SMT工艺相容性较差;

(f)操作夹持裸晶片比较困难;

(g)要求很高的组装精度;

(h)目前使用底部填充要求一定的固化时间;

(i)有些基板可靠性较低;

(j)维修很困难或者不可能。

半导体器件键合失效模式及机理分析

摘要:

本文通过对典型案例的介绍,分析了键合工艺不当,以及器件封装因素对器件键合失效造成的影响。通过对键合工艺参数以及封装环境因素影响的分析,以及对各种失效模式总结,阐述了键合工艺不当及封装不良,造成键合本质失效的机理;并提出了控制有缺陷器件装机使用的措施。

引言

半导体封装内部芯片和外部管脚以及芯片之间的连接起着确立芯片和外部的电气连接的重要作用。半导体器件的封装中,多采用引线键合的方式实现内部芯片和外部管脚以及芯片之间的互联威廉希尔官方网站 ;引线键合以工艺实现简单、成本低廉、适用多种封装形式而在连接方式中占主导地位,目前所有封装管脚的90 %以上采用引线键合连接。键合是半导体器件生产过程中的关键工序,对半导体器件的产品合格率有很大影响。

在半导体器件的使用过程中,只要其中一个键合点损坏,将导致器件失效,轻者造成器件部分功能丧失,严重者则完全功能丧失。半导体器件的本质失效约有1/3~1/4是由引线键合引起的,故其对半导体器件长期使用的可靠性影响很大。

键合失效表现出来的失效模式主要为开路(包括阻抗增大),个别情况为短路。分析其本质失效的原因,有些是与器件键合工艺有关,有些与器件的封装有关,下面结合具体案例分析介绍。

1 键合工艺不良造成失效

键合焊接时,劈刀寿命达到期限,磨损过多,以及焊接参数(时间、压力)设置不当,都可能导致键合点在以后器件使用过程中产生失效。

1.1 键合压力大造成键合点失效

某型号检波二极管在随组合完成振动试验后,发现两只器件失效,失效模式均为开路。用体视镜对两只失效器件外观进行观察,未发现明显异常。启封器件,置于显微镜下观察,发现两只失效器件内部芯片键合点脱键(如图1、2所示)。从开路键合点的形貌看,键合点金丝变形非常严重,边缘已经变得非常薄且有明显的开裂现象,说明键合焊接时,压力过大。键合压力大,键合点根部损伤严重,容易开路,另外,由于键合点非常薄且很容易出现“压裂”情况,受机械力的冲击,很容易出现开路失效。

1.2 键合压力小引发开路

键合时压力小,有可能造成键合点“未压牢”,键合丝与焊盘之间“融合”面积较小,受到机械冲击力作用,或者是温度应力作用(尤其是被塑封材料包封的键合点),键合点很容易与焊盘分离而开路失效。

某型号多丝发光二极管随整机进行试验时失效。对失效二极管外引脚进行测试,发现二极管开路失效。对器件进行X射线检查,键合丝未见明显断丝现象。对发光二极管外壳进行解剖,采用化学方法去除环氧树脂包封料,并对暴露出来的8个二极管的各个连接端进行测试,发现1#二极管开路。采用体视显微镜和扫描电镜进行观察,发现1#二极管内键合点与芯片焊盘脱键,与正常键合点比较,失效键合点变形较小。对器件内部所有键合丝进行非破坏键合拉力试验,1#二极管内键合点脱键,“零克力”失效,其它键合丝合格。使用扫描电镜对1#键合脱键位置进行观察,发现1#键合焊接面积较小。

1.3 键合丝塌丝引发短路失效

键合丝塌丝触及器件内部裸露的导体即造成短路失效。引起键合丝塌丝的原因很多,有些是因为键合丝的长短控制不当引起的,有些是因为键合丝走向不合适导致的,还有些是因为键合之后人为失误造成的。由于键合丝搭接处于一种不稳定状态,有时器件的失效现象很难复现,给失效分析工作带来困难,下面的案例充分说明了这一点。

某型号隔离放大器随整机进行振动试验时,发生失效。常温下,对失效器件进行综合电性能测试,结果为合格。之后,分别进行低温(-18 ℃,保温0.5 h后持续加电20 min)、高温(+60 ℃环境下,持续加电20 min)、常温(持续加电20 min) 测试,器件功能正常。又对器件进行5次温冲试验(-55 ℃,125 ℃,0.5 h保温,转换时间小于1 min)后,常温持续加电20分钟测试,高温(+85 ℃环境下,持续加电50 min)测试,以及恒定加速度试验(条件为:3 000 g、Y1方向,1 min)后,常温持续加电20 min测试,结果均为合格。

将失效件返生产厂家进行振动试验。首先进行两次不加电振动试验,X、Y、Z方向各5 min。在每个方向的振动完成后,对器件加电5~10 min进行测试,结果为合格。第二次振动试验功率谱密度(PSD)比第一次增加50 %,X、Y、Z方向各5 min。同样在每个方向的振动完成后,对器件加电5~10 min进行测试,结果为合格。之后再对失效样品按第二次振动条件进行加电振动试验。首先进行Z向(器件最长边方向)振动,刚刚起振,样品的正负隔离电压输出异常。停止振动并断电,重新加电后测试也正常。以上试验结果表明,振动试验可以激励器件故障复现。将样品从振动台上取下,再次进行加电测试,样品的正负隔离电压不正常。说明器件故障现象已处于稳定状态。

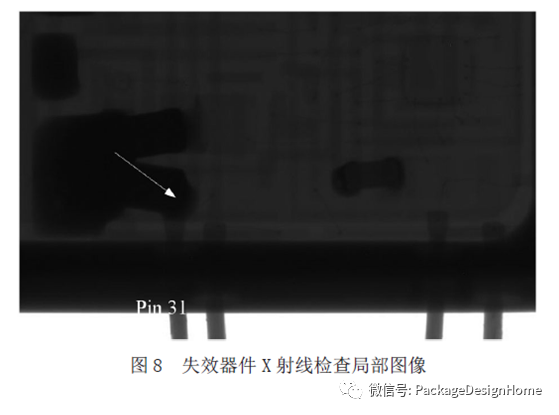

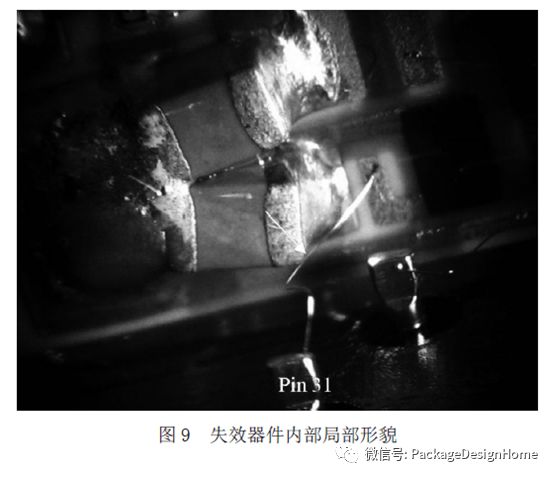

接下来对器件进行X射线检查,发现器件内部管脚31键合金丝与附近独石电容端头间无明显间隙(如图8所示)。开封器件,通过显微镜观察发现,器件内部+15 V电源(Pin 31)键合金丝与附近独石电容一端头搭接(如图9所示)。从图中可以看出,该键合丝明显过长。

隔离放大器失效机理为:器件内部管脚31(+15 V)键合金丝与附近独石电容一端头搭接,造成+15 V电源跳过限流电阻,直接加在内部振荡器芯片的正电源,导致器件内部振荡器不能正常供电,产品功耗增大,隔离电压降低,最终导致器件无输出。

以上介绍的是键合丝塌丝触及电容端头造成失效案例;有些案例是塌丝触及芯片边缘引起失效。

2 封装原因引起器件内部键合失效

因封装原因引发器件键合失效的情况包括:器件腔体内水汽含量高并有腐蚀性元素,造成键合点腐蚀开路失效,玻璃熔封DIP器件玻璃熔封料挤压外键合点开路失效,塑封器件分层造成内键合点脱键失效等。下面分别给予介绍:

2.1 内部键合点腐蚀开路失效

某型号三极管随组合进行试验过程中出现失效。对失效器件外部进行观察,发现:器件壳体表面存在熏黑迹象;底座管脚间蓝色橡胶垫局部存在过热、熔融现象。

对失效器件管脚间V-I特性进行测试,结果为:E、B及E、C极间正、反向均呈开路,B、C极间呈二极管特性。

对失效器件进行气密封检测,发现管壳与底座焊接区域存在微泄露,细检不合格。对失效器件进行粒子碰撞噪声检测,结果为合格。

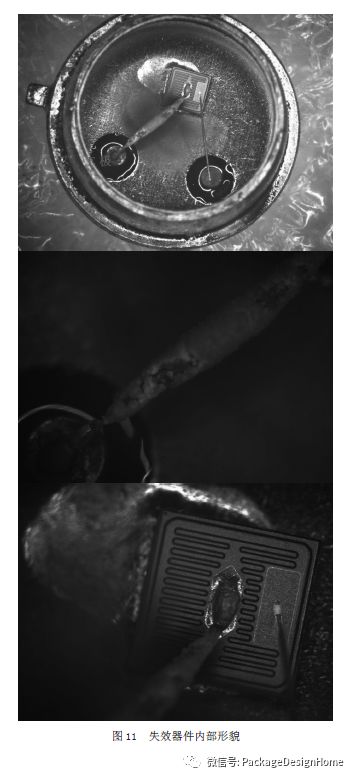

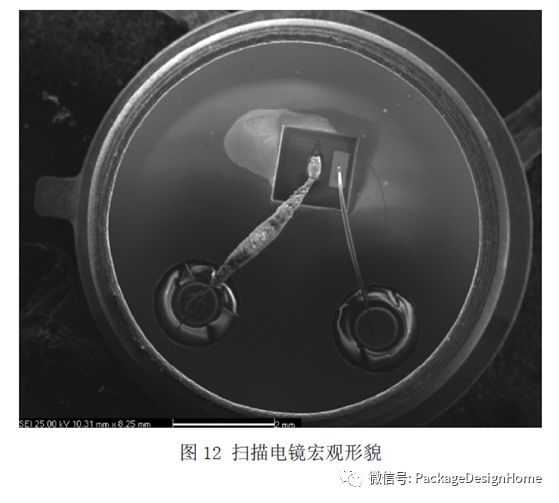

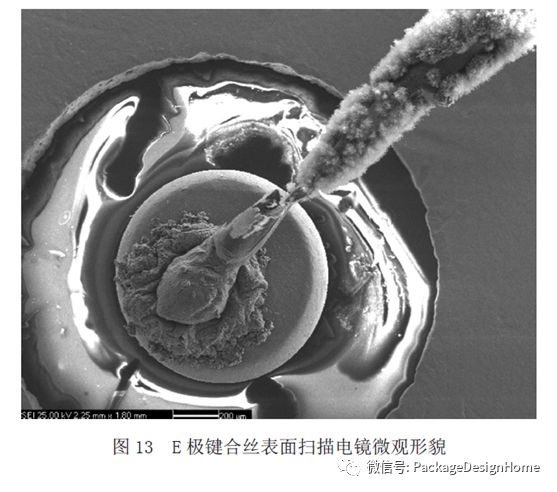

启封器件,置于显微镜下观察,发现:发射极E极外合区及键合丝表面严重腐蚀,存在一层白色絮状腐蚀产物;E极外键合区附近键合丝熔断;底座及芯片表面靠近E极键合区附近区域存在变色发黑现象;B极键合丝未发现明显异常(如图11所示)。

用扫描电镜观察,发现E极外键合区及键合丝表面腐蚀严重,存在一层白色絮状、似松球状腐蚀产物;E极外键合区附近键合丝已熔断(如图12、13所示)。对E极外键合区附近进行能谱分析,发现除含有Al、Si、Fe、Ni等主元素外,还含有O、P等元素;对键合丝表面腐蚀物进行能谱分析,发现除有Al、Si、Fe、Ni等元素外,还有O、P、Cl等元素;对B极外键合区进行能谱分析,只有Ni元素。因此得出:失效器件由于密封不合格,导致使用过程中水汽进入器件内部,同时E极键合区残存P等腐蚀元素,使键合区及键合丝外表面形成腐蚀产物堆积,在电应力的作用下,进一步过流烧毁、熔断。

2.2 玻璃熔封料挤压外键合点开路失效

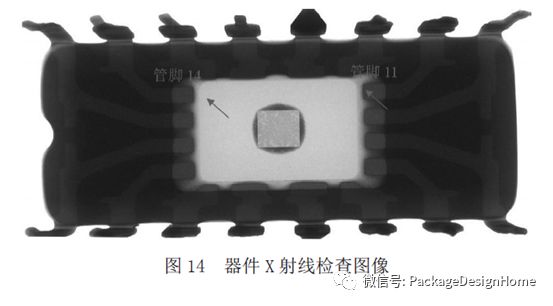

某型号玻璃熔封DIP器件在随整机进行温度冲击试验时,发现输出异常。对器件进行X射线检查,发现管脚11~14一侧玻璃熔封料较多,如图14所示。

对器件管脚间V-I特性进行测试,发现1Cext端口(管脚14)与地间开路,而正常器件则呈低阻特性。

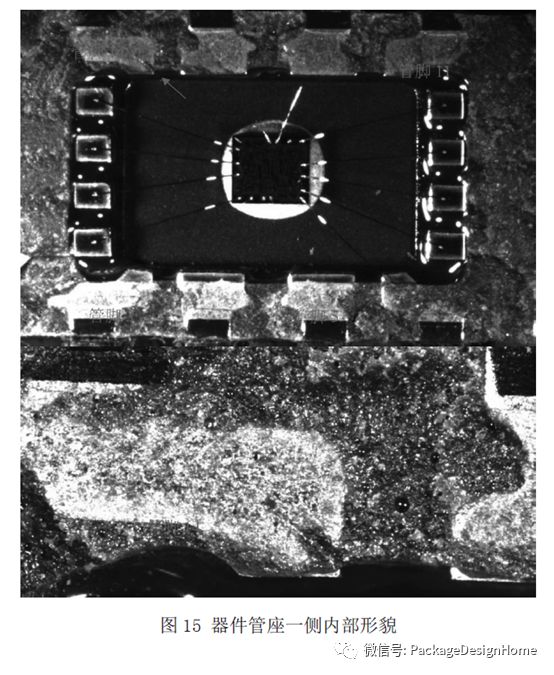

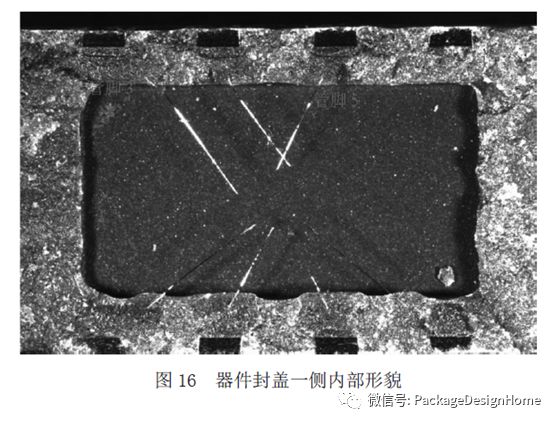

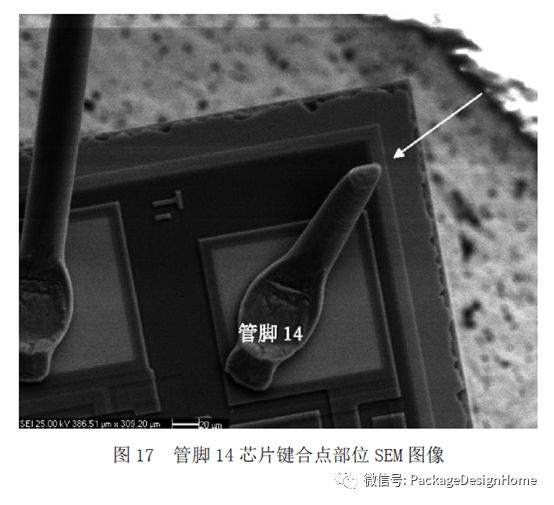

启封器件,置于显微镜下观察,芯片表面未见明显的击穿烧毁及其它异常现象,但管脚11~14一侧玻璃熔封料较多,致使管脚11~14外键合焊盘已完全被玻璃熔封料覆盖(如图15所示)。器件封盖与基座分开后,测试管脚14与焊盘间电连接无异常,管脚14焊盘上键合丝下面有一明显玻璃熔封料凸起部位(如图15所示)。封盖上残留的玻璃熔封料粘连部分与管脚3~5、管脚11~14相连键合丝(如图16所示)。管脚14内键合丝出现两个断点,一个断点位于外键合颈缩部位,另一断点位于键合丝中部,芯片一侧仍残留一段管脚14的内键合丝(如图17所示)。用万用表测试该段键合丝与地间电阻,呈低电阻特性。

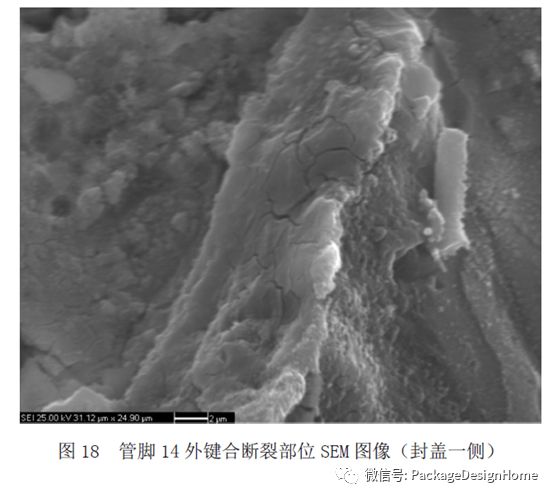

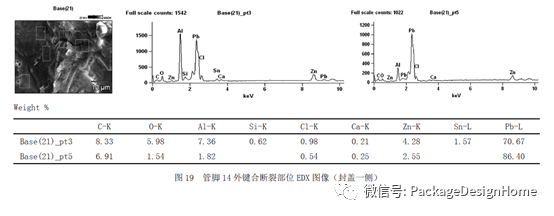

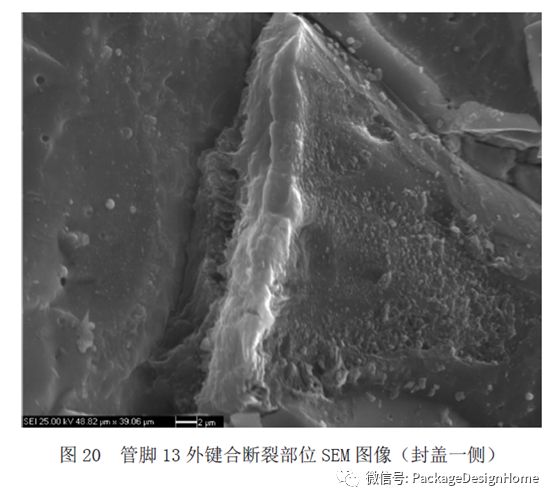

用扫描电镜及EDX对芯片一侧1Cext端口残留键合丝进行形貌观察与检测,发现断口为斜断口,断裂部位有明显的颈缩现象(如图17所示),具有明显的受力塑性断裂特征。EDX检测发现含有Al、Si、C、O等元素,未发现腐蚀性元素。此处断裂为开封过程造成的。用扫描电镜及EDX对封盖上残留的1Cext端口外键合颈缩断裂部位进行形貌观察与检测,并与1Q端口(管脚13)外键合颈缩断裂部位进行比较,发现1Cext端口外键合断裂部位存在玻璃熔封料(如图18、19所示),而1Q端口外键合颈缩断裂部位呈明显的受力断裂特征(如图20所示),能谱分析显示主要为Al元素。因此得出:器件失效是由于1Cext端口在管脚键合点颈缩部位开路造成的。导致该部位开路的原因为:封盖时1Cext端口管脚键合根部下面渗入了玻璃熔封料,对键合丝形成了“翘起”作用,并造成应力集中部位-外键合颈缩处-损伤。器件装机使用后,在各种环境应力试验过程中,受到热应力和机械应力的作用,造成该部位损伤程度进一步恶化,最终开路失效。

2.3 塑封器件分层造成内键合点脱键失效

塑封器件膜塑材料与芯片的热膨胀系数不同,如果塑封包封料与芯片间存在分层,温度变化将在塑封材料与芯片表面产生热机械剪切应力,芯片中心处的应力可以忽略,向外角或边缘延伸时应力成指数级增加;由于键合部位一般位于芯片边缘,很容易产生键合点脱键失效。

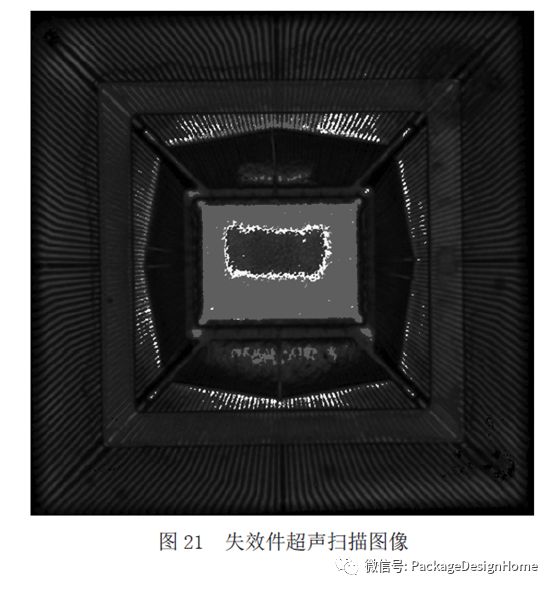

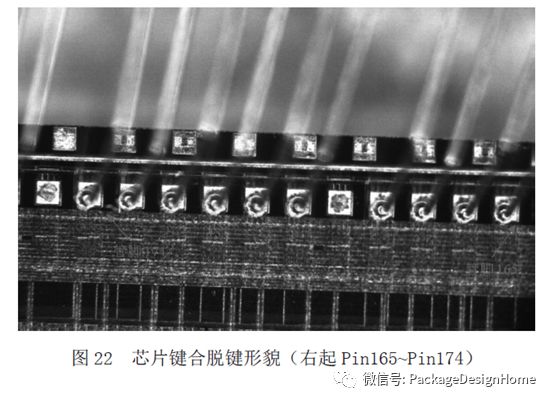

某型号集成电路在随整机进行试验时出现失效。对失效器件进行扫描超声显微镜检查,芯片表面及部分外键合部位呈现分层现象(如图21浅灰色区域所示)。

采用化学方法启封失效器件,置于显微镜下观察,发现器件内部部分与芯片基座相连的内键合丝已经脱落;多根内键合丝在芯片上的键合发生移位(如图22所示),说明键合与焊盘已经脱键。器件封装后,金丝球被塑封材料包裹,而塑封包封料与芯片间存在分层,芯片与塑封材料热涨系数差别较大,温度变化(如温度循环试验)将在塑封材料与芯片表面产生热机械剪切应力,加之键合点部位应力集中,造成部分键合点脱键失效。

3 预防措施

对于上述因制作工艺不当引起的键合失效,除了采取加强工艺控制的措施外,还可以通过相关的DPA试验项目或者筛选试验项目予以发现并剔除。下面详细介绍。

对于因键合压力大或压力小造成的键合缺陷,DPA试验中的内部目检可以发现键合点的异常形貌,DPA键合拉力试验也可以检测出键合力偏小(甚至“零克力”)的键合点。对于键合丝偏移、塌丝等缺陷,通过DPA试验中X射线检查(对Au丝),以及内部目检可以及早发现。对于键合点腐蚀缺陷,DPA试验中气密性检测可以发现器件密封问题,内部气体成份分析可以检测出器件内部水汽含量是否超标,内部目检可以及早发现腐蚀缺陷。恒定加速度的筛选试验也可以一定程度地暴露及剔除上述缺陷。

通过DPA试验中X射线检查,以及内部目检可以及早发现玻璃熔封料挤压外键合点缺陷。通过DPA试验中超声扫描检查,可以及早发现塑封器件分层缺陷。另外,温度循环试验也可以一定程度地暴露及剔除上述缺陷。

4 结束语

前面通过典型案例介绍,分析了键合工艺不当,以及器件封装因素对器件键合本质失效造成的影响。对以上分析进行总结,得出键合工艺不当,对元器件失效产生的影响主要体现在以下几方面:键合压力大造成键合点损伤,导致键合开路失效。键合时压力小,键合丝与焊盘之间“融合”面积较小,导致键合开路失效。键合丝的长短控制不当,或者走向不合适,导致短路失效。因封装原因引发器件键合失效的情况包括:空封器件腔体内气氛不良,造成键合点腐蚀开路失效,陶瓷玻璃熔封料挤压外键合点开路失效,以及塑封器件分层造成内键合点开路失效等。通过相关的DPA试验项目或者筛选试验项目可以及早暴露缺陷并予以剔除。

审核编辑:刘清

电子发烧友App

电子发烧友App

评论