我们俗称的 PCB 信号等长处理。等长的目标是为了满足同组信号的时序匹配要求。 2、等长范围应严格遵守不同接口或者信号的要求,具体的可参考模块规范内容。如若有疑问,及时与客户进行确认。 3、处理等长之前应先把同组内线长最长的信

2023-07-27 07:40:03 2592

2592

; Cadence PSD;MentorGraphices的Expedition PCB;Zuken CadStart;

2010-03-02 09:36:12 20037

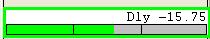

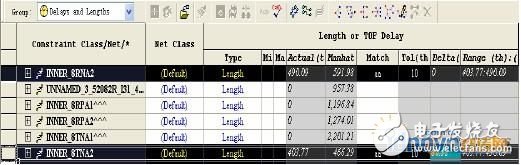

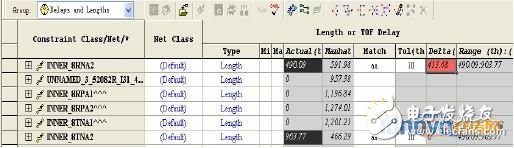

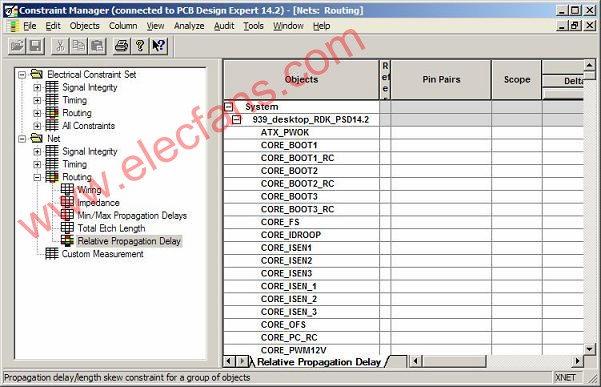

20037 Propagation Delay,如图5-100所示; 图5-100 相对传输延迟设置示意图 第三步,选中一根需要做等长其中一根信

2020-04-15 10:55:40 5486

5486 1.PCB设计之电容的结构和特性给导体加电位,导体就带上电荷。但对于相同的电位,导体容纳电荷的数量却因它本身结构的不同而不同。导体能够容纳电荷的能力称为PCB设计之电容。 通常,某导体容纳的电荷Q

2019-08-13 10:49:30

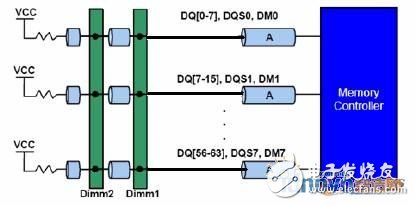

本期讲解的是高速PCB设计中DDR布线要求及绕等长要求。布线要求数据信号组:以地平面为参考,给信号回路提供完整的地平面。特征阻抗控制在50~60 Ω。线宽要求参考实施细则。与其他非DDR信号间距至少

2017-10-16 15:30:56

PCB设计中差分线怎么设置,还有就是等长分析

2019-08-19 09:47:36

PCB设计如何绕等长?阻抗会对信号速度产生影响吗?

2021-03-06 08:47:19

PCB设计者必看,18种特殊走线的画法与技巧01PCB设计者必看,AD布蛇形线方法Tool里选Interactive length tuning要先布好线再改成蛇形,这里用的是布线时直接走蛇形:先

2020-06-24 08:03:05

等长是PCB设计的时候经常遇到的问题。存储芯片总线要等长,差分信号要等长。什么时候需要做等长,等长约束条件是什么呢?首先,等长的作用。由于信号在PCB走线上存在延时,正比于信号线的长度。假设PCB

2014-12-01 11:00:33

PCB布等长线时,会设置等长规则,具体的长度是根据什么设置的呢?以最长的为依据还是芯片手册为依据呢?在这里抛砖引玉啦!!!

2016-01-09 20:54:46

我的AD9446的工作在LVDS模式下,请问对于AD9446(100MHz),LVDS信号线的PCB走线的差分对间等长有没有要求?(PS:16对差分线,都做等长好复杂)谢谢!

2023-12-18 06:26:51

,一定要想办法解决掉。②做好PCB布局布线前期准备主要包括PCB机械结构、外形定义,信号层电源层分配、电气网格大小设定,板子固定螺丝过孔安放等。这些设置与后面的布局布线密不可分。2012-3-30 13

2012-12-04 23:14:03

在附件中是如何设置等长线的规则指导,因为经常性的会忘记,所以经撰写下来,以供自己和他人参考,避免不必要的时间浪费在查找资料上。

2020-08-10 12:35:58

Altium Designer 蛇行 等长 布线 技巧一. 设置需要等长的网络组点击主菜单 Design-->Classes,在弹出的窗口中单击 Net Classes,并右键,点 Add

2013-01-12 15:18:43

本帖最后由 山文丰 于 2020-7-14 14:32 编辑

1、为什么要等长,等长的重要性。在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号

2020-07-14 14:30:31

,此时按下“tab”键就会弹出如下图1.3所示的“网络等长参数设置窗口”。按照下图1.3进行网络等长参数设置,完成操作后点击确定键。图1.3网络等长参数设置窗口完成等长网络参数设置,会出现如下图1.4

2018-03-09 09:54:43

最近在学习cadence,练习PCB时,发现等长条件不满足时,也没出现DRC报错,刚开始会出现ED错误的!求高手指教

2016-01-09 20:44:16

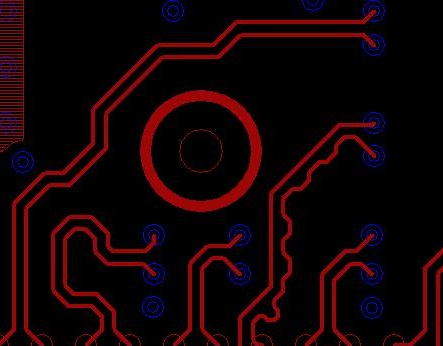

因为第一次做等长线处理,业务不熟练,在网上也看了各类教程,单实际画的时候又是另外一回事,能请各位大神帮我指出图中的问题点吗?万分感谢,你那个有具体的指导建议就更完美了!

2019-08-07 16:07:29

本帖最后由 carey123 于 2014-10-24 15:50 编辑

DxDesigner到Expedition进行pcb设计流程简介采集采集

2014-10-24 13:42:32

Mentor Expedition PCB 2004/2005 设计复用请教各位大侠~~~ 我用的软件是Expedition pcb 2004/2005,不知道怎么使用复用功能?每次遇到相同功能模块的时候,总是要从新摆放,很不方便,还请各位大侠赐教~~~~

2014-10-28 10:35:29

Mentor Expedition PCB的生成主要由三个过程组成:其一是原理图的生成,其二是根据已经生成的原理图产生一个PCB模板文件,第三步是在PCB模板文件的基础上进行布局和布线。当然,在这个过程中始终贯穿始终的是Expedition中心库的操作。点击下载

2019-04-17 09:30:05

`Mentor PCB设计交流, 包括PADS Standard Plus, PADS Professional(EE单机版), Expedition PCB设计, 群号:149765399`

2016-06-13 11:15:44

MentorGraphics"绑架"了Expedition!偶比较倾向Orcad Capture+Expedition的Netlist流程,主要是OrCAD Capture

2014-11-07 09:59:40

`各位大佬,ORCAD PCB (16.3~16.6)在设计PCB时候,需要画差分线和差分的等长要求,请教各位如何设置;谢谢!`

2018-04-14 09:54:03

`各们老师们,如何设置差分等长自动走曲形线,而不是蛇形线。在长度约束里我设置数量也是最小了还是没有像这样的曲形线,是不是PADS没有这个功能,请各们老师们帮小弟解答一下。`

2019-06-10 10:23:30

各位大侠,Allegro16.6 T等长是如何设置的呢,请帮帮忙啦~~~~

2016-02-29 08:22:15

allegro中 ddr等长设置及绕线的步骤

2015-12-28 22:01:11

个人小结,希望能对那些还不会用allegro设置等长规则的朋友有点作用。也欢迎同行交流。

2013-12-26 15:53:24

altuim designer 等长命令及技巧Altuim Designer by PCB高速设计解决方案,小北设计师SAS等长命令:TR:单端线等长;TI : 差分线等长;等长过程中: “”增加

2018-08-02 11:57:55

altuim designer 等长命令及技巧,小北PCB设计SAS等长命令:TR:单端线等长;TI : 差分线等长;等长过程中: “”增加绕线幅度; “Y“改变出线的方向;数字键1减小绕线拐角幅度

2018-08-04 13:03:03

mentor expedition PCB 文件谁有呢?还有安装与破解,求分享!请各位大神帮忙。

2013-03-02 10:41:15

pciex2进行PCB设计时,收发数据线需要做等长么?

2016-02-15 15:12:40

以太网的接口信号,在PCB走线的时候,差分可以不等长么?如果要等长,误差是多少?

2023-04-07 17:38:17

刚学ALLEGRO,一直搞不懂差分对设置等长跟阻抗匹配的关系,不知附图那样设置对不对,求指点

2014-11-30 22:41:22

在PCB布局走线时CAN需要差分等长线吗?

2023-04-07 17:39:25

请教大神如何将orcad转成mentor_expedition?

2021-04-23 07:22:47

各位大侠:想请问下,如何在Protel ***中设置手工不同网络之间的等长走线,越详细越好!谢谢!

2012-09-15 22:44:01

在ALLEGRO中设置好T型接点后,如下图所示据我的理解,ALLEGRO中T型接点等长设置的是图中BC和BD两断走线的等长,对吧??那如何设置AB走线的等长??

2017-07-07 17:55:14

原子大哥,由此看到你画PCB时,有考虑到时序,进行了等长线的画法,请问AD中如何设置等长线画法,有没有教程或者帖子推荐下!

2019-07-26 04:36:27

等长SDRAM时,比如A0换TAB键标题显示的是总的线长,大于目标长度,不能绕等长要怎么设置按ctrl+鼠标中间显示的也是总的线长,add from-to里显示的是正确

2019-04-23 07:35:01

走差分线可以设置等长吗

2019-07-31 05:35:12

`贴片电阻两端出线如何画才能等长???如何设置?PCB打样找华强 http://www.hqpcb.com 样板2天出货`

2013-08-19 20:50:13

Mentor Expedition PCB 的生成主要由三个过程组成:其一是原理图的生成,其二是根据已经生成的原理图产生一个PCB 模板文件,第三步是在PCB 模板文件的基础上进行布局和布线。当

2008-05-11 23:08:29 0

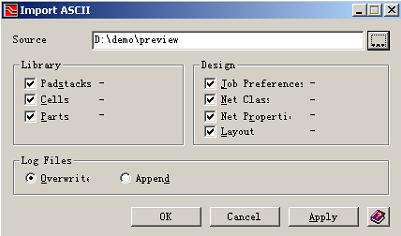

0 PowerPCB转Mentor Expedition过程:1. 把需要转化的文件放在一个新的目录下(本文的PCB文件放在D:demo下)2. 用PowerPCB打开PCB文件:3. 选用FileExport,选择保存的文件类型为HKP Files(*.hkp):这

2009-08-11 19:08:12 0

0 EXPEDITION PCB是MENTOR GRAPHICS公司针对企业用户开发的EDA设计工具,其PCB设计、仿真功能强大,又非常易于使用。

2010-06-07 09:03:55 0

0 本文介绍了应用MENTOR GRAPHICS公司的EXPEDITION系列实现单板计算机主模块设计流程,从而有效地解决了信号完整性问题,提高了复杂PCB项目的设计效率。

2010-06-07 09:17:33 0

0 本文主要从 pcb 设计的角度介绍如何利用ExpeditionI/O Designer 完成公司基站基带处理板的设计。在较短周期内完成单板PCB 设计,提高pcb 设计效率的设计过程。

2010-06-16 10:04:34 49

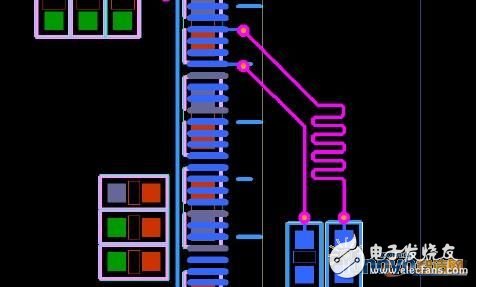

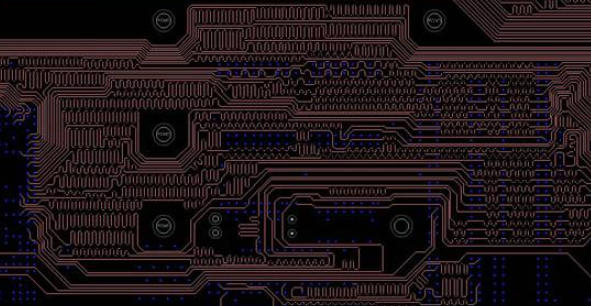

49 在当前的PCB 设计当中,对于走线长度的要求越来越多。ExpeditionPCB 自动调线的功能强大。在PCB 的设计当中若能最大限度地使用ExpeditionPCB 的自动调线功能,将有利于提高设计效

2010-07-04 11:41:02 0

0 mentor expedition的功能说明

一、Mentor Graphics Expedition 系列PCB 软件威廉希尔官方网站

特点概述1、基于WINDOWS NT/WIN2000/98 平台Expedition 的母平台为WINDOWS 操作系统,能在W

2008-03-22 17:46:48 6580

6580 PowerPCB转Mentor Expedition教程

1. 把需要转化的文件放在一个新的目录下(本文的PCB文件放在D:demo下)2. 用PowerPCB打开PCB文件:

2009-04-15 00:32:59 1621

1621

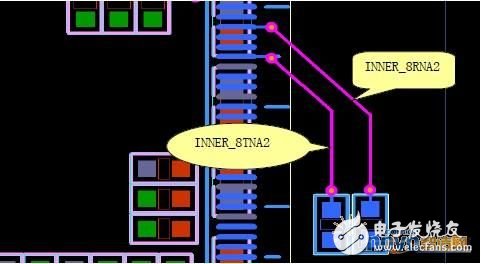

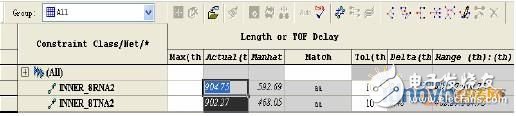

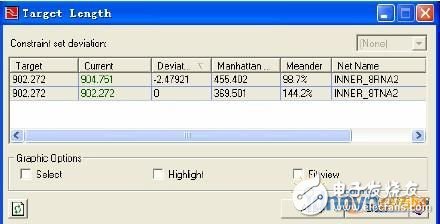

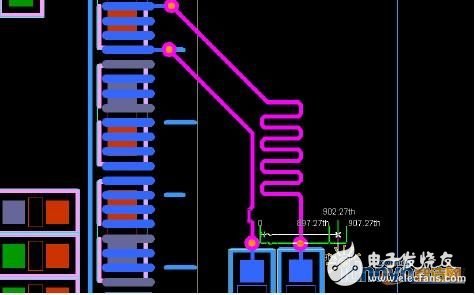

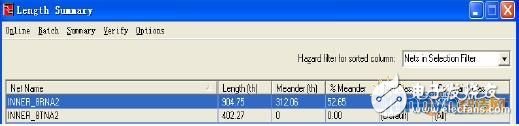

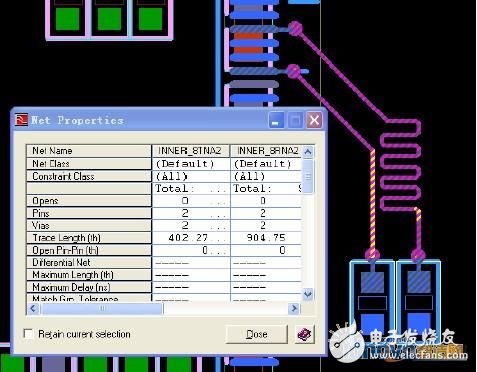

为了使二个SDRAM的时钟线等长,设置等长的方法有很多,在这里我们只为了二条时钟线等长来学习如何通过设置约束规则然后通

2010-06-21 11:57:52 1302

1302

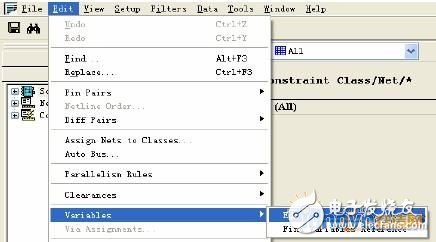

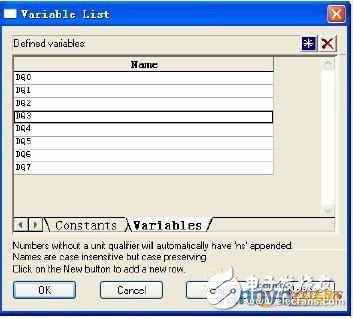

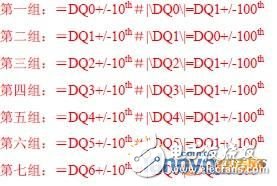

对于简单走线等长在以前文档中都有涉及这里不再复述了,下面内容将给大家介绍一下有关Xnet等长的设置问题, 如现在主板DD

2010-06-28 09:38:18 27424

27424

Mentor Expedition PCB 的生成主要由三个过程组成:其一是原理图的生成,其二是根据已经生成的原理图产生一个PCB 模板文件,第三步是在PCB 模板文件的基础上进行布局和布线。当然,在这

2011-05-10 15:13:20 0

0 PADS LAYOUT 设计等长方法 首先把要做等长的线,分组设一种颜色,在把设计格点设置好,(格点很重要,如线宽为5mil,间距为5mil,等长走 线要做2倍线宽,那么格点设计如下,2倍间距为10mil+5mil线宽

2013-09-05 11:26:14 0

0 PADS做等长与铺铜打VIA快速设计技巧 。学习PADS的盆友可要看看!

2016-01-13 15:22:32 0

0 allegro_差分线等长设置,有需要的下来看看

2016-02-22 16:15:35 62

62 第一步:连接好需要绕等长的线,

第二步: T+R T+R开始绕等长, TABTAB 键调出等长属性设置框

第三步:滑动走蛇形线即可;

2016-09-12 16:13:30 0

0 Expedition 的PCB 布线器不仅具有自动和交互式推挤布线功能,而且能推挤过孔;在布线完成后能移动元器件的位置且自动保持正确的连线。

2018-01-05 14:07:19 9601

9601

1.将需要做等长的线组成一个类:在Design-Classes中,右键Net Classes弹出菜单中,选择Add Class,为新New Class命名(Rename Class),加入需要

2018-05-22 10:45:56 17738

17738 在PCB设计中如何设置格点的方法 合理的使用格点系统,能使我们在PCB设计中起到事半功倍的作用。但何谓合理呢?

2018-07-08 05:33:00 11802

11802 PCB编辑器参数设置主要设定编辑操作的意义、显示颜色、显示精度等项目。

PCB编辑器及参数1 常规(General)参数设置2 显示(Editing Display)参数设置3 交互式布线

2018-09-21 08:00:00 0

0 有了单线的自动等长,那就肯定不会放过板上随处可见的差分了,看大招——Auto-interactive Phase Tune。现在板子的速率越来越高,板上的差分线也就跟着越来越多,对内等长的工作量自然就加大了。但是自从有了绕线新功能,就再也不担心绕等长费时多啦。步骤和单线绕等长一样,简单明了。

2018-10-19 15:33:40 26241

26241 本文档的主要内容详细介绍的是Allegro PCB设计时等长设置的一些方法与技巧解析。以DDR3(4pcs,fly-by 结构)为例,讲述一下在allegro 中如何添加电气约束(时序等长)。

2018-11-27 16:02:57 0

0 等长走线的目的就是为了尽可能的减少所有相关信号在 PCB 上的传输延迟的差异。至于 USB/SATA/PCIE 等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方将时钟

2019-04-26 15:27:25 10423

10423

本例中需要实现PCI-e金手指到EMMC芯片等长,包括D0-D7,CLK,CMD这10条网络。查看各条网络,确认是否存在串联匹配电阻。本例中,仅在时钟线上存在,如下图的高亮器件。

2019-06-22 09:44:22 8173

8173

相信很多layout工程师在画板的最后都在为绕等长而闹心,今天给大家介绍一个allergo自带的绕等长AiDT功能,希望对大家有所帮助。

2020-06-23 16:24:51 4152

4152

PCB布线设置规范说明

2020-06-29 18:19:39 1864

1864 Properties进入安全间距参数设置对话框进行参数设置,参数包括PCB设计布线范围(Rule scope)和PCB设计布线属性(Rule Attributes)。 2.设置拐角模式(Rules Corners

2020-09-03 14:38:37 6289

6289 在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

2020-09-27 14:08:18 2506

2506

在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

2020-10-24 09:29:38 8605

8605 如图所示很多用户在进行等长的时候回出现直角或者锐角的等长走线。 那么怎么解决呢: 1)在直接快捷键TR进行蛇形等长的时候,可以按字母键盘上方的数字1 或者2来调整等长走线的形状。 2)按一下无法调整过来的话可以继续执行,直到变成钝角。 编辑:hfy

2020-10-18 09:36:20 2646

2646

1.关于等长 第一次听到“绕等长工程师”这个称号的时候,我和我的小伙伴们都惊呆了。每次在研讨会提起这个名词,很多人也都是会心一笑。 不知道从什么时候起,绕等长成了一种时尚,也成了PCB设计工程师心中

2021-01-20 12:11:32 5175

5175

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54:17 18399

18399 第一次听到“绕等长工程师”这个称号的时候,我和我的小伙伴们都惊呆了。每次在研讨会提起这个名词,很多人也都是会心一笑。

2022-02-12 15:21:26 2222

2222 电子发烧友网为你提供DDR 高速PCB 设计走线绕等长资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-30 08:42:00 52

52 电子发烧友网为你提供PCB绕等长之“同组同层”资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-05 08:46:28 12

12 电子发烧友网为你提供PCB设计:如何绕等长?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-05 08:46:59 23

23 电子发烧友网为你提供PCB设计:为什么要绕等长?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-05 08:47:22 22

22 Mentor Expedition PCB 的生成主要由三个过程组成:其一是原理图的生成,其二是根据已经生成的原理图产生一个PCB 模板文件,第三步是在PCB 模板文件的基础上进行布局和布线。当然,在这个过程中始终贯穿始终的是Expedition 中心库的操作。

2021-05-08 11:24:15 75

75 PCB布线是pcb设计中很关键的一环,有一些小伙伴不知道pcb布线线宽一般设置多少,下面我们就来介绍一下pcb布线线宽一般设置多少。 一般pcb布线线宽要考虑两个问题。一是电流的大小,如果流过的电流

2021-08-17 15:07:54 63133

63133 在DDR的设计中,需要对数据线及地址线进行分组及等长来满足时序匹配,通常DDR的数据线之间的长度误差需要保证在50mil以内,地址线的长度误差需要保证在100mil以内。

2022-11-02 09:25:18 763

763 在PCB设计中做等长时,常常会用到蛇形走线,下面就介绍一下如何进行蛇形走线及相关设置: 执行菜单面临Route-Delay Tune,在Options进行相关设置,其中Style是蛇形等长的样式

2023-05-23 07:45:03 813

813 PCB设计中常见的走线等长要求

2023-11-24 14:25:36 651

651

电子发烧友App

电子发烧友App

评论