在systemverilog中,如果一个类没有显式地声明构造函数(new()),那么编译仿真工具会自动提供一个隐式的new()函数。这个new函数会默认地将所有属性变量。

2022-11-16 09:58:24 2700

2700 SystemVerilog中多态能够工作的前提是父类中的方法被声明为virtual的。

2022-11-28 11:12:42 467

467 SystemVerilog中可以将类属性声明为常量,即“只读”。目的就是希望,别人可以读但是不能修改它的值。

2022-11-29 10:25:42 1644

1644 在 SystemVerilog 中,联合只是信号,可通过不同名称和纵横比来加以引用。

2023-10-08 15:45:14 593

593

SystemVerilog 接口的开发旨在让设计中层级之间的连接变得更加轻松容易。 您可以把这类接口看作是多个模块共有的引脚集合。

2024-03-04 15:25:22 387

387

SystemVerilog 的VMM 验证方法学教程教材包含大量经典的VMM源代码,可以实际操作练习的例子,更是ic从业人员的绝佳学习资料。SystemVerilog 的VMM 验证方法学教程教材[hide][/hide]

2012-01-11 11:21:38

本帖最后由 鼻子抽筋 于 2012-2-21 15:41 编辑

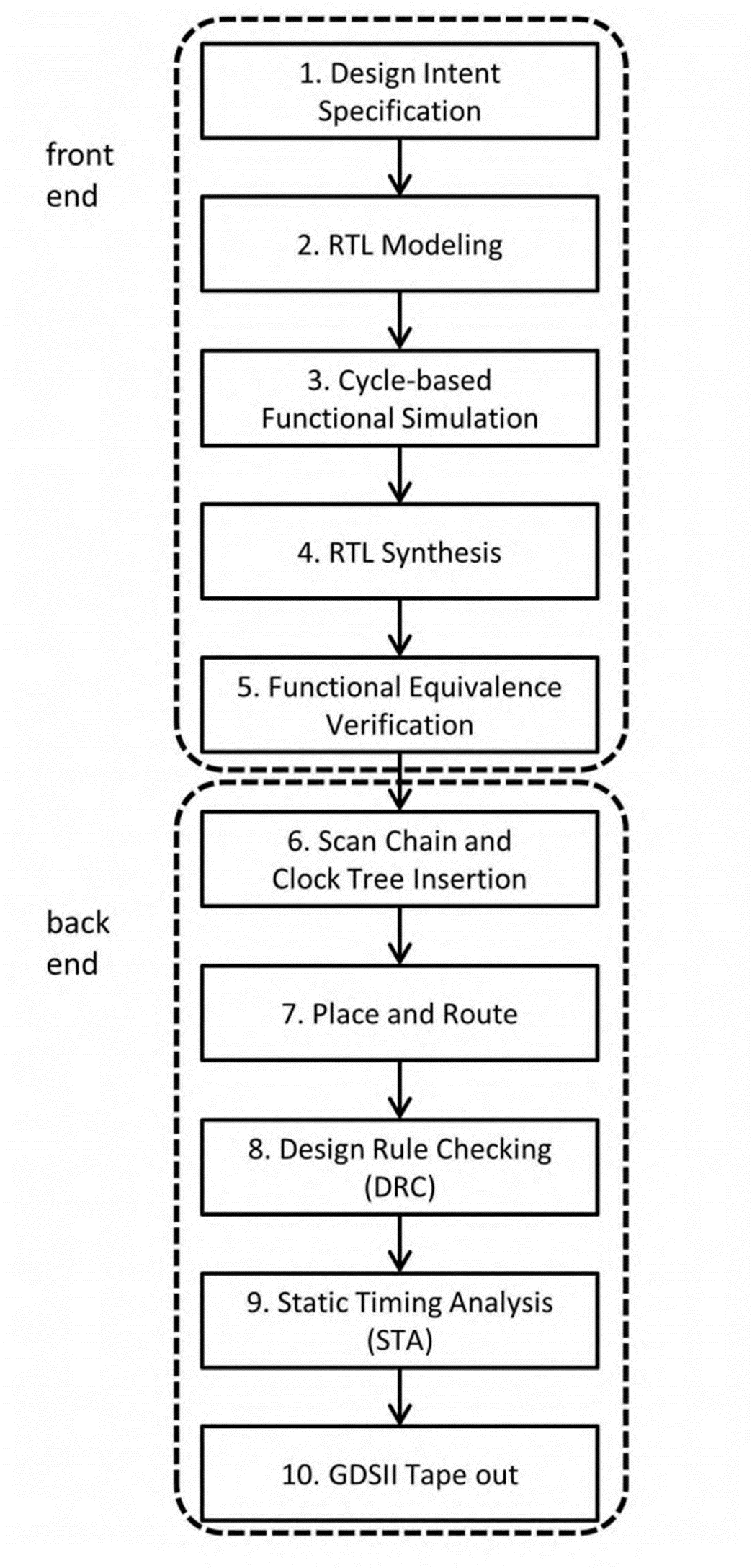

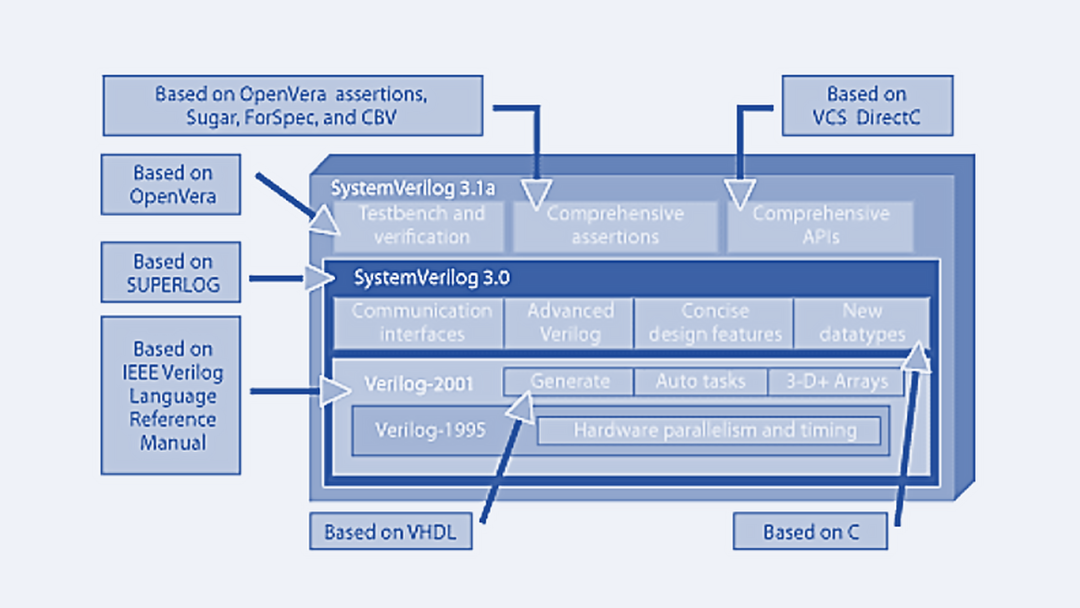

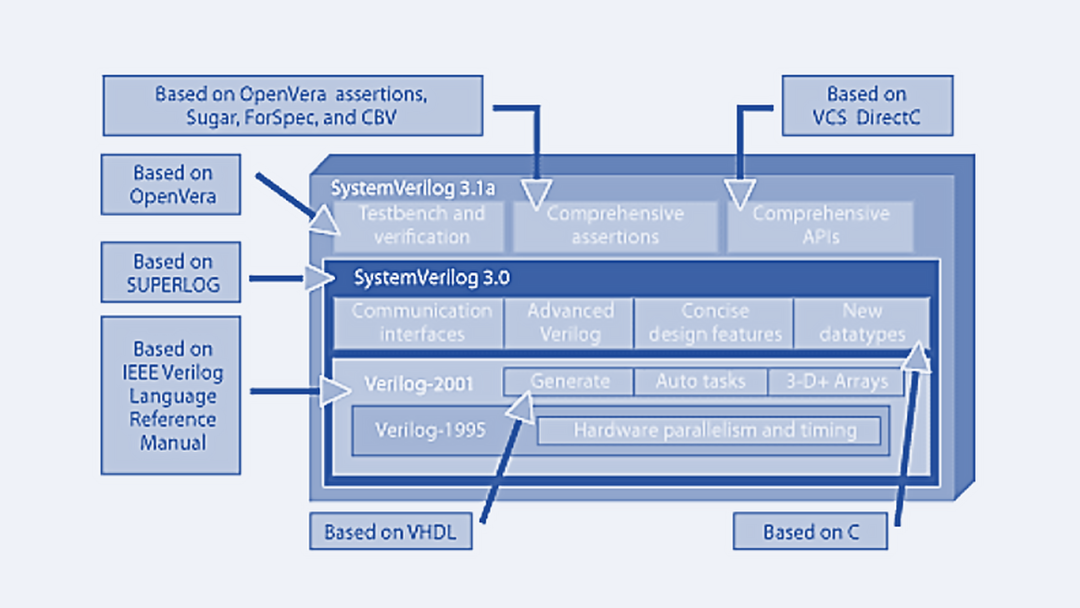

SystemVerilog给予Verilog、VHDL和C/C++优点为一身的硬件描述语言,很值得学一学。1、8-bit up

2012-02-21 15:39:27

SystemVerilog有哪些标准?

2021-06-21 08:09:41

官方的一个systemverilog详解,很详细。推荐给打算往IC方面发展的朋友。QQ群374590107欢迎有志于FPGA开发,IC设计的朋友加入一起交流。一起为中国的IC加油!!!

2014-06-02 09:47:23

官方的一个systemverilog详解,很详细。推荐给打算往IC方面发展的朋友。

2014-06-02 09:30:16

systemverilog的一些基本语法以及和verilog语言之间的区别。

2015-04-01 14:24:14

本文讨论了一些System Verilog问题以及相关的SystemVerilog 语言参考手册规范。正确理解这些规格将有助于System Verilog用户避免意外的模拟结果。

2020-12-11 07:19:58

本文讨论了一些System Verilog问题以及相关的SystemVerilog 语言参考手册规范。正确理解这些规格将有助于System Verilog用户避免意外的模拟结果。

2020-12-24 07:07:04

);没有像VHDL一样的重组件实例化。SystemVerilog语言的优势有:与Verilog相比代码结构更加紧凑;结构体和枚举类型有更好的扩展性;更高抽象级别的接口;Vivado综合支持

2020-09-29 10:08:57

学快速发展,这些趋势你了解吗?SystemVerilog + VM是目前的主流,在未来也将被大量采用,这些语言和方法学,你熟练掌握了吗?对SoC芯片设计验证感兴趣的朋友,可以关注启芯工作室推出的SoC芯片

2013-06-10 09:25:55

大家好,我对一个 round robin 的 systemverilog 代码有疑惑。https://www.edaplayground.com/x/2TzD代码第49和54行是怎么解析呢 ?

2017-03-14 19:16:04

的方向,可能会讲的更好,比如说 FPGA芯片,雷达系统,机器人设计与制造,芯片制造,机器视觉,3D建模,计算机安全,芯片安全,Verilog语言、VHDL语言、数字电路,SystemVerilog语言

2023-05-21 23:51:10

、数字电路,SystemVerilog语言、SystemC语言、Matlab、C/C++语言,人工智能, 激光雷达,智能算法,硬件加速设计等,希望有这些方向的书籍试读!谢谢!2023年5月22日

2023-05-22 23:34:48

仿真和后端仿真- 和模拟电路部门协同工作- 支持测试部门,帮助芯片级调试和失效分析l 任职要求- 精通Verilog语言和Systemverilog语言- 熟悉相关的EDA软件- 熟悉数字接口协议如

2018-10-23 17:15:42

,本科5年数字芯片验证工程师岗位要求:1、熟悉systemverilog 语言,熟练掌握UVM/VMM/OVM验证方法学,独立完成过中等规模以上模块的验证开发2、熟悉数字芯片验证流程,三年以上相关工作经验3、硕士3年,本科5年联系方式:ucollide@163.com一八五八3907八零五

2018-03-13 09:27:17

Xilinx推荐使用纯bd文件的方式来设计FPGA,这样HDL代码就会少了很多。但我们大多数的工程还是无法避免使用HDL来连接两个module。所以本文就推荐使用SystemVerilog来简化

2021-01-08 17:23:22

在某大型科技公司的招聘网站上看到招聘逻辑硬件工程师需要掌握SystemVerilog语言,感觉SystemVerilog语言是用于ASIC验证的,那么做FPGA工程师有没有必要掌握SystemVerilog语言呢?

2017-08-02 20:30:21

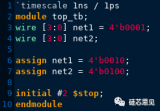

如下图,先建一个systemverilog的cell,但是会报错,求帮解决下。写个最简单的也会报语法错误。

2021-06-24 06:24:26

)的搭建经验; 7.熟练掌握Verilog、systemVerilog 语言编程,具有较为复杂的逻辑设计经验; 8.熟悉XILINX 或ALTERA FPGA 内部结构,熟悉相关开发工具(ISE

2015-07-16 11:04:49

我们将展示如何在SystemVerilog中为状态机的命令序列的生成建模,并且我们将看到它是如何实现更高效的建模,以及实现更好的测试生成。

2021-01-01 06:05:05

本节介绍循环模型编译器响应不受支持或被忽略的构造的行为。

一般而言,Cycle Model Compiler支持Verilog和SystemVerilog语言的大部分可合成子集。

如果周期模型编译器

2023-08-12 06:55:08

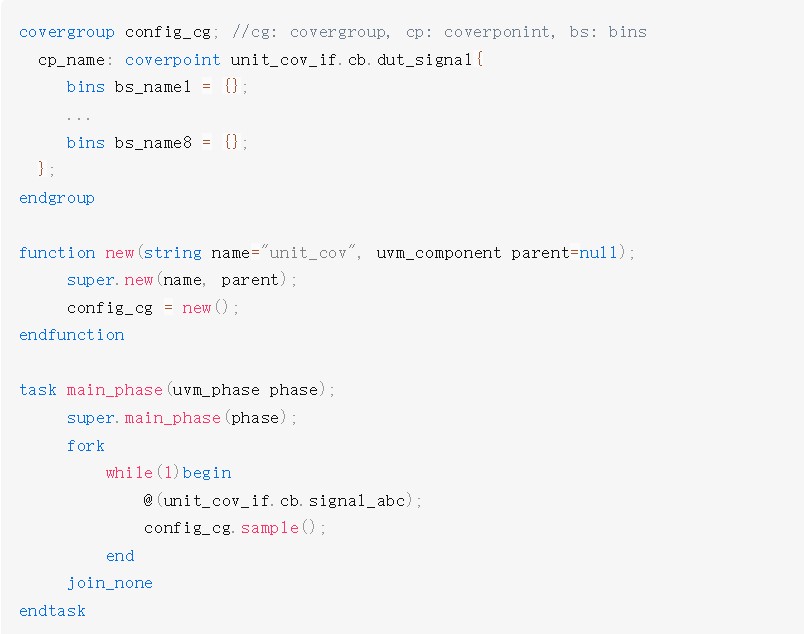

?uvm的特点以及uvm为用户提供了哪些资源?什么是uvm呢?uvm是通用验证方法学的缩写,是为验证服务的,uvm是基于systemverilog语言来实现的,因此,在学习uvm之前,应当

2021-01-21 16:00:16

,随着该介绍,第一个硬件验证语言诞生了。 ***2 年,还创建了一个新标准 SystemVerilog。 现在有不同的验证语言可用,其中 e、SystemVerilog、SystemC

2022-02-16 13:36:53

导入SystemVerilog程序包意味着什么?

2020-12-11 06:53:29

上是基于 Verisity Design 在 2001 年开发的用于 e 验证语言的eRM(e Reuse Methodology)。UVM 类库为SystemVerilog 语言,如序列和数据自动化功能(打包、复制、比较

2022-02-13 17:03:49

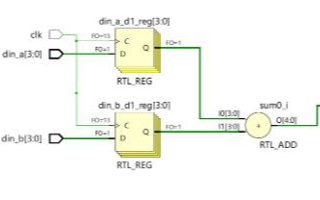

2打两拍systemverilog与VHDL编码1 本章目录1)FPGA简介2)SystemVerilog简介3)VHDL简介4)打两拍verilog编码5)打两拍VHDL编码6)结束语2 FPGA

2021-07-26 06:19:28

本参考手册详细描述了Accellera为使用Verilog硬件描述语言在更高的抽象层次上进行系统的建模和验证所作的扩展。这些扩展将Verilog语言推向了系统级空间和验证级空间。SystemVerilog

2009-07-22 12:14:44 187

187 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:08:48 188

188 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:12:50 20

20 Section 1 Introduction to SystemVerilog ..... 1Section 2 Literal Values... 42.1 Introduction

2009-07-22 14:18:46 39

39 Chapter 1: Introduction to SystemVerilogChapter 2: SystemVerilog Declaration SpacesExample 2-1

2009-07-22 14:45:34 0

0 本文利用形式化的方法对SystemVerilog的指称语义进行研究,采用EBES(extendedbundle event structure)作为抽象模型,以便更好的描述SystemVerilog真并发的特点。我们的主要工作是:首先,

2009-12-22 14:01:07 12

12 如何采用SystemVerilog 来改善基于FPGA 的ASIC 原型关键词:FPGA, ASIC, SystemVerilog摘要:ASIC 在解决高性能复杂设计概念方面提供了一种解决方案,但是ASIC 也是高投资风险的,如90nm ASIC/S

2010-02-08 09:53:33 10

10 就 SystemC 和 SystemVerilog 这两种语言而言, SystemC 是C++在硬件支持方面的扩展,而 SystemVerilog 则继承了 Verilog,并对 Verilog 在面向对象和验证能力方面进行了扩展。这两种语言均支持

2010-08-16 10:52:48 5140

5140 随着项目复杂程度的提高,最新的系统语言的聚合可以促进生产能力的激增,并为处在电子设计自动化(EDA)行业中的设计企业带来益处。SystemVerilog和SystemC这两种语言在设计流

2010-08-25 09:44:47 1181

1181 文章主要介绍《VMM for SystemVerilog》一书描述的如何利用SystemVerilog语言,采用验证方法学以及验证库开发出先进验证环境。文章分为四部分,第一部分概述了用SystemVerilog语言验证复杂S

2011-05-09 15:22:02 52

52 在介绍SystemVerilog 断言的概念、使用断言的好处、断言的分类、断言的组成以及断言如何被插入到被测设计(DUT)的基础上,本文详细地介绍了如何使用不同的断言语句对信号之间的复

2011-05-24 16:35:19 0

0 文中分析了基于Systemverilog验证环境的结构,并在介绍I 2 C总线协议的基础上,重点论述了验证环境中事务产生器及驱动器的设计。

2011-12-22 17:20:21 27

27 目前只完成了设计概念和硬件描述,支持部分常用32位MIPS指令(ADD,SUB,LW,SW,等)。硬件描述用的是SystemVerilog语言,生成软件Synplify 9.6.2。昨天我测试了执行

2014-12-16 15:51:07 15922

15922 Xilinx 更新语言课程: 使用 VHDL 进行设计 、 高级 VHDL 、 使用 Verilog 进行设计 、 使用 SystemVerilog 进行

2017-02-09 02:18:11 168

168 Xilinx 更新语言课程: 使用 VHDL 进行设计 、 高级 VHDL 、 使用 Verilog 进行设计 、 使用 SystemVerilog 进行

2017-02-09 02:18:11 217

217 本文档的主要内容详细介绍的是基于Verilog硬件描述语言的IEEE标准硬件描述语言资料合集免费下载:1995、2001、2005;SystemVerilog标准:2005、2009

2020-06-18 08:00:00 10

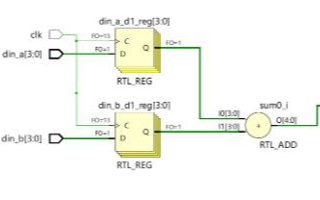

10 了SystemVerilog语言。有两点值得注意:一是两个N位数相加,无论是有符号数还是无符号数,其结果都有可能是N+1位,故输出比输入位宽多1位,这样才能保证不会发生溢出(Overflow)。二是默认情况下,代码中的logic表示的都是无符号数,但是对于下面这段代码,无

2020-09-24 14:31:15 1996

1996

手册的这一部分探讨了使用SystemVerilog进行验证,然后查看了使用SystemVerilog的优点和缺点。

2021-03-29 10:32:46 23

23 SystemVerilog语言简介 SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充

2021-09-28 17:12:33 2803

2803 作者:limanjihe https://blog.csdn.net/limanjihe/article/details/83005713 SystemVerilog是一种硬件描述和验证语言

2021-10-11 10:35:38 2042

2042 本文定义了通常用于描述使用SystemVerilog对硬件功能进行建模的详细级别的术语。

2022-03-30 11:42:02 1336

1336 SystemVerilog是硬件设计和验证语言的IEEE行业标准。标准编号为IEEE 1800。SystemVerilog名称将替换旧版Verilog名称。SystemVerilog语言是原始

2022-07-04 11:01:04 840

840 利用Systemverilog+UVM搭建soc验证环境

2022-08-08 14:35:05 5

5 IEEE SystemVerilog标准:统一的硬件设计规范和验证语言

2022-08-25 15:52:21 0

0 HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~

2022-08-31 09:06:59 1168

1168 SystemVerilog中枚举类型虽然属于一种“强类型”,但是枚举类型还是提供了一些“不正经”的用法可以实现一些很常见的功能,本文将示例一些在枚举类型使用过程中的一些“不正经”用法,并给出一些使用建议。

2022-09-01 14:20:14 1057

1057 event是SystemVerilog语言中的一个强大特性,可以支持多个并发进程之间的同步。

2022-10-17 10:21:33 1027

1027 SystemVerilog casting意味着将一种数据类型转换为另一种数据类型。在将一个变量赋值给另一个变量时,SystemVerilog要求这两个变量具有相同的数据类型。

2022-10-17 14:35:40 1960

1960 学习Systemverilog必备的手册,很全且介绍详细

2022-10-19 16:04:06 2

2 SystemVerilog提供了几个内置方法来支持数组搜索、排序等功能。

2022-10-31 10:10:37 1760

1760 SystemVerilog中除了数组、队列和关联数组等数据结构,这些数据结构还可以嵌套。

2022-11-03 09:59:08 1176

1176 SystemVerilog packages提供了对于许多不同数据类型的封装,包括变量、task、function、assertion等等,以至于可以在多个module中共享。

2022-11-07 09:44:45 862

862 SystemVerilog“struct”表示相同或不同数据类型的集合。

2022-11-07 10:18:20 1852

1852 SystemVerilog union允许单个存储空间以不同的数据类型存在,所以union虽然看起来和struct一样包含了很多个成员,实际上物理上共享相同的存储区域。

2022-11-09 09:41:28 575

575 在systemverilog中方法也可以声明为“static”。静态方法意味着对类的所有对象实例共享。在内存中,静态方法的声明存储在一个同一个地方,所有对象实例都可以访问。

2022-11-18 09:31:44 572

572 SystemVerilog中的句柄赋值和对象复制的概念是有区别的。

2022-11-21 10:32:59 523

523 要想理解清楚SystemVerilog语言中的Upcasting和Downcasting概念,最好的方式从内存分配的角度理解。

2022-11-24 09:58:15 925

925 SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充了 C语言 数据类型、结构、压缩

2022-12-08 10:35:05 1262

1262 SystemVerilog中Semaphore(旗语)是一个多个进程之间同步的机制之一,这里需要同步的原因是这多个进程共享某些资源。

2022-12-12 09:50:58 2344

2344 更紧凑; 支持块注释(老版VHDL不支持); 没有像VHDL一样的重组件实例化。 (3)SystemVerilog语言的优势有

2022-12-28 17:05:01 2375

2375 上一篇文章介绍了SystemVerilog的各种随机化方法,本文将在其基础上引入SystemVerilog的随机约束方法(constraints)。通过使用随机约束,我们可以将随机限制在一定的空间内,有针对性地提高功能覆盖率。

2023-01-21 17:03:00 1519

1519 SystemVerilog既是一种硬件设计语言,也是一种硬件验证语言。IEEE SystemVerilog官方标准没有区分这两个目标,也没有指定完整SystemVerilog语言的可综合子集。相反,IEEE让提供RTL综合编译器的公司来定义特定产品支持哪些SystemVerilog语言结构。

2023-02-09 14:23:56 734

734

SystemVerilog既是一种硬件设计语言,也是一种硬件验证语言。IEEE SystemVerilog官方标准没有区分这两个目标,也没有指定完整SystemVerilog语言的可综合子集。相反,IEEE让提供RTL综合编译器的公司来定义特定产品支持哪些SystemVerilog语言结构。

2023-03-31 14:45:22 1131

1131

持SystemVerilog语言,是开发仿真器的一个重要任务。 SystemVerilog的发展历程 数字芯片的验证威廉希尔官方网站

是随着Verilog语法的演变而演变的。 最早,Verilog是完全用来描述

2023-04-07 14:40:34 535

535

SystemVerilog Interface是modport的一种,但比简单的输入、输出或输入输出端口的功能更多。

2023-04-28 14:10:06 1233

1233

SystemVerilog Interface是modport的一种,但比简单的输入、输出或输入输出端口的功能更多。

2023-04-28 14:12:22 1924

1924

写过Verilog和systemverilog的人肯定都用过系统自定义的函数$display,这是预定好的,可以直接调用的功能。

2023-05-16 09:27:02 581

581

我们在工作中常常会针对数组施加各式的约束,下面列举一下有趣的**Systemverilog数组约束**示例

2023-05-30 11:13:21 402

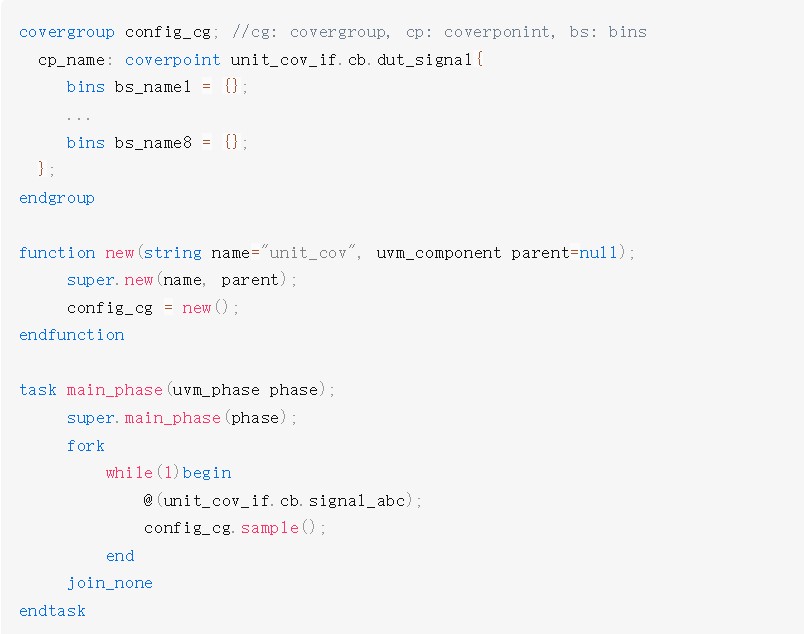

402 SystemVerilog是一名芯片验证工程师,必须掌握的一门语言,其中Function Coverage是必须要懂的知识点之一;

2023-06-04 16:30:24 3703

3703

在SystemVerilog中,我们知道可以使用动态数组实现数组元素个数的动态分配,即随用随分

2023-06-09 09:46:24 3977

3977

在systemverilog中,net用于对电路中连线进行建模,driving strength(驱动强度)可以让net变量值的建模更加精确。

2023-06-14 15:50:16 751

751

为了确保验证的完备性,我们需要量化验证目标。SystemVerilog提供了一套丰富的覆盖率建模方式。

2023-06-25 10:44:16 520

520 SystemVeirlog的全面支持是开发商用仿真器的第一道门槛。市面上可以找到不少基于纯Verilog的仿真器,但是真正能完整支持SystemVerilog 的仍然屈指可数。如何全面地支持SystemVerilog语言,是开发仿真器的一个重要任务。

2023-07-14 15:15:25 354

354

本文讲一下SystemVerilog的time slot里的regions以及events的调度。SystemVerilog语言是根据离散事件执行模型定义的,由events驱动。

2023-07-12 11:20:32 775

775

在Verilog和SystemVerilog中经常需要在使用变量或者线网之前,期望变量和线网有对应的初始值

2023-08-25 09:47:56 546

546

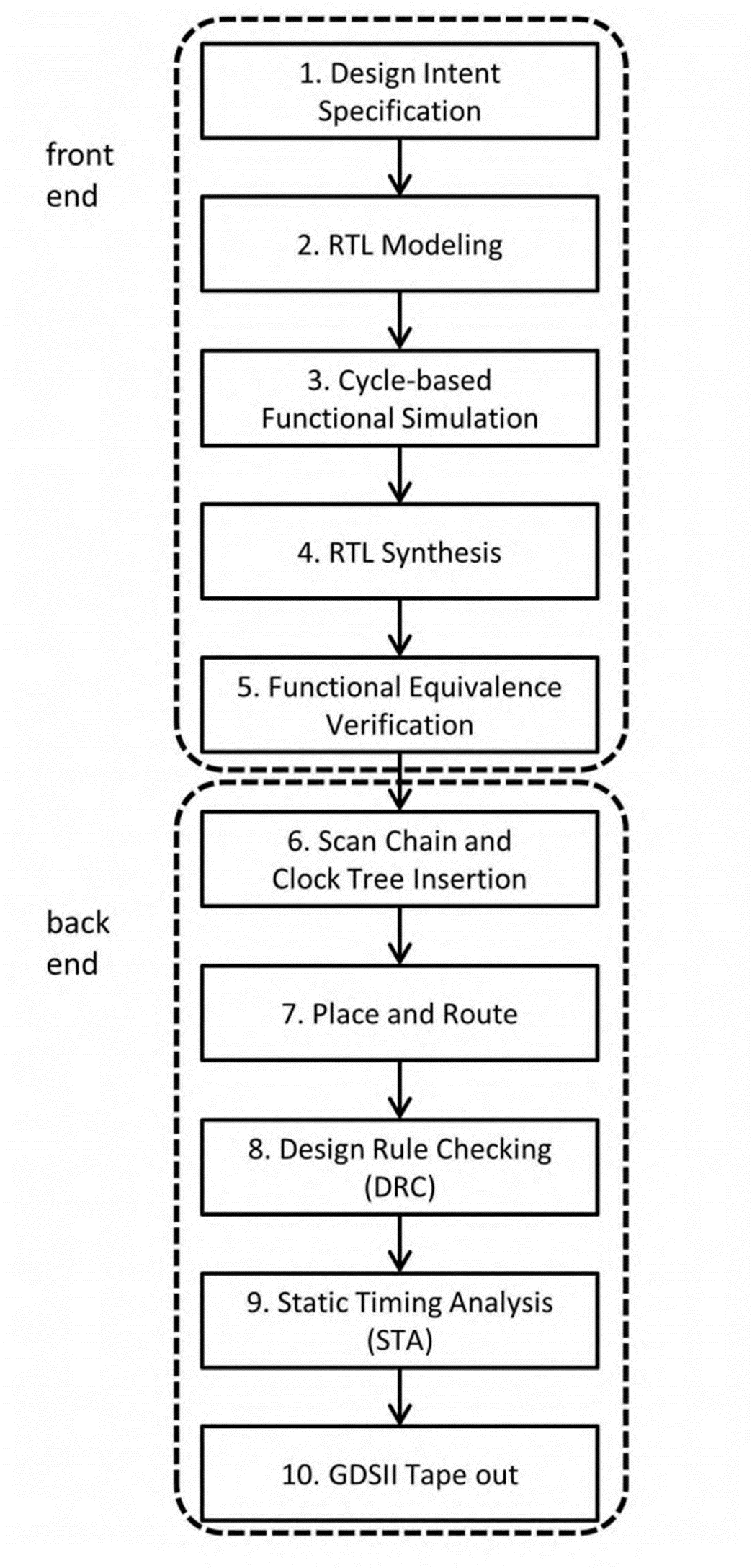

作为逻辑工程师,在FPGA和数字IC开发和设计中,一般采用verilog,VHDL或SystemVerilog等作为硬件描述语言进行工程设计,将一张白板描绘出万里江山图景。

2023-09-04 10:10:56 1187

1187

上一篇文章《暗藏玄机的SV随机化》介绍了SystemVerilog的各种随机化方法,本文将在其基础上引入SystemVerilog的随机约束方法(constraints)。通过使用随机约束,我们可以将随机限制在一定的空间内,有针对性地提高功能覆盖率。

2023-09-24 12:15:30 396

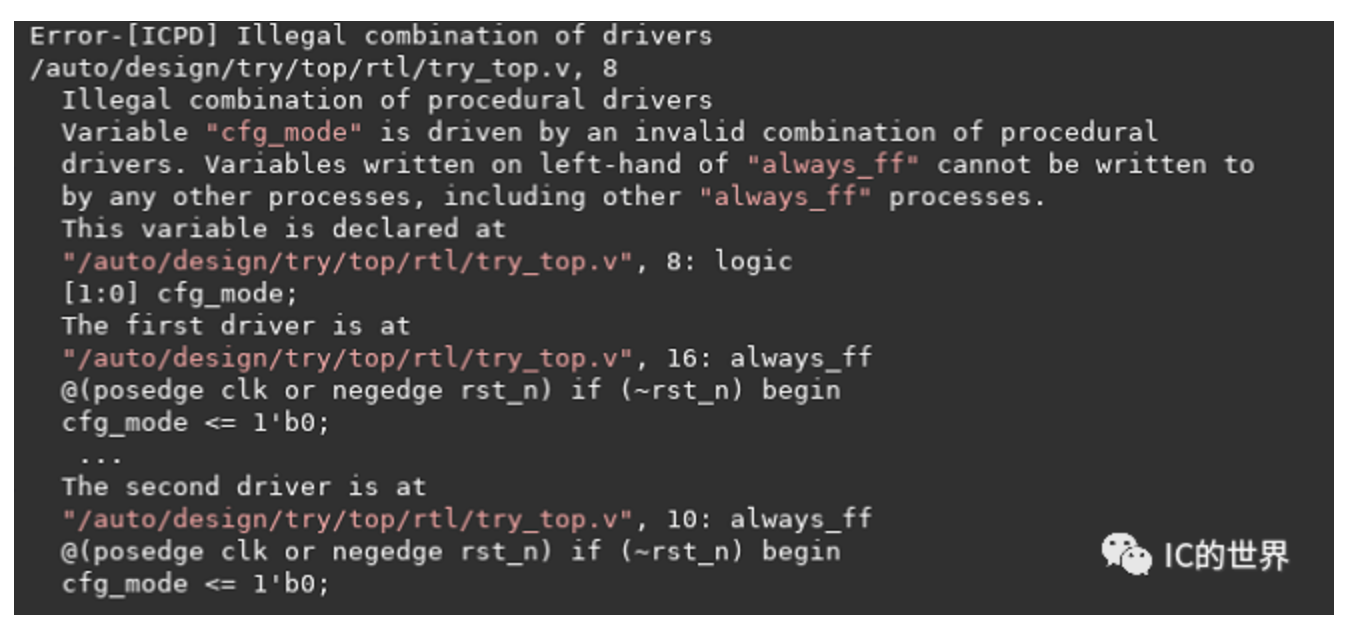

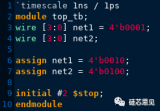

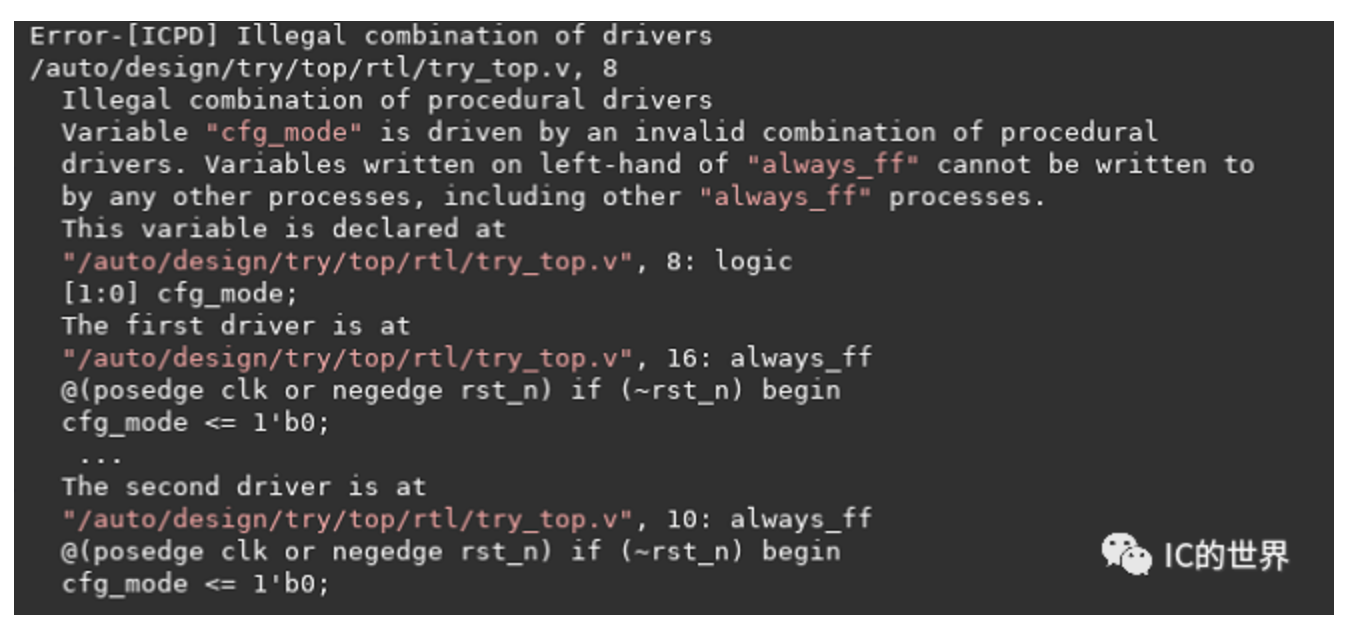

396 在systemverilog协议中,logic定义四态值,即向量(vector)的每个位(bit)可以是逻辑0, 1, Z或X,与verilog协议中的reg很接近。但是logic有个很明显的优势,不允许多驱动。

2023-09-28 17:34:37 1928

1928

谈到SystemVerilog,很多工程师都认为SystemVerilog仅仅是一门验证语言,事实上不只如此。传统的Verilog和VHDL被称为HDL(Hardware Description

2023-10-19 11:19:19 342

342

在systemverilog协议中,logic定义四态值,即向量(vector)的每个位(bit)可以是逻辑0, 1, Z或X,与verilog协议中的reg很接近。但是logic有个很明显的优势,不允许多驱动。

2023-10-26 09:32:24 324

324

本文分享一些SystemVerilog的coding guideline。

2023-11-22 09:17:30 272

272

FPGA(现场可编程门阵列)的编程涉及到三种主要的硬件描述语言(HDL):VHDL(VHSIC Hardware Description Language)、Verilog以及SystemVerilog。这些语言在FPGA设计和开发过程中扮演着至关重要的角色。

2024-03-15 14:36:01 89

89 2024年3月初,在美国硅谷举办的DVCon2024上,IEEE-SA和Accellera联合宣布通过IEEE Get Program可以免费获取IEEE 1800-2023 SystemVerilog语言参考手册。

2024-03-20 13:52:04 198

198

电子发烧友App

电子发烧友App

评论