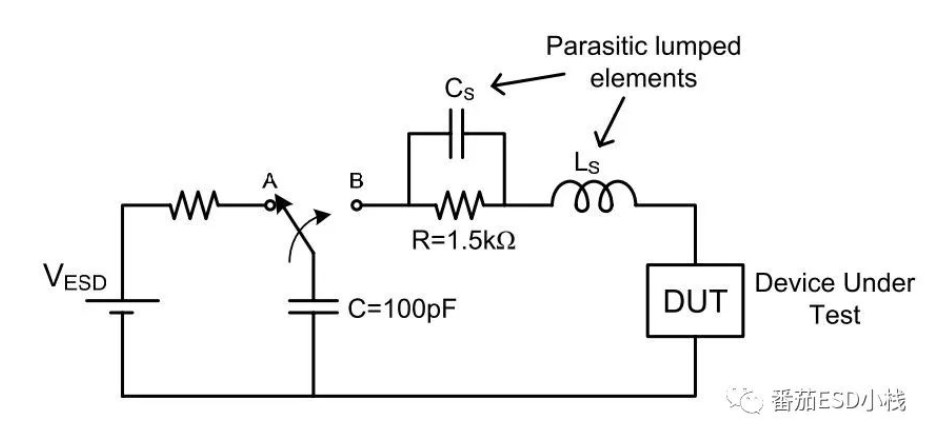

做, 使用TLP脉冲方波评估芯片的ESD性能,可以是Wafer,die或封装后成品。• 通常0V打到fail ➢ ESD-gun 静电枪测试• 模拟单板、系统外部接口在带电插拔等情况下的ESD放电,板级、系统级

2021-11-24 10:48:32

ESD测试台面搭建,图中红圈的电阻需要接吗。水平和垂直耦合面是要接的,红圈中为啥也有470k电阻?

2021-03-03 23:20:04

系统级ESD现象和器件级ESD现象有什么差异?ESD事件保护的系统级设计方法有哪几种?

2021-06-08 07:20:49

能够承受ESD的冲击,并继续正常工作。ESD保护方法为了给电子系统提供ESD保护,可以从不同的角度来着手。一种方法是在半导体芯片内建ESD保护架构。不过,日趋缩小的CMOS芯片已经越来越不足以承受进行

2011-07-05 14:19:03

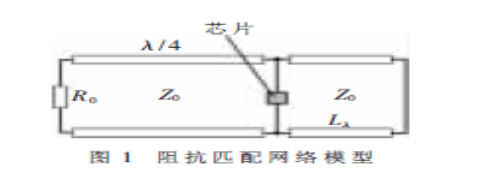

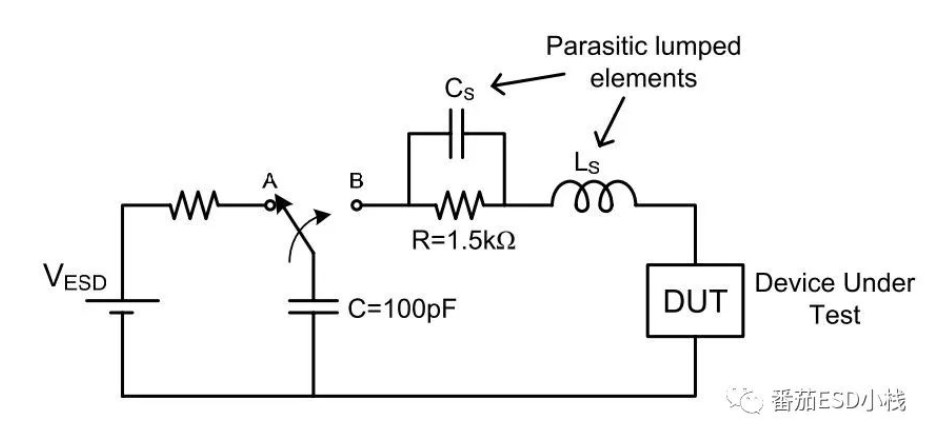

水平,以便使那些采用了对ESD越来越敏感的IC的终端产品保持高可靠性。 ESD波形 以系统级的方法来定义典型的ESD事件所采用的最常见的波形,是以其亚纳秒上升时间和高电流电平(参见图1)为显著特征

2010-08-18 19:44:07

作者: TI专家 Bruce Trump翻译: TI信号链工程师 Michael Huang (黄翔) 我们已经把芯片级的ESD性能写入数据手册多年,但这些参数仅适用于在芯片焊接到电路板前。那么在

2018-09-21 09:54:40

原理为了防止ESD损伤芯片,一般芯片内部各个引脚(除GND pin 或NC pin 外)都有对地二极管,简单的等效电路如下图所示:利用二极管的正向导通性测试芯片各引脚二极管特性,假设二极管因为ESD 或高压被反向击穿造成损坏,那么芯片对应管脚一般表现为对地短路。4)测试方法将万用表红表笔接地,黑表

2022-01-18 09:30:14

本帖最后由 testest 于 2020-5-17 20:51 编辑

芯片IC可靠性测试、静电测试、失效分析芯片可靠性验证 ( RA)芯片级预处理(PC)& MSL试验

2020-05-17 20:50:12

芯片IC可靠性测试、静电测试、失效分析芯片可靠性验证 ( RA)芯片级预处理(PC) & MSL试验 、J-STD-020 & JESD22-A113 ;高温存储试验(HTSL

2020-04-26 17:03:32

芯片功能测试常用5种方法有板级测试、晶圆CP测试、封装后成品FT测试、系统级SLT测试、可靠性测试。

2023-06-09 16:25:42

和功耗。晶圆级芯片级封装(WLCSP)的运用对减小这些设备电子组件的尺寸起到了极大的助推作用。此类新型应用包括介入性检测、医学植入体和一次性便携式监护仪。但是为了最大限度地发挥出WLCSP封装在性能

2018-10-17 10:53:16

`看到这篇对GALAXY S5的拆解,感觉真是到位,所有的元器件都列出来了iFixit、ChipWorks是一对好基友网站,前者擅长拆解维修,后者专精芯片级分析与显微观察。对于某一款设备,通常都是

2014-04-14 23:06:26

本帖最后由 eehome 于 2013-1-5 09:54 编辑

芯片级拆解:剖析新型LED灯泡设计的艺术

2012-08-20 19:45:33

芯片级维修资料分享(一)关于台式机主板维修分享

2019-08-28 14:47:21

AD7793,想请问一下INL的测试采用什么方法比较合理?

2023-12-01 07:30:13

的性能指标,设计有效的方法来测试。实际上入侵检测系统的测试是一个难度较大的问题,也是一件费时耗力的工作。对于这一工作,许多研究机构都进行了相应的研究,给出了自己的测试方法和测试结果。例如MIT的林肯实验室

2019-08-19 06:55:17

第二章 验证flow验证的Roadmap验证的目标UVM验证方法学ASIC验证分解验证策略和任务的分解AMBA可重用、灵活性、兼容性、广泛支持一.验证的Roadmap1.ASIC芯片项目流程市场需求

2021-11-01 06:28:47

晶圆级芯片级封装; 49 bumps; 3.29×3.29×0.54mm(包括背面涂层)

2022-12-06 06:06:48

PCB布板时的ESD保护设计方法是什么?

2023-04-06 17:49:21

SiC SBD 晶圆级测试 求助:需要测试的参数和测试方法谢谢

2020-08-24 13:03:34

USB元件提供ESD保护。 业界制定了不少针对不同瞬态干扰的ESD标准,比如针对系统级ESD事件的IEC61000-4-2国际标准。另外还有一些元器件级的ESD敏感度测试标准,如人体模型(HBM)和机器

2013-12-27 16:21:39

【芯片级维修工程师】电脑主板维修范例大全 下载 (474.94 KB)2010-11-28 17:16 本帖隐藏的内容需要

2010-12-02 21:47:40

`iPhone4S手机芯片级拆解`

2012-08-20 21:09:03

Circuits第 3 页 共 127 页8.2 动态浮接闸级之ESD 防护威廉希尔官方网站

2011-02-24 09:55:18

。芯片级一般用HBM做测试,而电子产品则用IEC 6 1000-4-2的放电模型做测试。为对 ESD 的测试进行统一规范,在工业标准方面,欧共体的 IEC 61000-4-2 已建立起严格的瞬变冲击抑制标准

2019-04-23 16:38:13

;该系统主要被用于产品的研发与测试分析 这一类ESD 可以理解为板级的ESD 3. 随着中美贸易不断升级,2017年开始国家加大半导体,芯片等相关公司的投资, 在武汉,厦门 合肥 南京 杭州成都等城市

2020-02-29 16:39:46

。生产嵌入式芯片的厂家也已有百家之多。然而,嵌入式芯片的应用开发方式基本上还是一直采用基于芯片级的应用开发方式。由于不同生产厂家生产的芯片其系统构架和指令系统不一样,嵌入式芯片应用的多样性和广泛性导致

2012-11-19 11:53:48

进行芯片级拆解与比对,详细的拆解进行横向比较,为您更清楚地揭示其中的微妙差异。Nook Table这里我们为您呈现的是Nook Tablet,这个薄板有很酷的一个大夹子。同样,它的内部也很酷,我们来看

2012-02-03 14:54:54

什么是EMI?ESD噪声抑制方法有哪些?

2021-06-04 06:36:14

本帖最后由 eehome 于 2013-1-5 09:46 编辑

保护元件免受ESD的方法 为了给电子系统提供ESD保护,可以从不同的角度来着手。一种方法是在半导体芯片内建ESD保护架构

2013-01-04 14:58:24

为了给电子系统提供ESD保护,可以从不同的角度来着手。一种方法是在半导体芯片内建ESD保护架构。不过,日趋缩小的CMOS芯片已经越来越不足以承受进行内部2KV等级的ESD保护所需要的面积。真正有效

2014-02-14 10:30:16

时钟频率的不断提高使相位噪声和抖动在系统时序上占据日益重要的位置。本文介其概念及其对系统性能的影响,并在电路板级、芯片级和单元模块级分别提供了减小相位噪声和抖动的有效方法。

2019-06-05 07:13:30

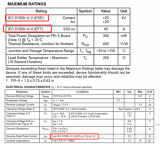

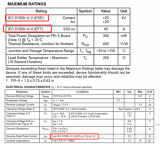

[/td][td=140]芯片级系统级上升时间2-10ns0.7-1ns峰值电流/KV0.66A3.75A2.测试设备不同MK2-芯片级静电枪-系统级3.测试方法不同芯片级HBM测试需要对IC按照

2020-10-16 16:36:22

0.7-1ns峰值电流/KV0.66A3.75A2.测试设备不同,MK2芯片级,静电枪系统级3.测试方法不同芯片级HBM测试需要对IC按照POWER,GND,IO进行分组测试系统级HBM测试分成两种方式:1

2022-09-19 09:53:25

。芯片级一般用HBM做测试,而电子产品则用IEC 6 1000-4-2的放电模型做测试。为对 ESD 的测试进行统一规范,在工业标准方面,欧共体的 IEC 61000-4-2 已建立起严格的瞬变冲击抑制标准

2021-08-10 07:00:00

我们已经把芯片级的ESD 性能写入数据手册多年, 但这些参数仅适用于在芯片焊接到电路板前。那么在电路板上的ESD性能如何呢?

2021-04-09 06:00:54

基于无线测试配置来研究和比较各种多DUT测试方案

2021-05-10 06:44:44

摘要:文中通过分析目前电子设备板级热仿真建模威廉希尔官方网站

存在的不足,基于设计数据共享威廉希尔官方网站

,系统研究了PCB 板卡的叠层铜分布和热过孔仿真建模对芯片温度预测精度带来的较大影响,并结合实际应用给出了仿真优化

2018-09-26 16:22:17

对于单颗的芯片,目的验证其从封装完成,经过储存、运输直到焊接到系统板之前的静电防护水平,建议采用芯片级的测试方式,测试电压通常在2000V左右。对于系统板和整机,为验证其抗干扰的能力,建议用静电枪测试,接触式放电8KV,空气放电15KV.

2022-09-19 09:57:03

过关,不过,对小型电子产品进行静电屏蔽也比较容易,只需在机壳上面贴一层薄薄的导电薄膜(或涂一层可导电的油漆)即可,因此,对敏感器件进行静电屏蔽是小型电子产品对付ESD测试比较常用的方法。

2021-01-08 16:08:07

脉冲有没有正确送到CPU芯片的复位脚。 4.查总线 数据总线、地址总线、控制总线的任何一根开路或短路都可引发故障,可以通过测试平行总线的对地电阻比较某路有没有故障来判断,或者观察各路总线的波形来判断。 5.查接口芯片 接口芯片是坏得最多的一类元件,可通过代换或专用仪器检测来判断是否损坏

2012-04-18 16:31:12

的集成度。现在一块单一的芯片就集成了从ADC转换到中频调制输出的大部分功能。因此,模块级和芯片级的射频测试点会减少很多,发射器系统级和天线端的测试和故障分析就变得更加重要。

2019-06-28 07:44:08

Ramon Navarro简介本应用笔记说明用于从印刷电路板(PCB)移除引线框芯片级封装(LFCSP)的建议程序。LFCSP符合JEDEC MO-220和MO-229外形要求。本应用笔

2018-10-24 10:31:49

怎样在IAP源码的基础上做芯片级的改动呢?STM32的启动过程是怎样的?

2021-11-02 06:13:23

面积,而硅片面积的增加增大了IC设计的成本。 当前,新的ESD英国威廉希尔公司网站

解决了这个问题:镇流电阻可以通过高效的面积使用方法来实现。新的设计方法能确保实现较小的I/O,更小的IC芯片尺寸,因而每一个晶圆上

2012-12-11 13:39:47

你好,我寻求CSG325 0.8mm间距BGA封装的布局信息。我想找到类似于UG112第87和88页中的建议,其中列出了焊盘尺寸,焊接掩模开口,焊盘尺寸等。是否有像CSG325这样的芯片级封装的类似

2019-04-12 13:51:20

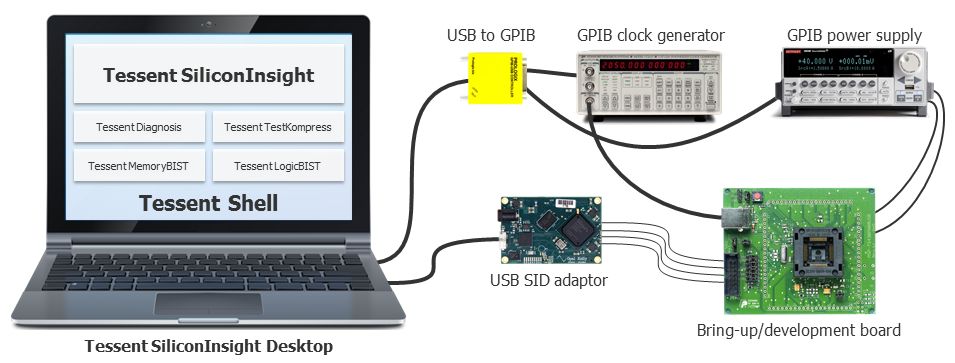

如何利用EDA工具去提高系统级芯片测试的效率?

2021-05-07 06:08:41

。这一规范的ESD保护电压水平高很多,因此与HBM不兼容。HBM规范要求的测试集中在500V。另一方面,IEC中的空气放电方法要求的测试可以超过15,000V。这意味着,在芯片组的ESD保护能力

2019-05-22 05:01:12

`浅析ESD 防护与ESD 防护器件中心议题:• 静电释放的危害和ESD 保护的重要性• 相对于压敏MOV和聚合物PESD,硅基ESD 在ESD 保护方面的比较优势解决方案:•硅基ESD采用硅芯片

2017-07-31 14:59:33

本帖最后由 llgzcts 于 2012-4-8 01:22 编辑

介绍一个关于电脑主板维修的好资料的下载地址:电脑硬件芯片级维修培训实用资料大全(650M)实用资料打包下载网实用资料打包下载网

2012-04-08 01:03:34

。芯片级一般用HBM做测试,而电子产品则用IEC 6 1000-4-2的放电模型做测试。为对 ESD 的测试进行统一规范,在工业标准方面,欧共体的 IEC 61000-4-2 已建立起严格的瞬变冲击抑制

2020-07-07 08:26:54

等。芯片级一般用HBM做测试,而电子产品则用IEC 6 1000-4-2的放电模型做测试。为对 ESD 的测试进行统一规范,在工业标准方面,欧共体的 IEC 61000-4-2 已建立起严格的瞬变冲击

2018-10-23 16:08:45

。芯片级一般用HBM做测试,而电子产品则用IEC 6 1000-4-2的放电模型做测试。为对 ESD 的测试进行统一规范,在工业标准方面,欧共体的 IEC 61000-4-2 已建立起严格的瞬变冲击抑制标准

2019-04-27 08:00:00

计算机芯片级维修中心(芯片级维修培训教材)

2009-04-05 01:17:54

SRAM中晶圆级芯片级封装的需求

2020-12-31 07:50:40

金属触点ESD测试问题像图中这种串口通讯触点(4.2V,TX,RX),如果还是不能通过空气放电15KV,接触放电8KV,然后板子空间有限,这种情况如何改善能一步通过ESD测试?

2023-02-02 11:01:38

飞凌干货丨6步讲解应对ESD基本方法ESD试验作为EMC测试标准的一项基本测试项目,往往由硬件工程师来考虑。对于整机来说,ESD抗干扰能力不仅仅来自芯片的ESD耐压和PCB的布局布线,与工艺结构也有

2021-02-07 13:22:05

(full-waverectifiers)等。 1 比较器的设计 本文设计的比较器是一个高增益的三级比较器,第一级为普通差分放大器,第二级为折叠式共源共栅差分放大器,第三级为共源极放大器和一个推挽式反向放大器

2011-08-18 09:20:12

摘要:介绍了一种研究器件和电路结构在EsD期间新的特性测试方法—一TLP法,该方法不仅可替代HBM测试,还能帮助电路设计师详细地分析器件和结构在ESD过程中的运行机制,有目的

2010-04-29 10:48:53 29

29 福禄克DTX-1800维修维修内容:主机屏幕爆屏、无法开机、测试指标偏移、无法充电、适配器接口损坏更换、电池内阻增大更换、原厂校准、芯片级维修等,各种疑难杂症。

2023-10-10 16:11:30

服务范围大规模集成电路芯片检测标准●JESD22-A103/ A104/ A105/ A108/ A110●J-STD-020●JS-001/002●JESD78检测项目(1)芯片级可靠性验证试验

2024-03-14 16:28:30

论述了一种测试混合信号集成电路衬底噪声波形的方法采用电压比较器利用衬底电压对比

较器状态的影响对噪声作出统计测试根据测试结果重建噪声波形设计了一

2010-08-29 16:08:46 14

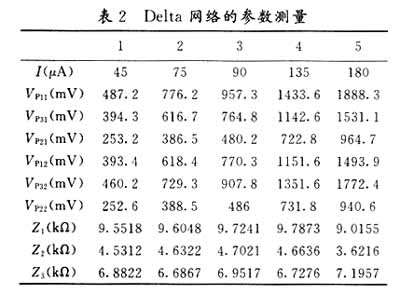

14 基于IEEE1149.4的测试方法研究

根据混合信号边界扫描测试的工作机制,提出了符合1149.4标准的测试方法,并用本研究室开发的混合信号边界扫描测试系统进行了测试

2009-05-04 22:29:18 1007

1007

测试一直是静电与电磁防护研究的瓶颈. 针对ESD 辐射场 测试问题, 提出了能量有效带宽和动态范围有效带宽的概念, 并根据IEC61000

2011-06-20 16:45:24 29

29 《开关电源维修技能实训:芯片级》共8章,系统讲解了电源中的各种元器件的检测方法及常用维修工具的使用方法、基本电路、电脑电源分析与检修、显示器电源分析与检修、UPS电源分

2011-10-21 17:10:14 0

0 清晰易懂 表明esd如何发生,如何避免esd

2016-02-22 18:05:45 0

0 蓄电池测试系统中SVPWM与SPWM的比较研究

2016-03-30 14:59:59 15

15 ESD模型和测试标准

2016-12-10 14:02:20 17

17 基于电压比较器衬底噪声的测试方法

2017-01-22 13:38:08 5

5 IT硬件能耗测试方法应用研究_黄植勤

2017-03-19 11:27:34 2

2 STUN协议的实现原理及测试方法研究_吴任国

2017-03-19 11:28:02 0

0 MEMS制造中精确测量薄膜厚度的方法研究与比较_陈莉

2017-03-19 18:58:18 2

2 翻译: TI信号链工程师 Michael Huang (黄翔) 我们已经把芯片级的ESD性能写入数据手册多年,但这些参数仅适用于在芯片焊接到电路板前。那么在电路板上的ESD性能如何呢? 我们用多次电击若干个芯片的每个引脚的方法来确保其ESD性能。它模拟了在触摸和装配过程中芯片遭遇的恶劣情景。

2017-04-08 04:09:11 2932

2932

CE标志测试以满足欧共体理事会指令89/336/EEC要求测试根据EN 61000-4-2。EN 61000-4-2是由CENELEC和他们使用IEC标准IEC 61000-4-2作为ESD测试标准

2017-08-31 11:05:20 33

33 ADI公司的iCoupler产品提供了一种替代光耦合器的隔离 解决方案,具有出色的集成度、性能和功耗特性。一个 iCoupler隔离通道包括CMOS输入和输出电路与一个芯片级 变压器(见图1)。由于

2017-09-13 08:08:03 4

4 每一个输入/输出相对于其他所有的输入/输出的正向ESD脉冲测试。

2018-11-24 09:23:07 17325

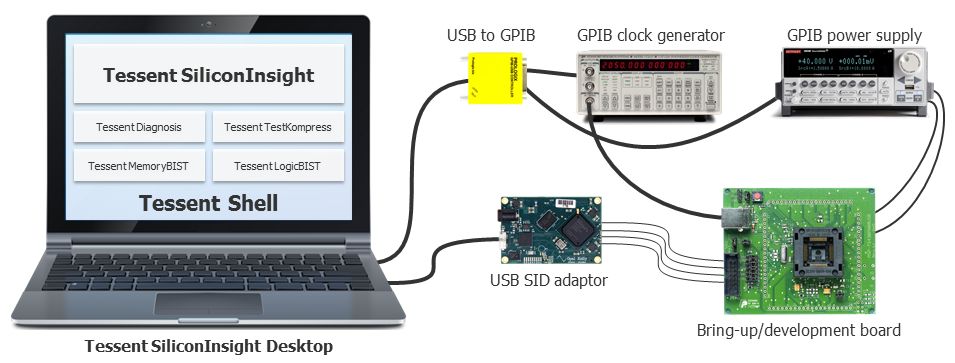

17325 尽管业界广泛采用IJTAG(IEEE 1687)测试架构进行芯片级测试,但很多公司在芯片级测试向量转换,以及自动测试设备 (ATE) 调试测试保留了非常不同的方法。因此,每个特定芯片必须由 DFT 工程师编写测试向量,然后由测试工程师进行转换,以便在每种测试仪类型上调试每个场景。

2019-10-11 15:36:23 3515

3515

芯片级守护 华为P30系列如何从底层保证通信安全?

2019-08-28 11:18:28 3901

3901 在做ESD放电测试时通常采用两种方法:接触放电和空气放电。

2019-09-02 08:49:24 4173

4173

根据AEC-Q200-002,HBM的ESD测试流程如图3所示,级分类如表1所示。根据图3的流程进行测试,耐电压的分级如表1所示进行分类。

2020-07-01 15:33:31 3731

3731

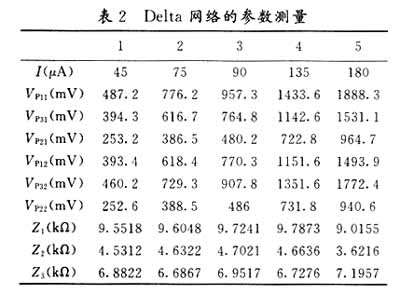

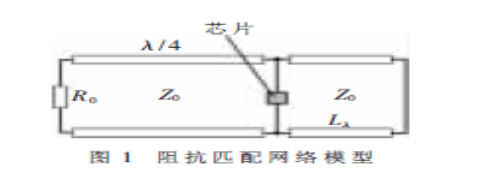

提出一种用于UHF无源RFID标签芯片阻抗测试的新方法。利用ADS仿真软件对测试原理进行了仿真并实际制作了测试板。利

2021-03-22 17:16:21 3021

3021

作者: TI专家 Bruce Trump

翻译: TI信号链工程师 Michael Huang (黄翔)

我们已经把芯片级的ESD性能写入数据手册多年,但这些参数仅适用于在芯片焊接

2021-11-22 16:13:17 2835

2835 Fairchild 模拟开关产品 ESD 测试方法概述

2022-11-14 21:08:28 0

0 ESD和浪涌问题往往是基带工程师最头疼的问题,因为测试标准严苛,问题神出鬼没。特别是ESD问题,没有解决问题的标准路径,只能靠反复地构思方案并验证。

2023-03-14 14:36:20 12660

12660 ESD按照发生阶段主要分为两类:1.发生在芯片上PCB板前的过程中(生产 、封装、运输、销售、上板)这类ESD事件完全需要由芯片自己承受。

2023-05-16 16:21:31 7698

7698

芯片功能测试常用5种方法有板级测试、晶圆CP测试、封装后成品FT测试、系统级SLT测试、可靠性测试。

2023-06-09 15:46:58 1666

1666

ESD静电放电在芯片实际使用过程中越来越影响到芯片的可靠性,是影响芯片质量和性能的重要因素之一。因此,ESD抗干扰测试是非常重要的,防止ESD对芯片造成损坏。

2023-10-08 16:24:01 565

565 ESD和浪涌问题往往是基带工程师最头疼的问题,因为测试标准严苛,问题神出鬼没。特别是ESD问题,没有解决问题的标准路径,只能靠反复地构思方案并验证。

想要尽量避免以上问题,就必须选择合适的防护器件,设计上做足防护措施。本文告诉你ESD和浪涌的测试标准,测试方法,以及如何选择TVS器件。

2023-10-09 12:18:28 2401

2401

电子发烧友网站提供《IEC61967-2芯片级RE测试应用笔记.pdf》资料免费下载

2023-12-14 10:03:06 0

0

电子发烧友App

电子发烧友App

评论