为了在嵌入式系统设计中实现对SDRAM存储器的访问,本文提出了一种基于AMBA-AHB总线规范的SDRAM控制器设计方案。方案首先简要介绍了AMBA总线规范,然后在完成整个存储控制器的整体框架

2014-01-02 13:59:42 4099

4099

PDMA中INTSTS寄存器中有个标志位是TEIF

描述为:

描述符表空中断标志(只读)

该位指示PDMA控制器已经完成了所有表传输,工作在停止模式。用户可以读寄存器TEIF来指示哪个通道已经完成

2023-06-13 06:49:25

基于SDRAM控制器实现FPGA模块化和通用性的解决方案设计

2020-12-22 07:58:55

上找到了几个sdram控制器,但是我无法存储或读取任何内容。我问的是你有没有改变sdram的工作代码并使它像sram那样我可以测试我的硬件?你有什么想法我怎么测试芯片是否存活?最好的祝福。我喜欢

2019-05-16 13:10:57

SDRAM控制器用户手册主要内容包括功能特点、整体框图、工作原理、信号定义、参数介绍、GUI 调用、接口时序等。主要用于帮助用户快速了解高云半导体 SDRAM 控制器的产品特性、特点及使用方法。

2022-10-08 07:48:27

描述此参考设计演示了如何实现 SDRAM 存储器并通过接口连接到高性能微控制器 TM4C129XNCZAD。为了实现此设计,其中采用了该微控制器的 EPI 接口来连接 256Mbit SDRAM

2018-08-30 09:31:51

SDRAM的基本工作原理是什么SDRAM的基本读写操作步骤是什么一种简单的通用SDRAM控制器的实现

2021-05-10 06:26:44

在STM32微控制器中如何使用PWM?

2021-09-24 10:02:51

ARD智能控制器的功能特点有哪些?如何去使用ARD智能控制器?ARD智能控制器在风机及水泵中的应用是什么?

2021-07-06 07:07:35

PrimeCell SDRAM控制器是一款符合高级微控制器总线架构(AMBA)的片上系统(SoC)外围设备,由ARM开发、测试和许可。

PrimeCell SDRAM控制器将SDRAM连接到嵌入式SoC ASIC和ASSP。

2023-08-02 18:13:06

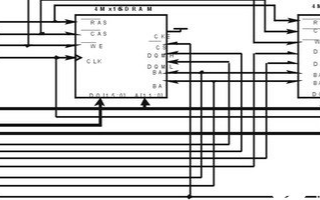

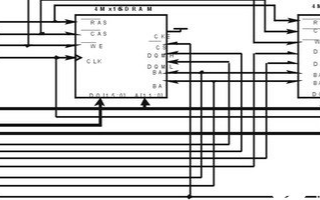

、锁相环等硬件资源。使用这些特性,可以更加容易地设计性能可靠的高速DDRSDRAM存储器控制器。 1 DDR SDRAM 在嵌入式系统中的应用 图1是DDR SDRAM在高速信号源系统中的应用实例

2018-12-18 10:17:15

DDR_SDRAM控制器的VHDL代码已经测试

2016-08-24 16:49:35

FPGA之SDRAM控制器设计(二):刷新这次要来解决上次留下来的刷新问题,在100us后首先要经过两次刷新才进行模式寄存器设置。这颗SDRAM芯片需要每隔64ms对8192行(列地址10-位,行

2021-07-30 07:48:42

本次发布三例 SDRAM 控制器参考设计及 IP Core Generator 支持调用SDRAM 控制器 IP。 1. 32-bit SDRAM Controller for device

2022-10-08 07:59:17

应用程序:M480系列微控制器(MCU)通过PDMA接收UART数据时使用这个示例代码。

BSP 版本: M480 BSP CMSIS V3.05.001

硬件: NuMaker-PFM-M487

2023-08-31 09:18:37

应用程序:M480系列微控制器(MCU)通过PDMA接收UART数据时使用这个示例代码。

BSP 版本: M480 BSP CMSIS V3.05.001

硬件: NuMaker-PFM-M487

2023-08-31 10:02:28

基于FPGA的SDRAM控制器设计(三)读写作者:小周 本文为明德扬原创及录用文章,转载请注明出处! SDRAM控制器设计的主要功能是能对SDRAM进行读写操作,本工程实现了SDRAM的初始化、自动

2020-04-23 11:31:47

在这一讲中,Kevin先带着大家了解一下我们这一套视频教程《SDRAM那些事儿第一季—轻松设计SDRAM控制器》中所要讲的这个项目。这个项目总的来讲,就是设计一个简单的SDRAM控制器,PC机通过

2017-05-08 22:14:21

第六讲已介绍完SDRAM的写模块,而在这一讲中,我们会接着介绍SDRAM控制器的读模块。在搞定读模块之后,就相当于SDRAM控制器部分已经搭建好了,想一想还是很期待的哦,哈哈,大家先别急。在这一讲中

2017-05-08 22:28:13

终于到第九讲了,第九讲是这套《轻松设计SDRAM控制器》的最后一讲。相信大家也是非常的期待这套教程的终结,在前面的8讲内容,我们已经介绍完了SDRAM控制器、串口部分和命令解析模块。在第九讲中,我们

2017-05-08 22:38:37

是至关重要的一点。讲完第五讲之后,整个SDRAM控制器的各模块就可以说很清晰了。特别是掌握了仲裁机制后,对于SDRAM的刷新操作、写操作、读操作三个操作之间的控制也可以非常流畅的控制起来了。所以在第五

2017-05-08 22:22:44

SDRAM读写的完整项目。在第三讲中,我们已经完成了串口的收发功能。在本讲中,我们先来对串口发送过来的命令和数据进行解析和分离。在搞定读模块之后,就相当于SDRAM控制器部分已经搭建好了,想一想还是很期待

2017-05-08 22:31:58

SDRAM中写入两行数据,那什么时候可以退出仲裁状态机的写状态:数据已经写完;SDRAM需要进行刷新操作;数据未写完,需要激活下一行继续写。这是我们SDRAM控制器写模块使用到的状态图,这样可以完美解决我们

2017-05-08 22:25:30

的SDRAM控制器哦!!!!自己也是一时兴起,看到很多威廉希尔官方网站

类的微信公众号,所以自己也开通了微信公众号【开源骚客】(微信号:OpenSoc)微信公众号,主要是用来分享一些不适合博文写出来的东西,博文可能大家

2017-05-08 22:20:54

,但由于接触FPGA时间不长,虽认真研读过各种关于SDRAM的资料,却仍然无法使用Verilog设计出一个工作正常的SDRAM控制器。在本文中,【开源骚客】将会先引入一个SDRAM控制器简单例子的演示

2016-10-16 23:04:43

第1节 SDRAM读写控制器--作者:小黑同学本文为明德扬原创及录用文章,转载请注明出处!1.1 总体设计1.1.1 概述同步动态随机存取内存(synchronousdynamic

2020-10-15 15:16:02

嗨,我使用MIG 2.1构建了两个DDR2 SDRAM控制器来进行Ping Pong缓冲。该设备是virtex4FX60FF1152和ISEver是10.1。当它在设备上运行时,控制器

2020-06-02 16:58:51

当我使用 PE 微型调试器在微控制器中闪存程序时,我们在 216 处收到以下错误 ieruntime 错误并且 GDB 已终止,因此我们无法在控制器中闪存程序。请解决问题

2023-04-17 06:03:53

使用Verilog实现基于FPGA的SDRAM控制器

2012-08-20 19:35:27

可以选中相应的外接设备。本实验流程:禁止看门狗—>nand flash中前4k字节复制到芯片内部SRAM中执行—>通过存储控制器初始化外接的SDRAM—>复制

2022-05-07 09:54:28

本文介绍一种通用SDRAM控制器的FPGA模块化解决方案。

2021-05-07 06:42:49

求大佬介绍一种通用SDRAM控制器的FPGA模块化解决方案

2021-04-08 06:40:34

我们想在我们的一个物联网应用项目中使用 MIMXRT1176DVMAA。为此,我们不需要外部 SDRAM。所以,我们想在没有 SDRAM 的情况下运行这个控制器。

根据数据表,该控制器具有内部 2MB SDRAM,因此我们要使用它。

你能证实这一点吗?

2023-05-04 08:12:41

。DDR的时序与SDRAM是相似的,学好SDRAM后,理解DDR2和DDR3就非常容易了。2、至简设计代码实现(附录部分代码)下面是使用至简设计法实现的SDRAM控制器,该控制器使用了四段式状态机,其他信号

2017-08-02 17:43:35

控制器设计—初始化设计》中的“SDRAM中心对齐原则”部分进行学习。另外,本模块锁定输入时钟后,将产生LOCK指示信号,此信号用于其它模块的复位信号。我们可以理解为,在时钟稳定之前,其它模块都处于复位

2020-04-15 14:43:50

进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行类FIFO接口的封装,屏蔽掉了DDR3 IP核复杂的用户接口,为DDR3数据流缓存的实现提供便利。系统测试表明,该

2018-08-02 09:34:58

当A/D转换结束的时候,转换结果被存储在ADDR寄存器中,同时VALID位被置‘1’。如果ADCR.PTEN被置‘1’,A/D控制器将产生PDMA请求(P_nDRQ)来传输数据,PDMA通过响应P_nDRQ请求来读走A/D转换的数据,以此达到CPU无干预情况下的连续A/D转换。

2023-06-14 08:26:07

本文提出了一种基于FPGA的SDRAM控制器的设计方法,并用Verilog给于实现,仿真结果表明通过该方法设计实现的控制器可以在FPGA芯片内组成如图1所示的SDRAM接口,从而使得系统用户对SDRAM的操作非常方便。

2021-04-15 06:46:56

本文利用C-NOVA公司数字电视MPEG-2解码芯片AVIA9700内置的SDRAM控制器所提供的时序补偿机制,设计了一个方便使用的内存时序测试软件工具,利用这个工具,开发测试人员可在以AVIA9700为解码器的数字电视接收机设计和生产中进行快速诊断,并解决SDRAM的时序问题。

2021-06-07 06:19:01

基于FPGA的SDRAM控制器包括哪些部分呢?如何去实现一种基于FPGA的SDRAM控制器设计呢?

2021-11-04 06:47:44

SDRAM控制器基本操作原理是什么?如何去设计并实现一种SDRAM控制器?

2021-06-07 06:01:39

如何对电机控制器进行测试?

2021-04-28 07:19:42

如何解决SDRAM控制器设计刷新的问题?

2021-11-04 07:20:02

我移植网上的一个sdram vga的代码到ep4ce6e22c8n开发板上,它里面的sdram控制器是tequan写的,但是我移植后,却得不到代码要的效果,sdram读写出来的数据有错,调了好久也

2014-04-03 16:23:55

DDR SDRAM在嵌入式系统中有哪些应用?DDR SDRAM的工作方式有哪几种?怎样去设计DDR SDRAM控制器?

2021-04-30 07:04:04

SDRAM控制器的主要特点是什么?SDRAM控制器的状态流程是怎样的?SDRAM控制器有哪些功能?

2021-06-26 07:35:01

用什么方法去测试SDRAM控制器的性能?PDMA的结构及工作原理是什么?RTL仿真的顺序是什么?

2021-04-08 06:19:50

本帖最后由 upmcu 于 2012-7-28 15:07 编辑

截图:LED显示控制系统中SDRAM控制器的设计.pdf基于FPGA的DDR2+SDRAM数据存储研究.pdf基于FPGA

2012-07-28 14:40:53

会达到上百帧,这样保证处理的数据尽量是最新的一帧。 好了,进入正题了,我们在已有的SDRAM burst1/2/4/8的控制器代码下怎么修改成full-page burst 模式,需要注意点什么细节

2014-09-03 00:08:33

SDRAM(同步动态存储器)是一种应用广泛的存储器,具有容量大、数据读写速度快、价格低廉等优点,特别适合那些需要海量存储器的应用领域,例如视频方面。那么有谁知道,高速SDRAM控制器的视频有哪些吗?

2019-08-09 06:23:43

简要介绍了SDRAM工作原理并认真研究了Altera提供的SDRAM控制器,根据实际系统使用需要加以修改简化,设计了对修改后控制器进行操作的状态机。采用全页突发读写模式,每次读/写

2009-12-26 17:02:56 70

70 DDR2 SDRAM控制器的设计与实现

本文介绍了&&," -&,+. 的基本特征!并给出了一种&&," -&,+. 控制器的设计方法!详述了其基本结构和设计思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 本文采用Altera 公司的Stratix 系列FPGA 实现了一个三端口非透明型SDRAM 控制器,该控制器面向用户具有多个端口,通过轮换优先级的设计保证了多个端口平均分配SDRAM的带宽且不会降

2010-03-03 14:37:14 11

11 简要介绍了SDRAM工作原理并认真研究了Altera提供的SDRAM控制器,根据实际系统使用需要加以修改简化,设计了对修改后控制器进行操作的状态机。采用全页突发读写模式,每次读/写后自动

2010-07-21 17:31:37 38

38 本文介绍了DDR3 SDRAM 的基本特点和主要操作时序,给出了一种基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的设计方法。详述了控制器基本结构和设计思想,分析了各模块功能与设计注意事项,并

2010-07-30 17:13:55 30

30 摘要: 介绍了SDRAM的存储体结构、主要控制时序和基本操作命令,并且结合实际系统,给出了一种用FPGA实现的通用SDRAM控制器的方案。

关键词:

2009-06-20 12:51:58 834

834

摘 要:介绍了SDRAM的特点和工作原理,提出了一种基于FPGA的SDRAM控制器的设计方法,使用该方法实现的控制器可非常方便地对SDRAM进行控制。

关键

2009-06-20 13:04:51 2075

2075 基于FPGA的高速SDRAM控制器的视频应用

0 引言 SDRAM(同步动态存储器)是一种应用广泛的存储器,具有容量大、数据读写速度快、价格低廉等优点,特别适

2009-11-04 09:56:20 847

847 定义了时钟单位阶跃信号C(n) 提出了一种利用带相对时钟坐标的逻辑方程表示逻辑信号的方法通过对所设计的DDR SDRAM控制器的读写时序的分析建立了控制器主要信号的时序表达式并利用

2011-09-26 15:34:12 39

39 SDRAM存储芯片拥有快速读写的性能,可以应用以回波模拟系统作为数据高速缓存器。SDRAM芯片是由SDRAM控制器控制的, SDRAM控制器有严格的控制时序和工作状态,可以使用有限状态机理论

2011-10-24 15:08:05 0

0 通过设计基于CPLD 的SDRAM 控制器接口,可以在STM系列、ARM系列、STC系列等单片机和DSP等微处理器的外部连接SDRAM,增加系统的存储空间。

2012-02-16 17:06:47 45

45 Xilinx FPGA工程例子源码:DDR SDRAM控制器参考设计VHDL代码

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源码:DDR SDRAM控制器verilog代码

2016-06-07 14:13:43 38

38 高速图像存储系统中SDRAM控制器的实现

2016-08-29 15:02:03 10

10 DDR2SDRAM控制器IP功能测试与FPGA验证_陈平

2017-01-07 21:45:57 3

3 基于VHDL的SDRAM控制器的实现

2017-01-22 13:43:27 12

12 DDR2SDRAM控制器在机载显控系统中的应用_孙少伟

2017-03-19 11:26:54 1

1 EPM1240的SDRAM控制器的设计

2017-10-31 08:24:31 21

21 逻辑复杂,接口方式与普通的存储器差异很大。为了解决这个矛盾,需要设计专用的SDRAM控制器,使用户像使用SRAM -样方便的使用SDRAM。考虑到控制器的通用性,本文中提出了一种通用的SDRAM控制器的FPGA设计,FPGA内部采用状态机的方式。该设计采用了AD公

2017-11-28 19:51:26 5

5 随着大规模集成电路和高速、低功耗、高密度存储威廉希尔官方网站

的发展,SDRAM动态存储器因容量大、速度快、价格低廉等优点,现已成为PC内存的主流。然而SDRAM存储器内部控制逻辑十分复杂,时序要求也非常严格,因此需要设计专门的SDRAM控制器来实现系统对SDRAM的访问。

2018-04-30 10:58:00 5066

5066

本文利用C-NOVA公司数字电视MPEG-2解码芯片AVIA9700内置的SDRAM控制器所提供的时序补偿机制,设计了一个方便使用的内存时序测试软件工具,利用这个工具,开发测试人员可在以AVIA9700为解码器的数字电视接收机设计和生产中进行快速诊断,并解决SDRAM的时序问题。

2020-03-13 07:59:00 1596

1596

本文档的主要内容详细介绍的是FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文主要包括了:FPGA读写SDRAM的实例,SDRAM控制器核心介绍,系列SDRAM数据手册

2018-12-25 08:00:00 56

56 、PSRAM、MRAM等存储芯片供应商英尚微电子解析这款比脑力更强大的DDR SDRAM控制器。 任何DRAM控制器背后的智商都是与命令时序和执

2020-07-24 14:25:27 719

719 针对SDRAM 操作繁琐的问题,在对SDRAM 存储器和全页突发式操作进行研究的基础上,提出一种简易SDRAM 控制器的设计方法。该设计方法充分利用全页式高效率存取的优点,对SDRAM 进行配置、全页突发式读写时,操作方便。在实现sDRAM 的快速批量存储方面,具有良好的应用价值。

2020-12-18 16:13:18 6

6 SDRAM作为大容量存储器在高速图像处理中具有很大的应用价值。但由于SDRAM的结构和SRAM不同,其控制比较复杂。文章详细介绍了 SDRAM存储器的结构、接口信号和操作方法,以及 SDRAM控制器

2021-01-26 15:30:52 13

13 1.SDRAM使用越来越广泛。

2.SDRAM具有存储容量大,速率快的特点。

3.SDRAM对时序要求严格,需要不断刷新保持数据。

.FPGA在电子设计中的广泛应用,使用十分灵活利用FPGA来设计自己的 SDRAM控制器。

2021-03-05 14:49:00 10

10 本文首先分析了DDR SDRAM的基本特征,并提出了相应的解决方案详细介绍了基于J EDEC DDR SDRAM规范的DDR SDRAM控制器设计方案。该控制器采用Verilog HDL硬件描述语言实现,并集成到高性能SoC中。

2021-03-28 10:57:24 18

18 EE-127:ADSP-21065L片上SDRAM控制器

2021-04-16 10:12:57 3

3 EE-163:ADSP-21161N SHARC片上SDRAM控制器

2021-04-17 16:44:17 12

12 ,SDRAM的控制逻辑复杂,使用很不方便。 为了解决这个矛盾,需要设计专用的SDRAM控制器,使系统用户象使用SRAM一样方便的使用SDRAM是十分必要的。考虑到控制器的通用性,本文提出了一种通用的SDRAM控制器的 Verilog设计,并给出了实现结果。 1 SDRAM的工作原理

2021-06-30 09:16:47 2346

2346

基于FPGA的DDR3SDRAM控制器设计及实现简介(arm嵌入式开发平台PB)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现简介资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的SDRAM控制器的设计与实现简介(嵌入式开发工程师和基层公务员)-该文档为基于FPGA的SDRAM控制器的设计与实现简介文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 09:34:59 11

11 基于FPGA的DDR3SDRAM控制器设计及实现(嵌入式开发式入门)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 13:07:09 35

35 部分的 HT32 系列单片机,包含 HT32F1755/1765/2755 等型号在内,内建了 8~12 个 channel

的 PDMA,支持内部 FLASH、SRAM、USB RAM

2022-06-07 11:05:25 1

1 SDRAM 控制器用户手册主要内容包括功能特点、整体框图、工作原理、

信号定义、参数介绍、GUI 调用、接口时序等。主要用于帮助用户快速了解

高云半导体 SDRAM 控制器的产品特性、特点及使用方法。

2022-09-15 15:17:29 0

0 实时视频SDRAM控制器的FPGA设计与实现

2022-12-30 09:21:26 3

3

电子发烧友App

电子发烧友App

评论