今天给大家分享的是:集电极开路电路、集电极开路晶体管电路、集电极开路工作原理、集电极开路TTL、集电极开路输出接线图、集电极开路优缺点。

在数字芯片设计、微控制器应用和运算放大器中,集电极开始输出通常用于驱动继电器等高负载或用于连接其他电路。

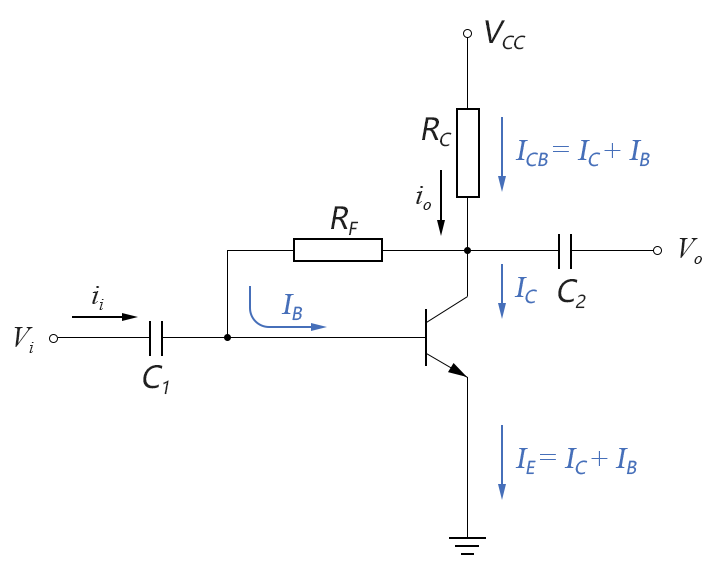

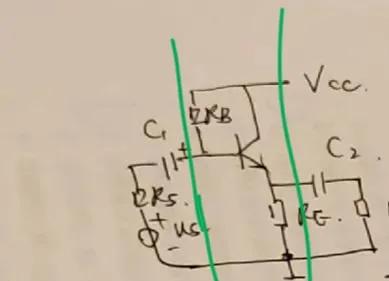

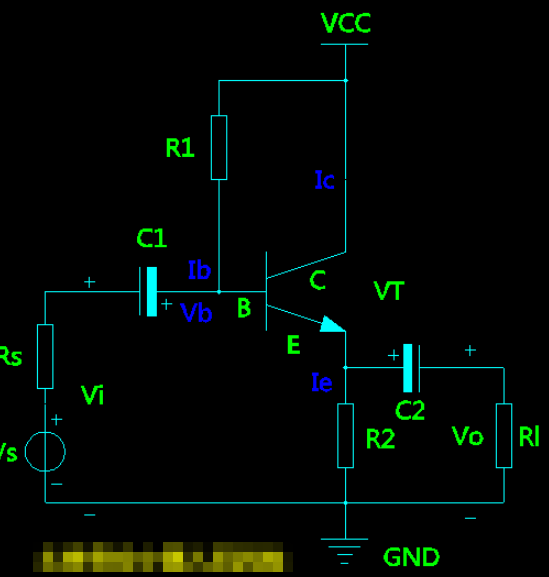

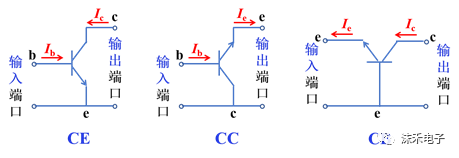

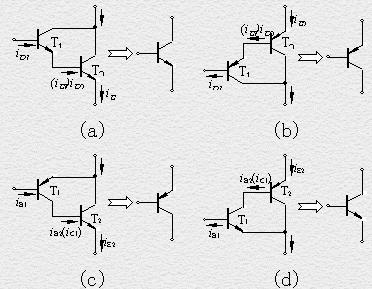

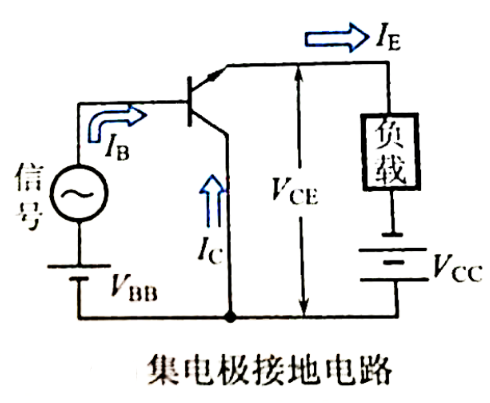

众所周知,BJT是一个晶体管,有三个端子(发射极、基极和集电极),这些端子主要可以配置三种开关模式:共基极、共集电极和共发射极。

这篇文章主要是关于集电极开路电路的相关知识。

一、集电极开路是什么意思?

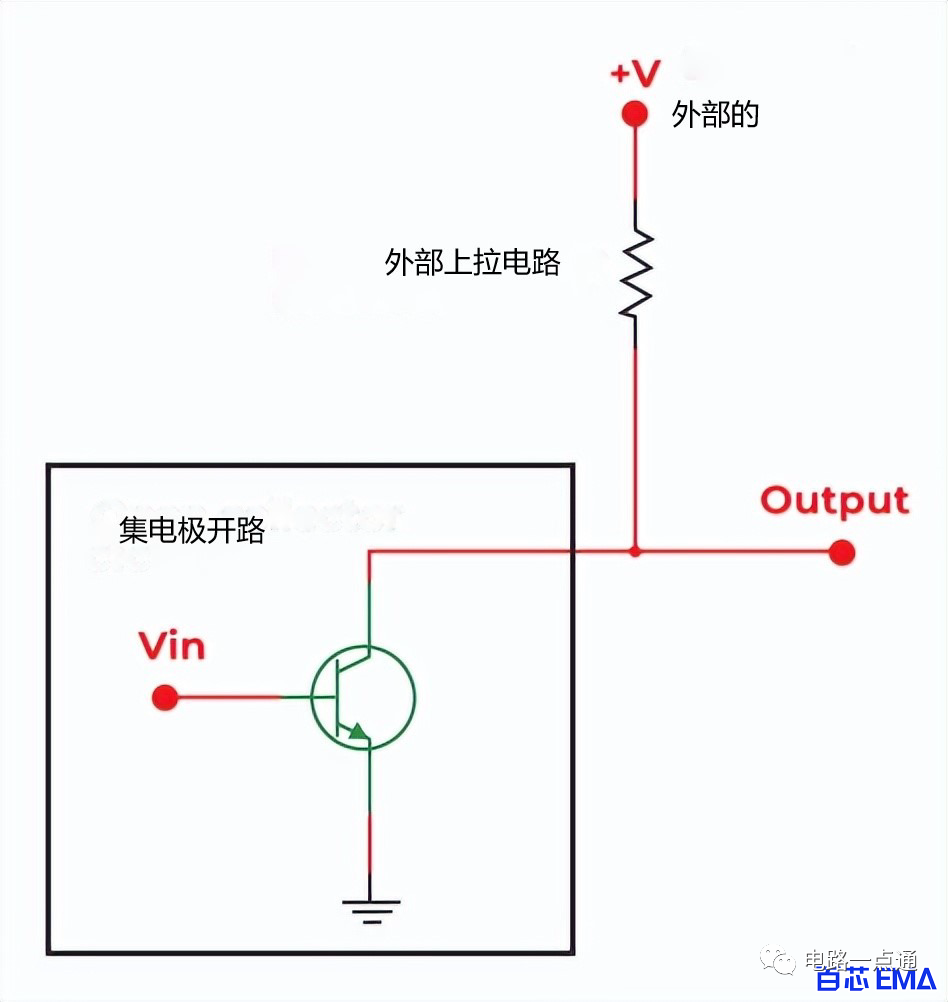

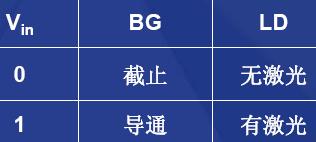

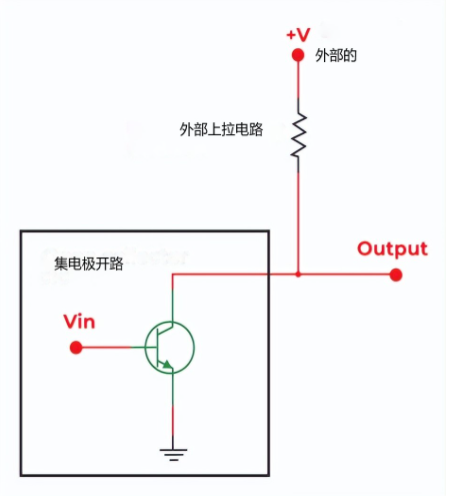

集电极开路是各种集成电路中常见的输出。集电极开路就像一个接地或断开的开关。除了将IC或任何其他晶体管的输出连接到特定设备外,还连接到NPN晶体管的集电极开路的基极端子,NPN晶体管的发射极端子与接地引脚内部连接。

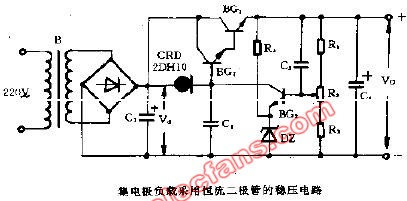

因此集电极开路的输出视为NPN晶体管,它允许电流吸收到公共端。对于这样集电极开路电路,必须有一个电源才能使输出正常工作。当我们要求未连接任何电源时计算输出电压时,电压不会发生变化。必须计算输出端的电压以了解集电极开路电路的正常运行。

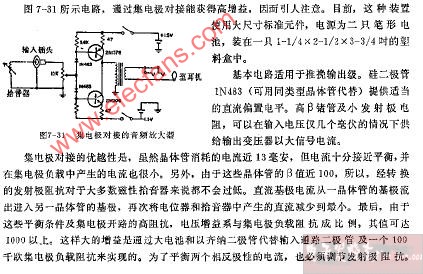

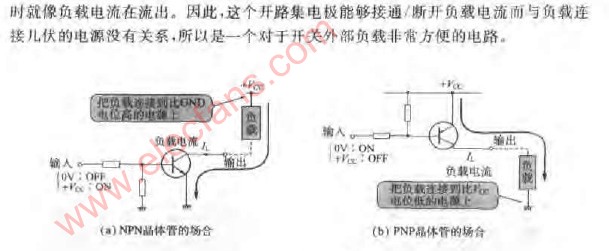

该电路可以根据晶体管的类型(NPN或者PNP)提供灌电流或拉电流输出。

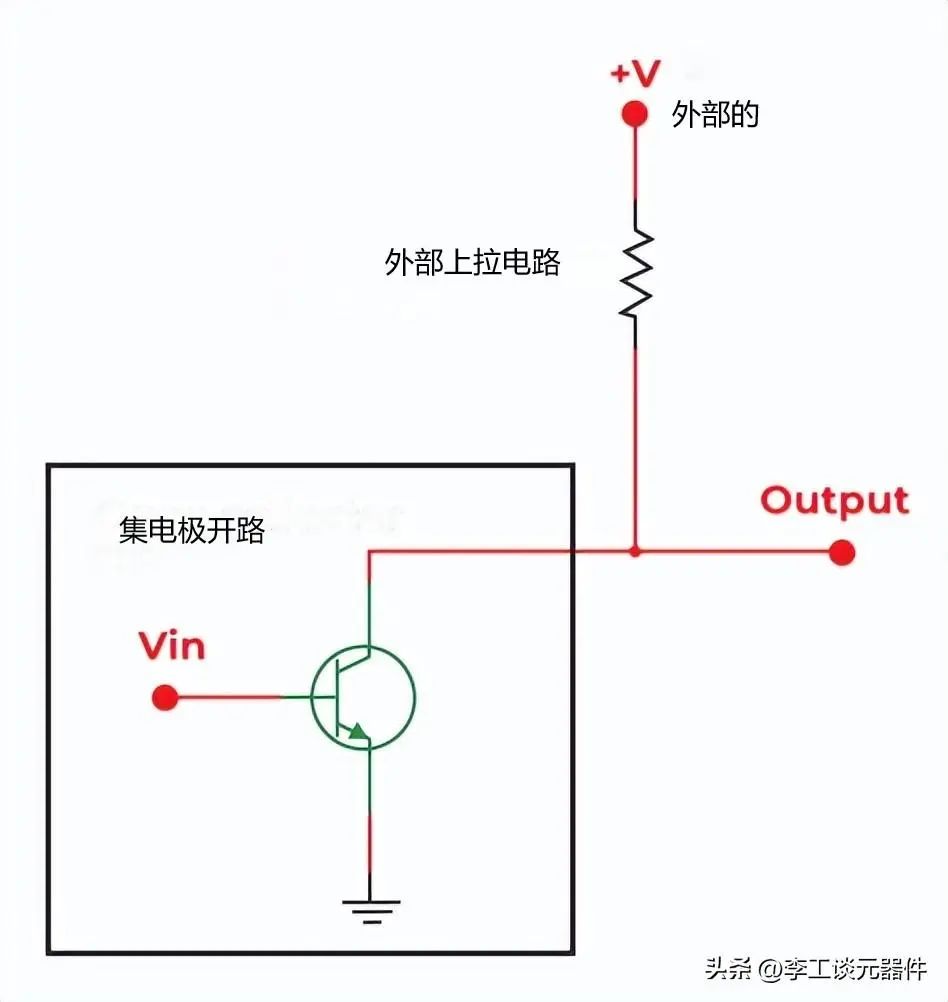

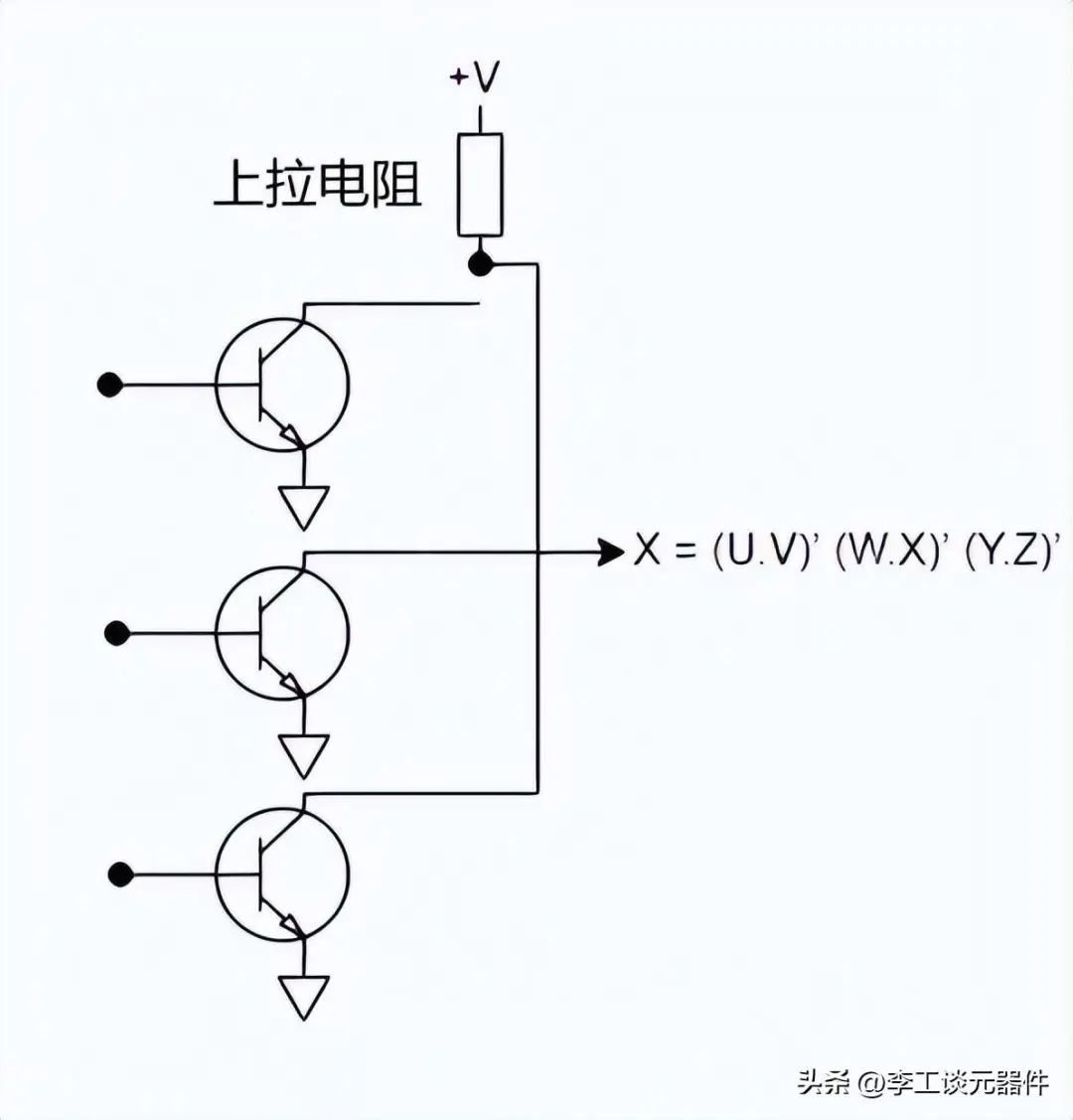

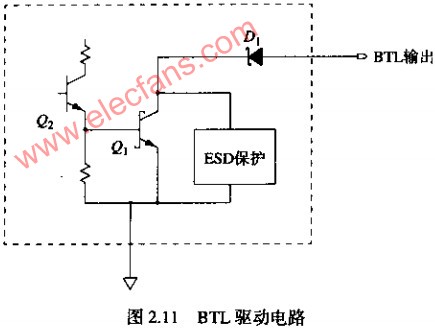

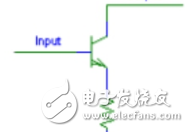

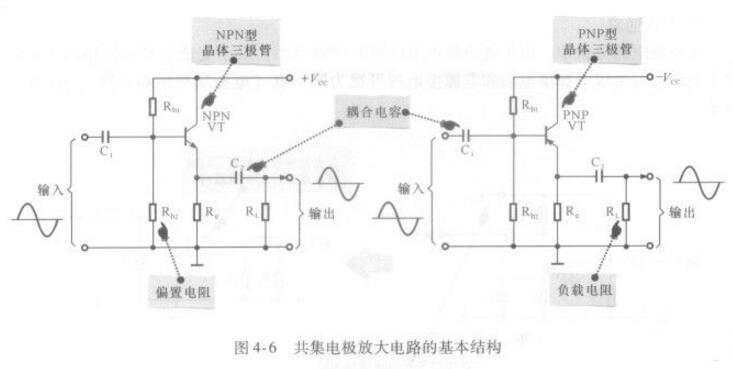

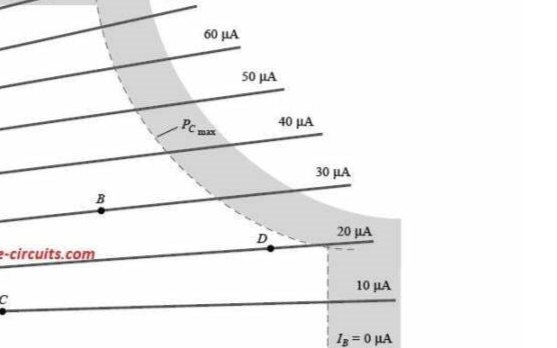

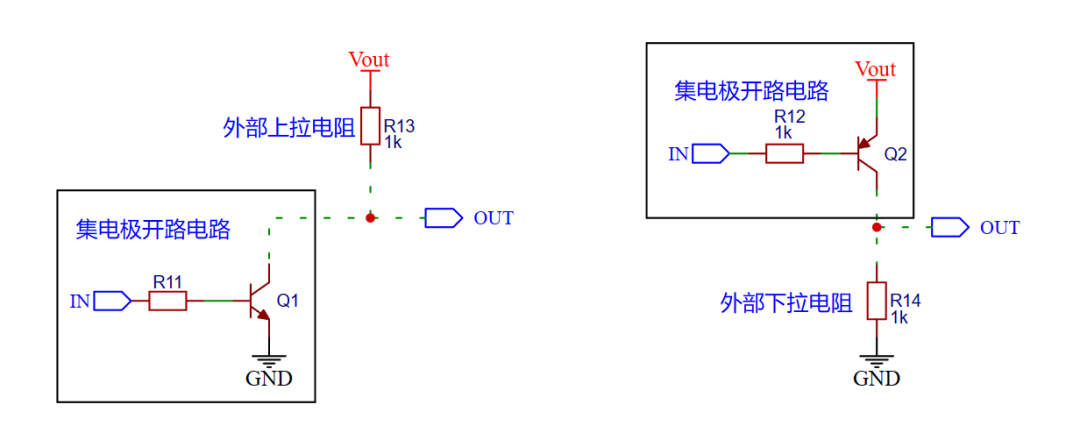

1、当 NPN 晶体管工作在“高”状态时,它向地提供灌电流;在“低”状态时,输出端将浮动,直到它通过上拉电阻连接到正电源电压。 2、当 PNP 晶体管工作在“高”状态时,它向地提供源电流;在“低”状态时,输出端将浮动,直到使用下拉电阻连接到地。 下图是集电极开路逻辑图。

集电极开路逻辑

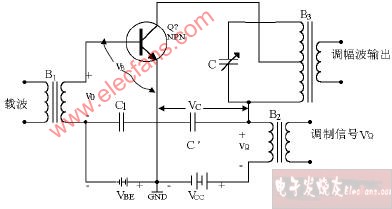

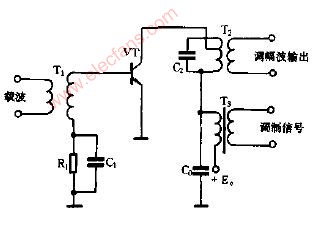

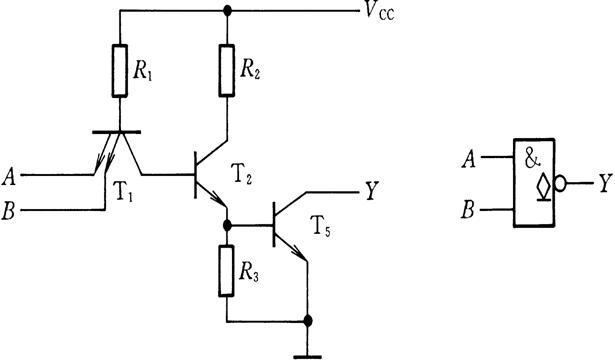

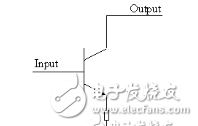

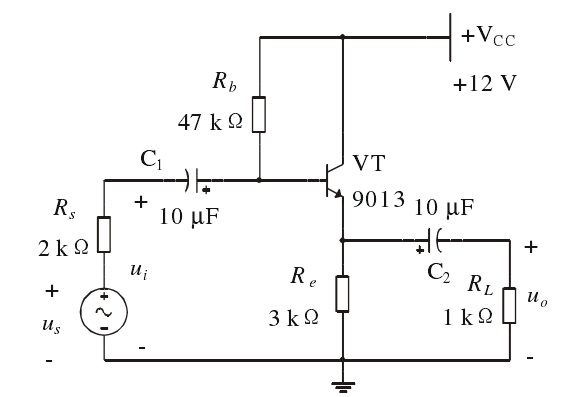

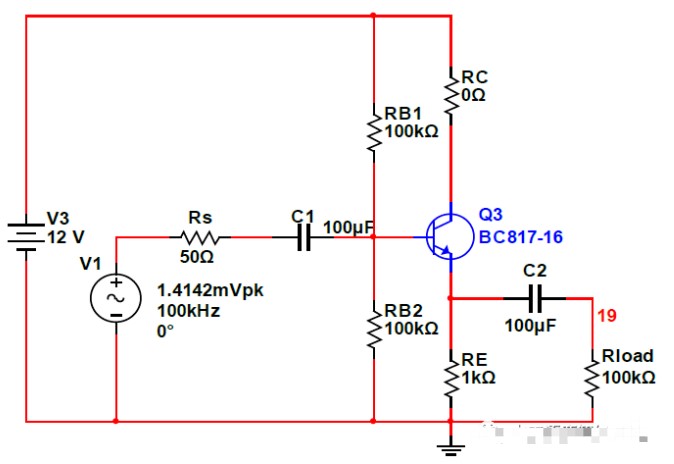

二、集电极开路晶体管电路

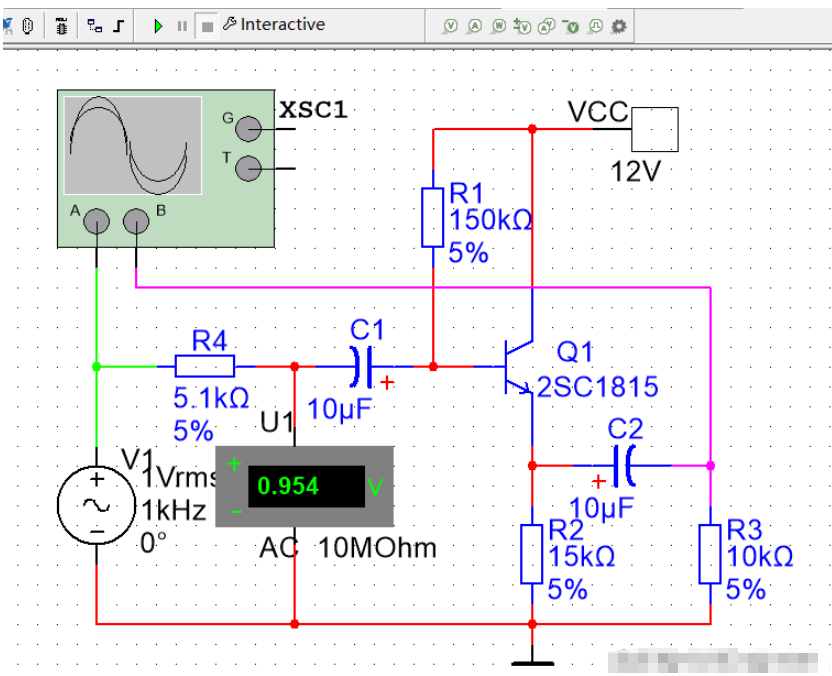

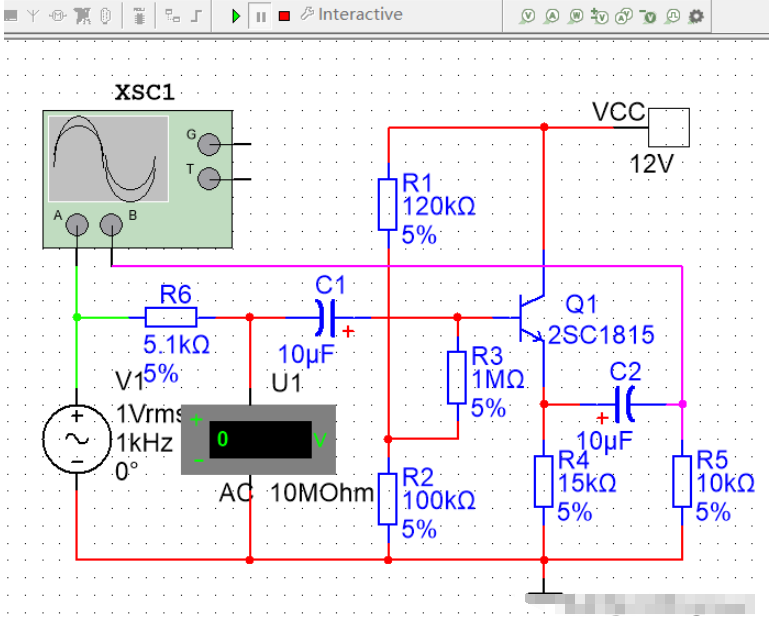

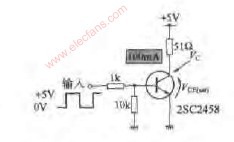

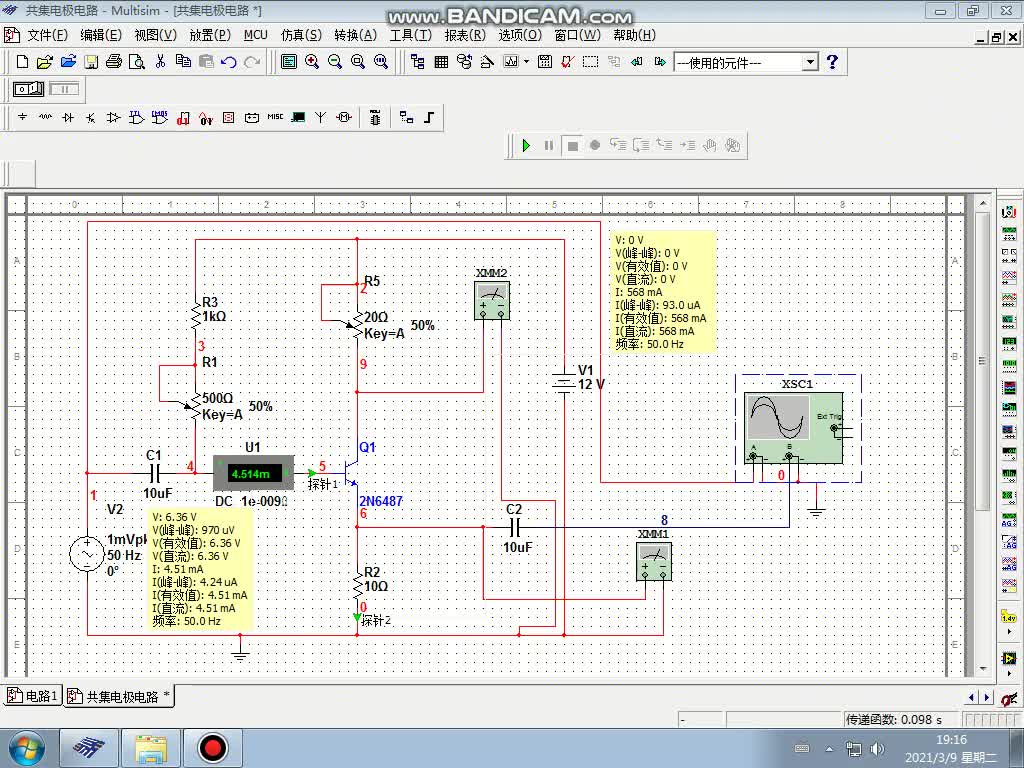

1、NPN 集电极开路输出 当 NPN 双极晶体管在集电极开路(OC 或 o/c)配置下运行时,它在完全开启或完全关闭之间运行,因此充当电子固态开关。 也就是说,在没有施加基极偏置电压的情况下,晶体管将完全关断,而当施加合适的基极偏置电压时,晶体管将完全导通。因此,当晶体管在其截止区 (OFF) 和饱和区 (ON) 之间运行时,它不会像在其有源区受控时那样作为放大器件运行。 晶体管在截止和饱和之间的切换允许集电极开路输出驱动外部连接负载的能力,这些负载需要比以前的共发射极配置所允许的更高的电压和/或电流。唯一的限制是实际开关晶体管的最大允许电压和/或电流值。 那么集电极开路输出的优点是,任何输出开关电压都可以通过像以前一样将集电极端子上拉到单个正电源,或者通过单独的电源轨为负载供电来简单地获得。例如,想要驱动需要从 +5 伏逻辑门或 Arduino、Raspberry-Pi 输出引脚的输出提供 +12 伏电源的低电流灯或继电器。 但其缺点是,当使用集电极开路输出来切换数字信号、门电路或电子电路的输入端时,由于三极管的集电极端没有输出驱动能力,一般需要外接上拉电阻。这是因为对于 NPN 晶体管,它只能在通电时将输出拉低至地 (0V),而在处于关断状态时无法返回或将其再次推回高电平。 当断电时,必须使用连接在其集电极端子和电源电压之间的外部“上拉电阻”将输出再次拉高,以阻止集电极开路端子在高电平 (+V) 和低电平之间浮动 ( 0V) 当晶体管关闭时。 此上拉电阻的值并不重要,在某种程度上取决于输出端所需的负载电流值,电阻值的范围通常为几百到几千欧姆。因此,对于 NPN 双极晶体管,其集电极开路输出仅为电流吸收输出。 下面为集电极开路晶体管电路。

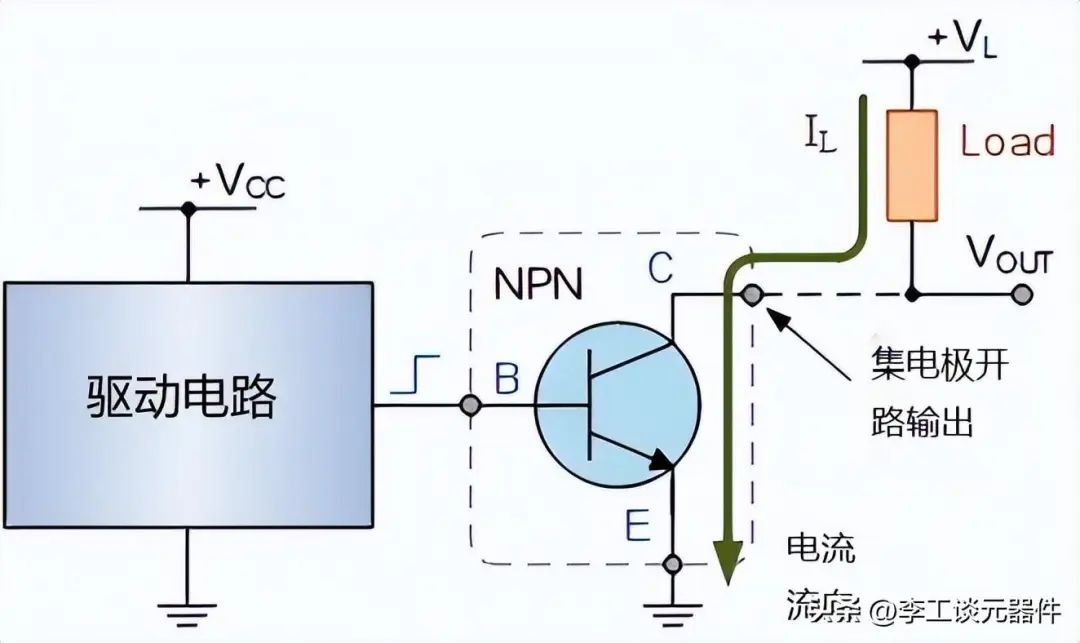

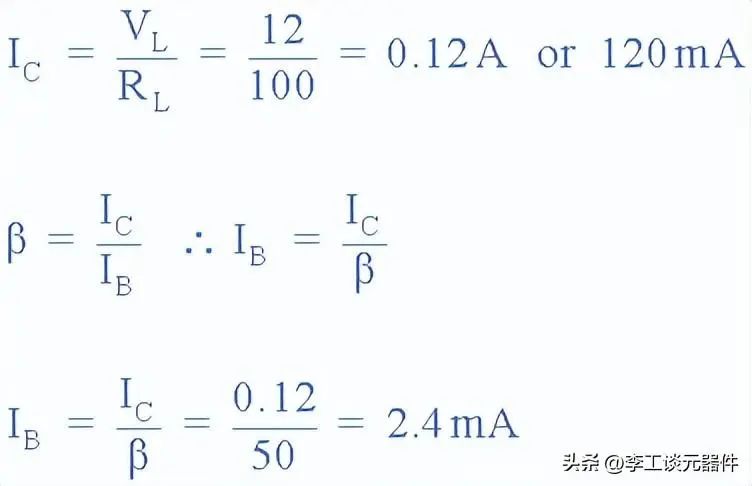

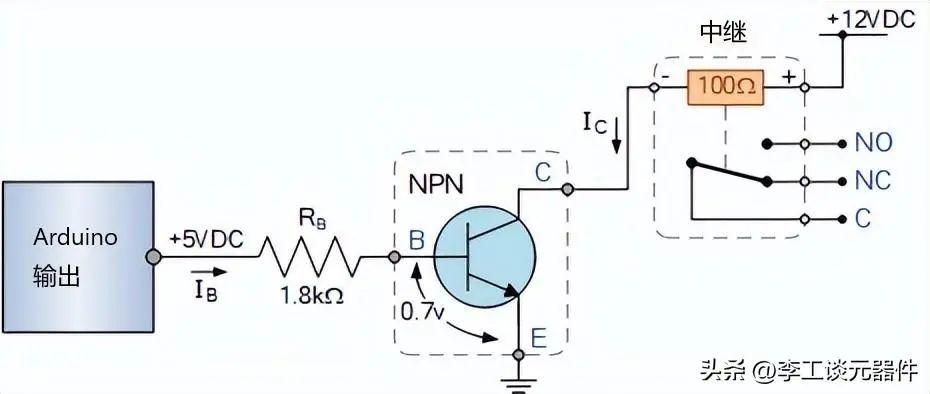

集电极开路开关电路 上图显示了集电极开路开关电路的典型布置,该电路可用于驱动机电型设备以及许多其他开关应用。NPN晶体管基极驱动电路可以是任何合适的interwetten与威廉的赔率体系 或数字电路。晶体管的集电极连接到要切换的负载,晶体管的发射极端子直接接地。 对于 NPN 型集电极开路输出,当控制信号施加到晶体管的基极时,它会导通,并且连接到集电极端子的输出通过现在导通的晶体管结点被下拉到地电位连接的负载并将其打开。因此,晶体管开关并传递负载电流 I L,其使用欧姆定律确定为: 负载电流,Iload= 负载电压 / 负载电阻 当晶体管正基极驱动被移除(关闭)时,NPN 晶体管停止导通,负载(可能是继电器线圈、螺线管、小型直流电机、灯等)断电并关闭。然后输出晶体管可用于控制外部连接的负载,因为 NPN 晶体管集电极开路的电流吸收开关动作可作为开路 (OFF) 或短路 (ON)。 这里的优点是集电极负载不需要连接到与晶体管驱动电路相同的电压电位,因为它可以使用较低或较高的电压电位,例如 12 伏或 30 伏直流电。 同样简单的数字或模拟电路也可用于通过简单地改变输出晶体管来切换许多不同的负载。例如,10mA 时为 6 VDC(2N3904 晶体管),或 3 安培时为 40 VDC(2N3506 晶体管),甚至使用集电极开路达林顿晶体管。 2、集电极开路输出示例 No1 在这个电路中需要来自 Arduino 板的 +5 伏数字输出引脚来驱动机电继电器。如果继电器线圈的额定电压为 12 VDC、100Ω,并且在其集电极开路配置中使用的 NPN 晶体管的直流电流增益 (Beta) 值为 50,则计算操作继电器线圈所需的基极电阻。 通过线圈的电流可以使用欧姆定律计算为:I = V/R

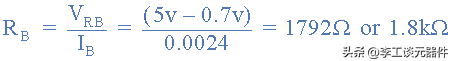

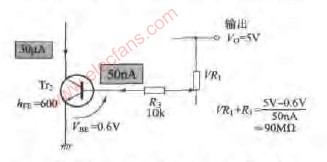

集电极开路计算公式 因此,对于直流电流增益为 50 的 NPN 晶体管,需要 2.4mA 的基极电流,忽略约 0.2 伏的集电极-发射极饱和电压 (V CE(sat) )。回想一下,晶体管的直流电流增益是指产生集电极电流需要多少基极电流。 当晶体管完全导通时,基极-发射极结 (V BE )两端的压降将为 0.7 伏。因此,所需的基极电阻 R B的值计算如下:

集电极开路计算公式 3、集电极开路工作原理 在集电极开路逻辑中,输出要么接地,要么保持开路(断开)。当输出接地时,输出端电压为0伏;当输出开路时,输出电压等于电源电压。

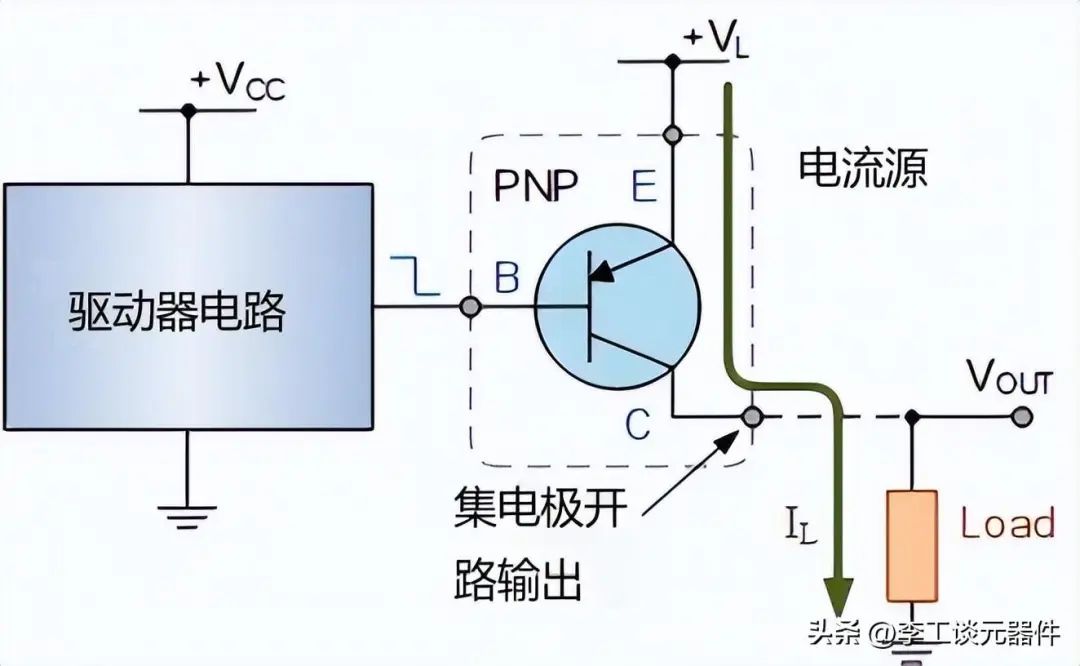

集电极开路工作原理 虽然 NPN 集电极开路晶体管电路产生“电流吸收”输出,即 NPN 晶体管集电极开路端子会将电流吸收到地 (0V),PNP 型晶体管也可用于集电极开路配置以产生所谓的“电流源”输出。 4、PNP 集电极开路输出 上面我们已经看到,集电极开路输出的主要特点是负载信号在完全导通时通过 NPN 双极晶体管的开关动作主动“下拉”到地电平,在关断时再次被动拉回产生电流吸收输出。 但是我们可以创建相反的开关条件,方法是使用 PNP 双极晶体管的集电极开路输出主动将其输出切换到电源轨,并使用外部连接的“下拉”电阻器在关断时再次将输出被动拉低。 对于 PNP 型集电极开路输出,晶体管只能将输出高电平切换到电源轨,因此其输出端必须通过外部连接的“下拉”电阻再次被动拉低,如下图所示。 下图为集电极开路 PNP 晶体管电路:

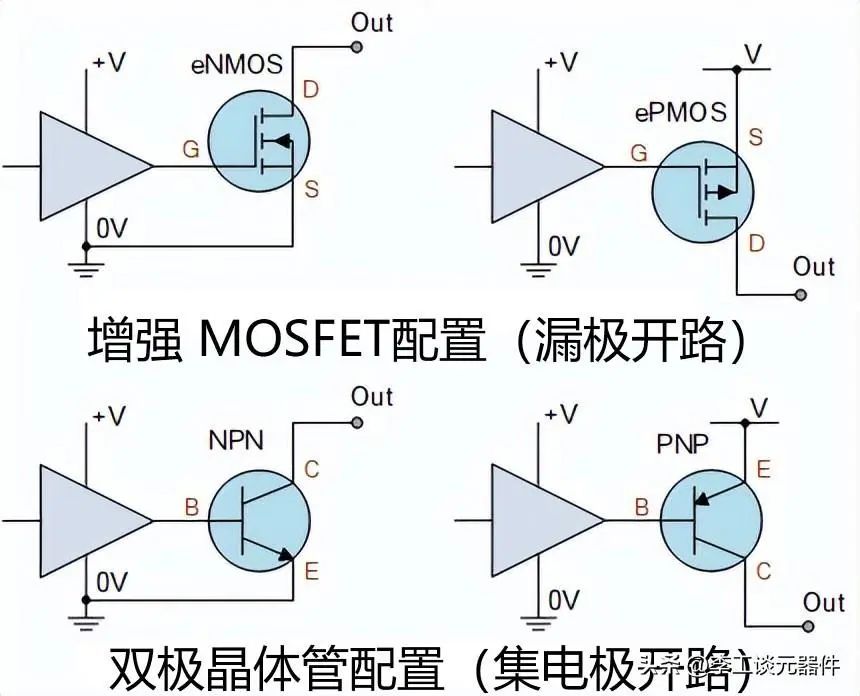

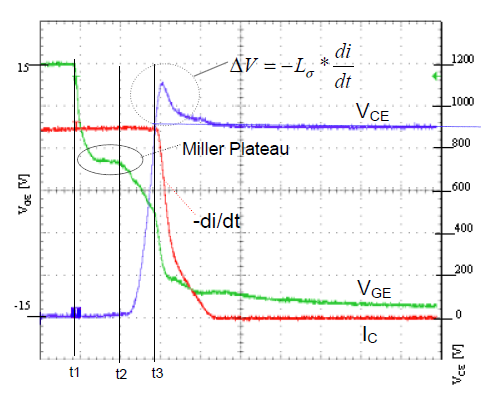

集电极开路 PNP 晶体管电路 然后我们可以看到,NPN 型或 PNP 型集电极开路输出配置只能在 ON 时主动将其输出拉低至地,或拉高至电源轨(取决于晶体管类型),但其集电极端必须拉高如果连接的负载无法做到这一点,则通过使用连接到其输出端子的上拉或下拉电阻被动地向上或向下。所用输出晶体管的类型及其开关动作会产生电流吸收或电流源条件。 除了在集电极开路配置中使用双极晶体管外,还可以在其开源配置中使用 n 沟道和 p 沟道增强型 MOSFET 或 IGBT。 与双极结型晶体管 (BJT) 需要基极电流来驱动晶体管进入饱和状态不同,常开(增强型)MOSFET 需要在其栅极 (G) 端子上施加合适的电压。MOSFET 的源极 (S) 端子直接连接到地或电源轨,而开漏 (D) 端子连接到外部负载。 将 MOSFET(或 IGBT)用作漏极开路(OD)器件时,在驱动功率负载或连接到更高电压电源的负载时,遵循与集电极开路输出(OC)相同的要求,因为使用上拉或下拉电阻适用。唯一的区别是 MOSFET 通道热功率额定值和静态电压保护。 5、开漏增强 MOSFET 配置

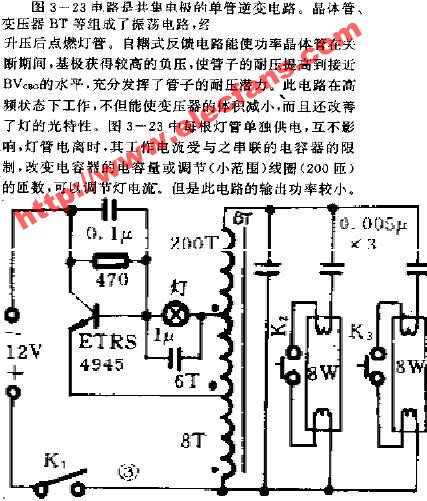

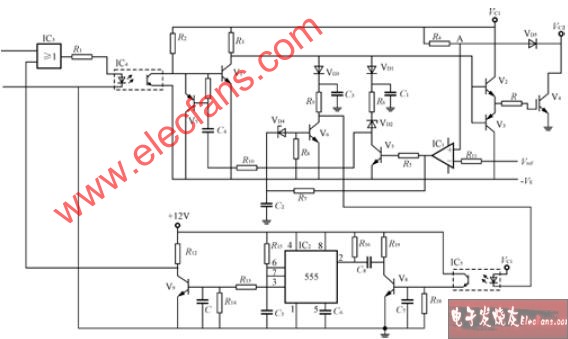

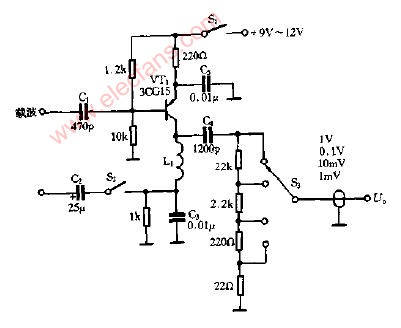

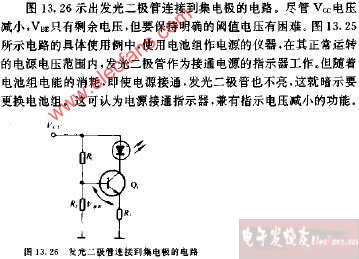

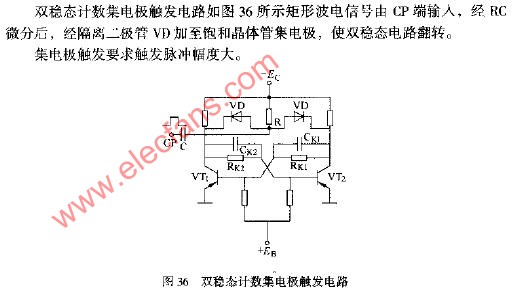

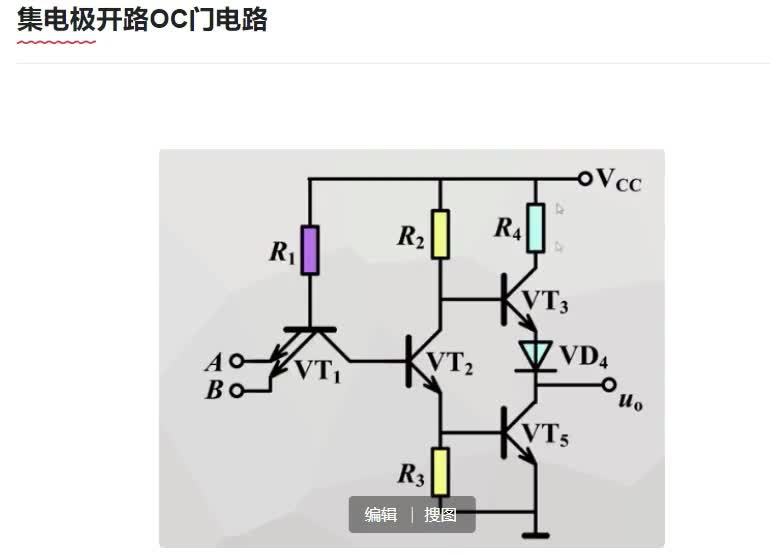

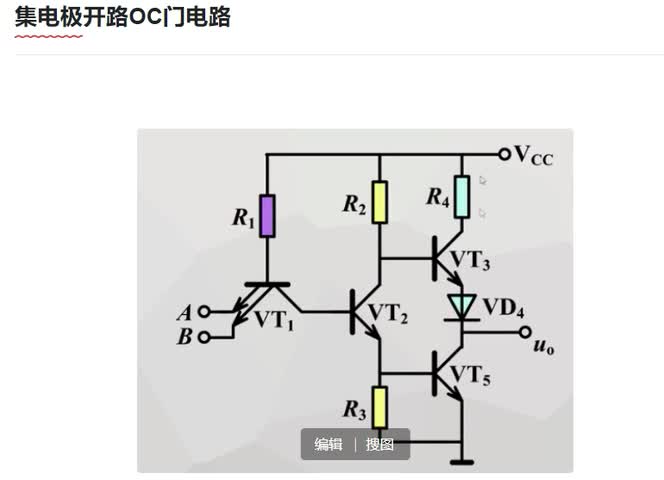

三、集电极开路电路--TTL 门

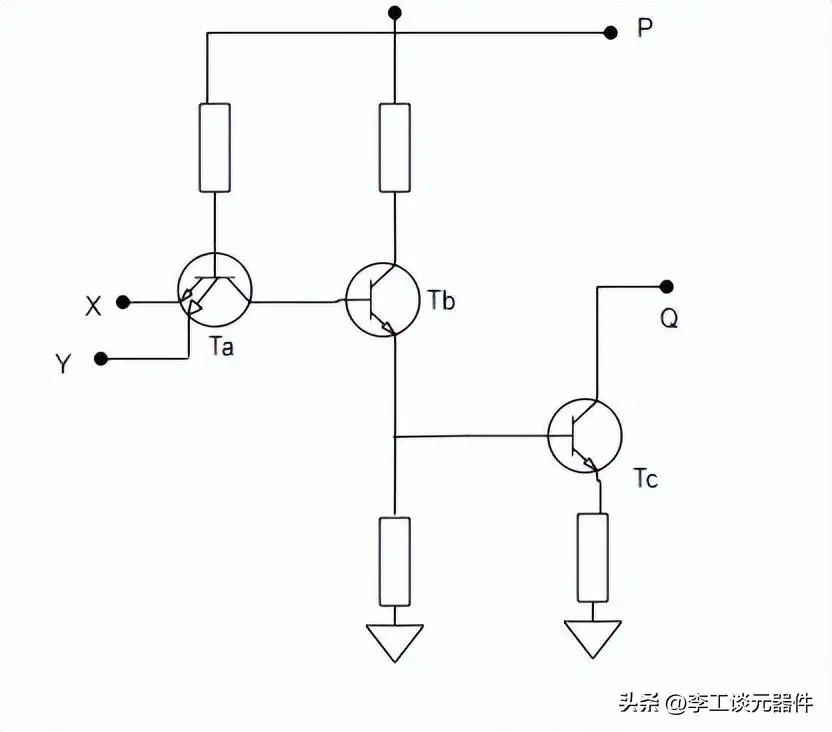

当晶体管 Tc 从图腾柱配置中移除时,就会形成集电极开路 TTL 栅极。通过在下图中的输出端子P和Q之间使用上拉电阻,可以将TTL与非门转换为与门。

集电极开路电路--TTL 门 集电极开路与非门 使用集电极开路逻辑门,可以开发有线 AND 和有线OR 门。在下图中,多个与门在集电极开路 TTL 门的帮助下进行与运算,结果显示为接线与。这是因为 AND 是通过对所有输出进行与运算而产生的,可以表示如下: X = (UV)' (WX)' (YZ)' 当所有 NAND 门的集电极端子都为输出晶体管短路时,这将执行 ANDing 操作。通过这种有线或连接也可以通过德摩根原理得到,方程为 X = (UV + WX + YZ)' 在下图中,上拉电阻值是通过每个输出晶体管允许流过集电极端子的最大电流值已知的。

使用 TTL 与非门的有线与或

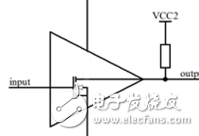

四、集电极开路输出接线图

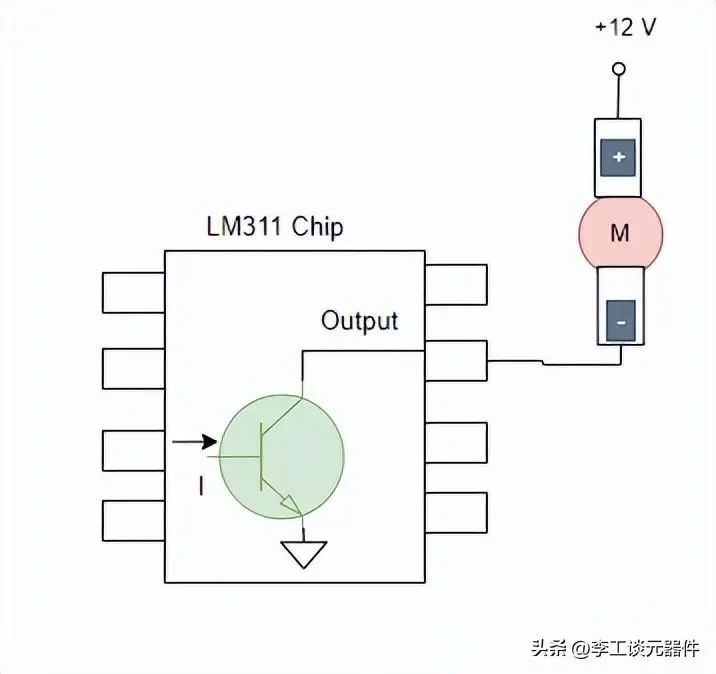

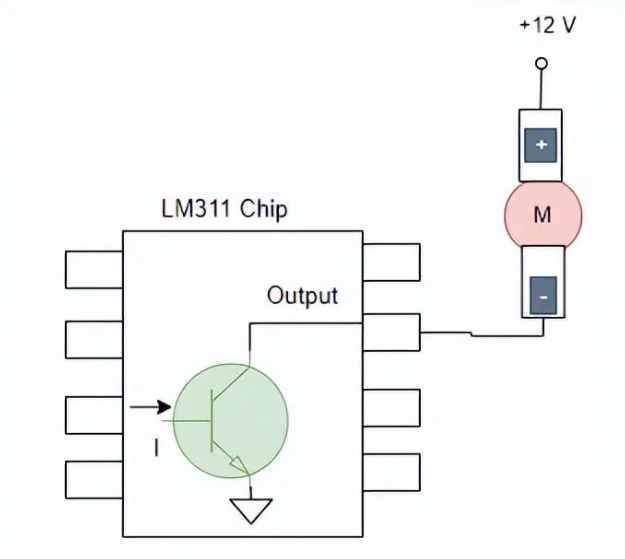

集电极开路电路通常用于电压比较器。很少有电压比较器芯片是LM339、LM393和LM311,它们都作为集电极开路器件工作。 当在输出端连接任何设备时,输出设备应连接到能够驱动负载的正电压源。 例如:当输出设备为 12V 直流电机时,则输出应接+12V。然后,负载的负极和接地端子连接到驱动电机的设备的输出。 当LM311芯片需要接一个12V直流电机时,配置如下:

集电极开路输出的LM311芯片

五、集电极开路的作用

集电极开路逻辑是一种输出信号为漏极开路的逻辑。这意味着输出可以吸收电流,但不能提供电流。集电极开路逻辑通常用于多个设备需要共享一条公共信号线的情况。

改进的系统性能

较低的电容

更大的负载可以连接到收集器而没有交叉击穿的危险

集电极开路输出对电磁干扰相对不敏感

多个集电极开路输出可以连接在一起以创建逻辑或功能。例如,如果需要一个具有两个输入的 OR 函数,可以将这些输出中的一个连接到 A,将另一个连接到 B。如果试图找出哪个是的系统的更好选择,这将很有用,例如, 是否使用 A 型或 B 型电机。 开漏输出在未驱动时具有高阻抗,因此非常适合用作状态指示器。集电极开路逻辑的缺点之一是需要高电压才能关闭电路。 集电极开路输出不能提供电流,因此不可能从单个集电极开路输出驱动多个负载。设备的最大电压输出受驱动设备的VOH(高电压)限制。例如,如果集电极开路由 5V 设备驱动,则可以施加到负载的最大电压将为 5V。

六、集电极开路优缺点

1、优点 集电极开路逻辑的主要优点是它很容易与其他数字设备连接。集电极开路设计也不会像其他数字设计那样受到串扰或噪声的影响。然而,集电极开路逻辑的缺点是它不如其他数字逻辑设计快。集电极开路是某些集成电路 (IC) 上的一种输出类型,它无法吸收与标准输出一样多的电流。当用作输入时,集电极开路给出与开关相同的结果:它可以是 ON 或 OFF。使用集电极开路输出的优点是它可以连接到其他集电极开路作品以创建线或连接。 集电极开路逻辑的主要优点是:

可用于在多个输出之间创建线或连接。

集电极开路输出可以吸收比标准输出更多的电流,使其成为驱动 LED 和其他低电流设备的理想选择。

集电极开路逻辑通常用于需要考虑电气干扰 (EMI) 的应用中,因为输出和地之间没有内部连接可减少产生的 EMI 量。

2、缺点: 使用集电极开路逻辑时,主要缺点之一是可能存在竞争。当两个或多个设备试图同时将输出拉低时,就会发生这种情况。为了避免这种情况,必须使用适当的设计和布局威廉希尔官方网站 。另一个缺点是集电极开路输出只能吸收电流,不能提供电流。这意味着如果需要驱动高电平信号,就必须使用外部上拉电阻。

编辑:黄飞

电子发烧友App

电子发烧友App

评论