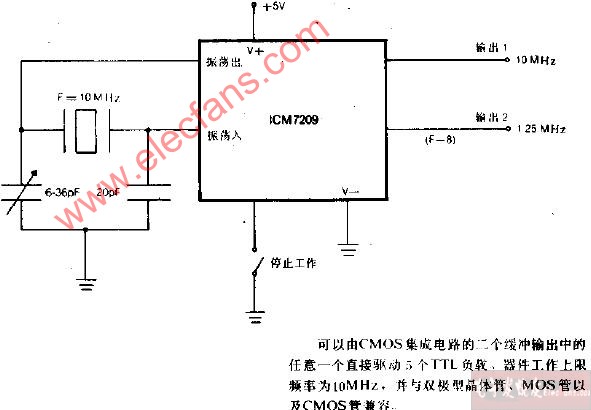

精密时钟发生器电路图

电子发烧友App

电子发烧友App

硬声App

硬声App

完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网>电子威廉希尔官方网站 应用>电子威廉希尔官方网站 >电路图>光电振荡电路>精密时钟发生器电路图

相关推荐

99

99 478

478

706

706

1598

1598

679

679 2489

2489

3736

3736 671

671

6830

6830 1267

1267

748

748 722

722 1282

1282

126

126 1424

1424

616

616

392

392

913

913

1654

1654 865

865

评论