一种低功耗系统芯片的实现流程(2)

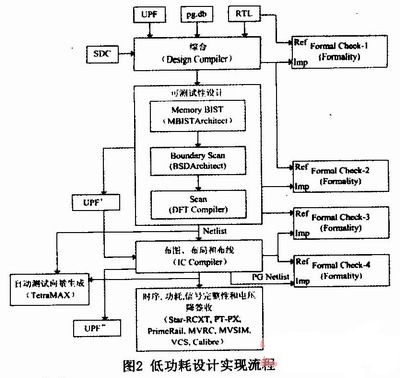

如图1所示,每个关断电压域的输出要插入隔离器件,以防止该电压域电源关断后输出的不定态影响别的电压域正常工作,由于PD6的工作电压是1.2V,其余的是1.8V,因此要在PD6的输入和输出插入电平转换器件。这些低功耗的设计意图写入UPF文件,EDA工具根据UPF实现设计者的想法。整个设计实现过程中包括RTL代码的综合、可测试性设计、布局布线、物理验证和网表的等价形式验证,如图2所示。

3.1 综合

RTL代码的综合使用Design Compiler(DC),输入文件为UPF、带电源信息的库文件(pg.db)、RTL代码和时序约束文件(SDC。在综合优化的过程中,工具会根据 UPF自动地在相应的位置插入电平转换器件和隔离器件,优化完成后,可以用check_mv_desing命令进行正确性检查。 DC输出的网表与RTL代码使用Formality进行等价形式验证。

3.2 可测试性设计

在通过等价形式验证的综合网表中做可测性设计。首先利用MBISTArchitect做静态随机存储器(SRAM)的内在自测试(MBIST)。输入文件包括网表、SRAM的模型,输出带自测试电路的网表。其次利用BSDArchitect完成边界扫描测试,输入文件包括网表和输入/输出接口电路的模型,输出包含边界扫描电路的网表。最后利用DFTCompiler完成逻辑扫描测试,输入文件为UPF、时序约束文件和网表,利用insert dft命令完成扫描链的连接。由于做内在自测试和边界扫描测试电路时没有用到UPF,因此在扫描链插入后要用check mv desing命令进行检查,电平转换器件和隔离器件如果缺少用insert_mv_cell插入,如果多余用remove_mv_cell命令删除。DFT Compiler输出为网表、新的UPF'、SPF、DEF和时序约束文件。做完可测试性设计的网表和综合的网表进行等价形式验证。

3.3 布局布线

利用IC Compiler进行布局布线,输入文件有UPF'、时序约束文件、网表,输出文件为网表和时序约束文件。输出网表要完成等价形式验证。完成布局布线后的网表使用MVRIC进行低功耗设计的检查,用Star-RCXT抽取寄生参数,用PrimeTime进行时序和功耗的签收,最后用MVSIM和VCS完成后仿真。最后使用Calibre完成物理验证,输出GDSII文件。最终的芯片版图如图3所示。

3.4 自动测试向量的生成

完成布局布线后的网表和DFT Compiler输出的SPF文件送入TetraMAX中进行自动测试向量的生成。本文的设计生成2576个向量,故障覆盖率为98%,并用VCS完成了测试向量的后仿真。

4 结论

本文阐述了一种低功耗系统芯片的实现流程。利用该流程实现了一个包含4万寄存器、20万等效逻辑门的系统芯片,并流片验证,结果达到预期目标。

- 第 1 页:一种低功耗系统芯片的实现流程(1)

- 第 2 页:低功耗设计流程#

本文导航

非常好我支持^.^

(0) 0%

不好我反对

(0) 0%

相关阅读:

- [新品快讯] MAX9644,MAX9645,MAX9646精密基准的低功耗比较器 2011-04-01

- [新品快讯] Linear推出超低功耗12位/14位模数转换器LTC2145 2011-03-31

- [新品快讯] 德州仪器推出低功耗16位数字模拟转换器(DAC) DA 2011-03-29

- [电子威廉希尔官方网站 ] DOCEA低功耗芯片和系统设计方案 2011-03-28

- [新品快讯] SiTime推出SiT8004业内最低功耗高频振荡器 2011-03-23

- [通信设计应用] 展讯40nm低功耗3G手机解决方案 2011-03-22

- [AD威廉希尔官方网站 ] MAX11612-MAX11617低功耗12位多通道模数转换器(ADC) 2011-03-16

- [新品快讯] SpringSoft发布最新版一贯式定制IC版图流程设计平 2011-03-16

( 发表人:发烧友 )