基于Spantan FPGA的多路数字量采集模块设计(2)

FPGA内部逻辑主要分为数字信号采集、数据缓存和数据读取、FIFO控制。根据要求,信号采集又分为频率信号采集、20路数字信号采集和15路脉冲信号采集。系统同时采集三组信号,再送入外部FIFO中缓存。由于脉冲信号的数据量较大,时序不匹配,因此在信号采集完后数据还应缓存,然后再经数据编帧送至外部FIFO。内部缓存利用VHDL编写模块,但是更简易的方法是利用FPGA内部的双口RAM。因此,FPGA选用Xilinx公司的XCF2S-100E,其内部集成5 KB容量的RAM,足够内部缓存使用。数据经信号采集后送人缓存,然后由读取模块读出再送入外部FIFO,整个模块采用120 MHz的时钟,可以满足要求大于100 MHz的时钟频率。采集20路数字信号的方法是当信号变化时,就将当前所有数字信号的电平状态都送入缓存,而对于频率信号和脉冲信号的采集则采用如下方法。

4.1 频率信号采集

由于频率信号只需体现出其频率大小即可,因此采集频率信号时只记录该信号两沿间的时间。即就是设定一个16位的计数器T,计数器的值随主时钟累加,当判断到该信号有变化时,就将计数器的值T1送人缓存,然后将该计数器清零。计数器的值继续累加,直到该信号下一次变化,再将计数器的值T2送入缓存,计数器再清零,以此类推,来记录该信号两沿间的时间。

4.2 脉冲信号采集

采集脉冲信号需记录该信号的脉宽以及相对于同步信号的延迟。记录方法是:使用一个单独的进程,定义一个24位的计数器TB,当同步信号的上升沿到来时开始计数,当同步信号的下一个上升沿到来时,该计数器清零。另一个进程判断15路脉冲信号中有一路信号变化时,将当前计数器TB的值送人缓存,并将当前所有脉冲信号的电平状态都送入缓存。

4.3 数据的编帧和解帧

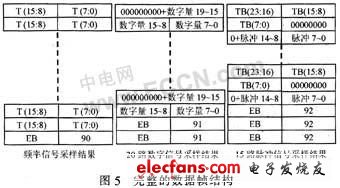

在数据采集部分中,当同步信号的上升沿到来时,将3个帧标志分别写入3个缓存,频率信号数据的帧标志为EB90;20路数字信号的帧标志为2个EB91;15路脉冲信号数据的帧标志为3个EB92。读取数据模块中,当同步信号的下降沿到来时,开始读取缓存的数据送至外部FIFO,并判断当读取一个EB90后,开始读取缓存的数据,并送入外部FIFO;当读到两个EB91后,读取缓存的数据,并送入外部FIFO;当读到3个EB92后表明一帧数据读取完毕,等待下一个同步信号的下降沿后再开始读取下一帧数据。由于外部FIFO是16位,所以数据中不满16位的都用0将数据补充完整,完整的数据帧结构如图5所示。

上位机收到一帧数据后进行解帧处理,对于频率信号数据,将这些T值相加并求平均得出T’,再乘以2,由于系统时钟是120 MHz,所以2T’/120为频率信号周期(μs级),然后求倒数即可得出该信号的频率值。

20路数字量信号数据直接显示其电平状态。脉冲信号数据则先判断哪一路(多路)脉冲信号发生变化,再判断该信号(几路信号)的电平状态。若为高电平,则对应的时间应为TBa;若为低电平,则对应的时间应为TBb。TBa即为该脉冲信号相对于同步信号的延迟,而TBb-TBa的值即为该脉冲信号的正脉冲脉宽。

5 结束语

针对测控系统监测信号数量较多的问题,提出了一种基于FPGA的多路数字量采集与处理模块,设计了相应的电路和FPGA逻辑。在综合调试成功的基础上,该多路数字量采集模块已成功应用于某测试系统。

- 第 1 页:基于Spantan FPGA的多路数字量采集模块设计(1)

- 第 2 页:FPGA内部逻辑设计#

本文导航

非常好我支持^.^

(0) 0%

不好我反对

(0) 0%

相关阅读:

- [电子常识] ASIC和FPGA的优势与劣势 2011-03-31

- [电子常识] fpga 2011-03-31

- [FPGA/ASIC威廉希尔官方网站 ] 立体摄像深度感知的FPGA实现 2011-03-31

- [FPGA/ASIC威廉希尔官方网站 ] 免费的I/O改进FPGA时钟分配控制 2011-03-30

- [RF/无线] 航管二次雷达射频切换单元FPGA实现 2011-03-30

- [FPGA/ASIC威廉希尔官方网站 ] 基于FPGA和AD1836的I2S接口设计 2011-03-29

- [新品快讯] LatticeXP2低成本非易失FPGA 2011-03-28

- [新品快讯] 莱迪思半导体推出第三代LatticeECP3系列FPGA 2011-03-23

( 发表人:简单幸福 )