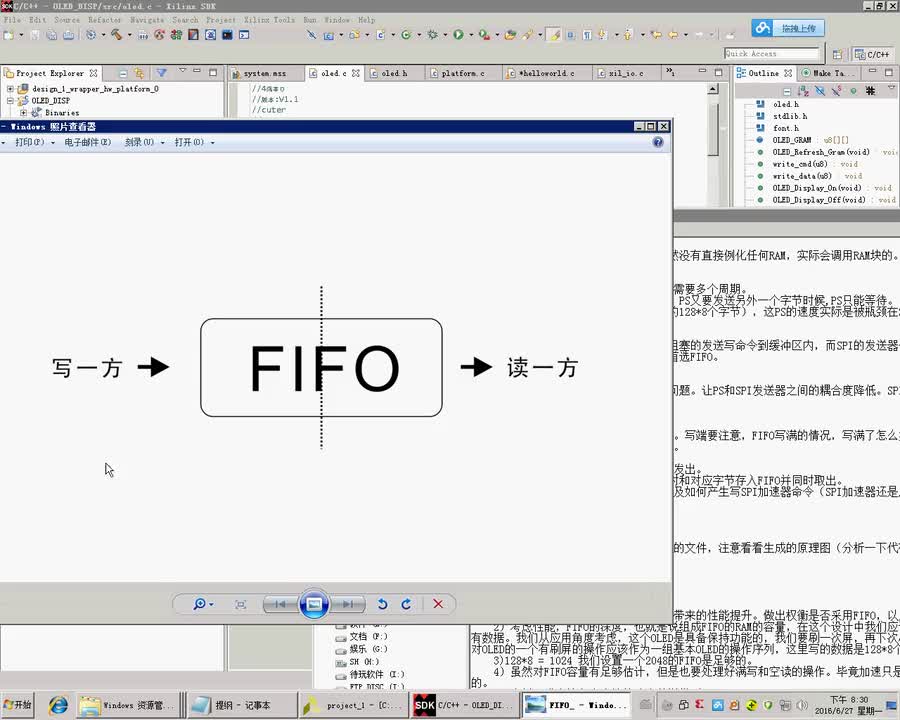

大家好,又到了每日学习的时间了,今天我们来聊一聊基于FPGA的异步FIFO的实现。 一、FIFO简介 FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,它与普通

2018-06-21 11:15:25 6164

6164

,它是7系列FPGA新设计的IO专用FIFO,主要用于IOLOGIC(例如ISERDES、IDDR、OSERDES或ODDR)逻辑功能的扩展。 FPGA的每个BANK有4个IN_FIFO

2020-11-29 10:08:00 2340

2340

对于fifo来说,H的设置至关重要。既要保证功能性,不溢出丢数,也要保证性能流水。深度设置过小会影响功能,过大又浪费资源。因此,总结下fifo设计中深度H的计算。

2022-08-29 11:19:03 1071

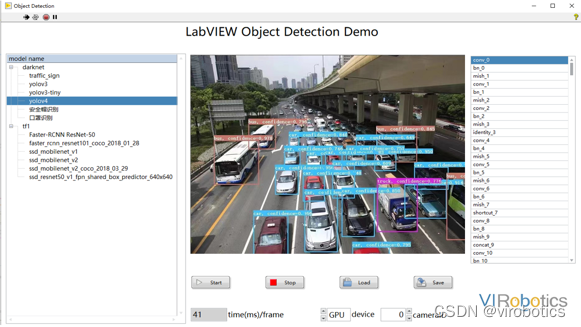

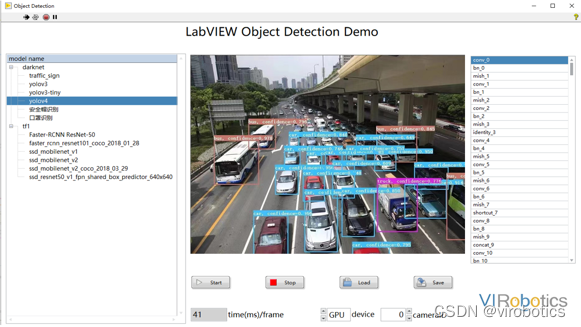

1071 LabVIEW可以实现深度学习嘛,今天我们一起来看看使用LabVIEW 实现物体识别、图像分割、文字识别、人脸识别等深度视觉

2023-08-11 16:02:21 758

758

最近加的群里面有些萌新在进行讨论**FIFO的深度**的时候,觉得 **FIFO的深度计算比较难以理解** 。所

2023-11-28 16:19:46 347

347

FIFO先进深度?我也想知道我的输入是否改变为3个数据单元(每个16位)的突发,应该是什么深度?谢谢,阿伦以上来自于谷歌翻译以下为原文Hi All, I have a design issue, I

2019-01-10 10:45:27

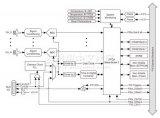

的读写时序。 2 模块划分本实例工程模块层次如图所示。●Pll_controller.v模块产生FPGA内部所需时钟信号。●fifo_test.v模块例化FPGA片内FIFO,并产生FPGA片内

2019-04-08 09:34:42

大虾们,小虾米求助!FPGA的最大深度可以达到多少,如果我存储的数据由14000*29bit,又需高速处理的话,我是否应该考虑使用SDRAM?顺便记录下:当读速率F2慢于写速率F1时,FIFO便可

2013-05-28 14:17:37

,这样我们可以实现读写不同速度。

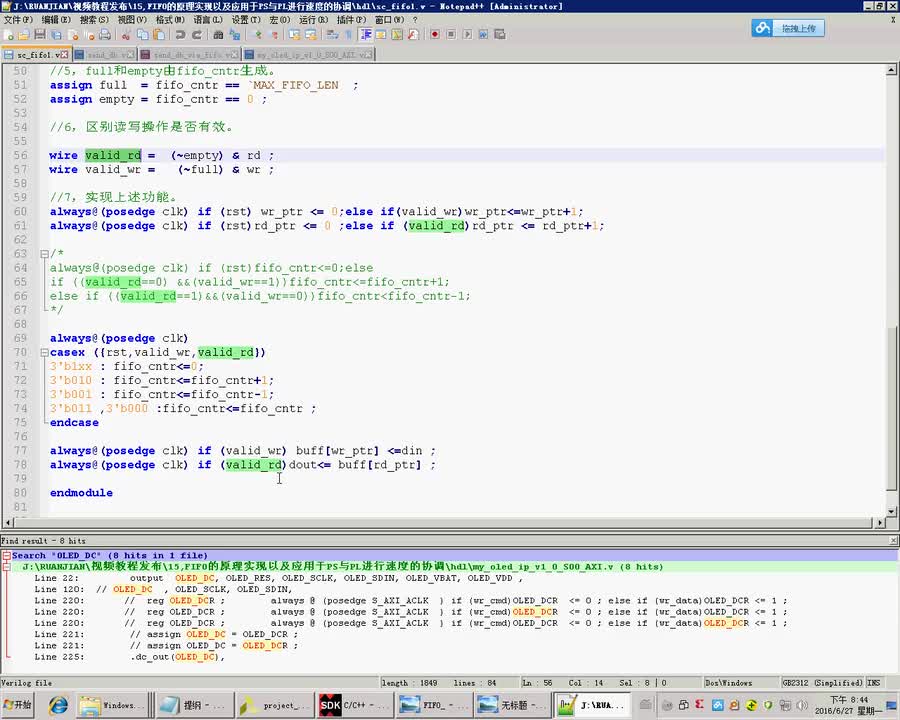

那么接下来,我们就来实现一下异步FIFO的读写过程。

上图为选择异步FIFO之后的图示,在这个图示中,我们给大家解释一下每个信号的含义

2023-06-16 17:50:31

CORE 之 FIFO设计 本篇实现基于叁芯智能科技的SANXIN -B01 FPGA开发板,以下为配套的教程,如有入手开发板,可以登录官方淘宝店购买,还有配套的学习视频。 SANXIN-B01

2023-03-15 16:19:35

问一下哪位使用过labview 2010 FPGA 编程,除了需要安装 labview fpga 模块外,还要安装什么才可以使用呢?只安装labview的模块没有硬件实物,能否实现labview fpga编的程序下载到赛灵思公司的fpga开发软件里面进行仿真呢?万分感谢

2012-08-24 10:23:36

如何使用labview实现深度学习应用。ok样本ng样本这些图片的特征是:ok与ok,ng与ng之间都有差异,传统的方法要实现,就需要复杂的算法编程实现,如果用深度学习,则非常简单。1.准备好样本库

2020-07-23 20:33:10

SPI手册中写的是SPI发送接收的FIFO 为16*16.但是如何设定用FIFO0还是FIFO15呢?现在只能传16bie的呀。求解

2018-11-13 15:00:02

CC430的RF模块的FIFO有几个字节的深度?

2018-06-07 04:37:39

不多说,上货。IP CORE 之 FIFO 设计- ISE 操作工具本篇实现基于叁芯智能科技的SANXIN -B02 FPGA开发板,如有入手开发板,可以登录官方淘宝店购买,还有配套的学习视频。FIFO

2023-04-11 20:50:21

实例内部系统功能框图如图所示。我们通过IP核例化一个FIFO,定时写入数据,然后再读出所有数据。通过ISE集成的在线逻辑分析仪chipscope,我们可以观察FPGA片内FIFO的读写时序。 2 模块

2016-02-26 10:26:05

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm1新建源文件打开

2016-02-29 13:35:55

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm1新建源文件打开

2016-02-29 13:35:55

逻辑分析仪chipscope,我们可以观察FPGA片内异步FIFO的读写时序。 2 模块划分本实例工程模块层次如图所示。●Pll_controller.v模块产生FPGA内部所需时钟信号

2016-03-07 11:32:16

`Xilinx FPGA入门连载56:FPGA片内异步FIFO实例之FIFO配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1新建

2016-03-09 10:49:56

的在线逻辑分析仪chipscope,我们可以观察FPGA片内ROM、FIFO和RAM的读写时序,也可以只比较ROM预存储的数据和RAM最后读出的数据,确认整个读写缓存过程中,数据的一致性是否实现。 2

2016-03-16 12:43:36

FIFO内缓存数据最多。计算此时写入数据-该阶段读出数据即为FIFO的最小深度。 Nwr = 120x = Nwr - Nrd = 120 - 96 = 24.二.为保证数据连续输出,求读取前

2020-02-22 20:37:49

- 恒定8 MB /秒(一旦开始读取,您将需要保持数据速率,不允许上溢/下溢)什么应该是fifo深度?谢谢,以上来自于谷歌翻译以下为原文Hi, I have a design problem where

2019-04-26 10:56:25

FPGA实现。易于适应新的神经网络结构深度学习是一个非常活跃的研究领域,每天都在设计新的 DNN。其中许多结合了现有的标准计算,但有些需要全新的计算方法。特别是在具有特殊结构的网络难以在 GPU 上

2023-02-17 16:56:59

利用FPGA进行图像处理,实现特效显示。请问事先我怎么设定模块?求帮忙说说采集

2014-10-10 00:21:01

点开“memory compiler",然后选择FIFO,同时在右边填入自命名的器件名字。点下一步,在这一步中要设置FIFO的数据宽度,FIFO的深度,FIFO的类型(同步FIFO还是异步FIFO,他们

2012-03-27 12:28:32

设计工程师通常在FPGA上实现FIFO(先进先出寄存器)的时候,都会使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其针对性变差,某些情况下会变得不方便或者将增加硬件成本。

2019-09-02 06:09:41

现在有10个fifo,当其中任何一个满512字节就进行数据处理,应该如何实现呢?多个FIFO的数据输出data_out连接在一起,然后连接到数据处理模块(也是FPGA的一个逻辑模块)的data_in行不行?

2012-09-14 15:11:37

数据进入FPGA的速率高于传出的速率,持续的传输会造成数据的溢出,断续的传输可能会造成数据不连续。使用基于LabVIEW FPGA的DMA FIFO作为主控计算机和FPGA之间的缓存,若DMAFIFO深度设置的合适,FIFO不会溢出和读空,那么就能实现数据输出FPGA是连续的。

2019-10-12 09:05:54

fifo不为空时,用rd clk = 50 MHz连续读出数据。从模拟开始,在5次写入后,fifo空置为空。如何正确计算深度?最初,我的深度为16,所有人都在董事会工作。然后进行实验,我改变了wr和rd

2019-04-09 06:25:58

官方TRM中提到NUC230/240的UART0有提供到64 Bytes的接收缓冲区,UART1及UART2只提供了16Bytes的接收缓冲区,但uart.h文件中RFITL设定仅供到14 Bytes

想问如果想使用64 Bytes FIFO该如何设定,谢谢

2023-06-13 08:43:34

各位大神,有没有用过AXIStream-FIFO IP core的或不用core直接用verilog实现过AXIStream-FIFO功能的,我现在FPGA入门练习(据说华为等大公司喜欢考这种

2014-02-21 16:24:45

图像压缩之后的数据存入fifo,然后经过nrf2401发送。。但是由于图片尺寸比较大,导致fifo深度不够,受限于FPGA芯片尺寸的限制,fifo深度不能再选大了。。。求指导

2015-05-22 14:34:48

理解参考。目录:浅析labview实现相机读取2labview实现can通讯3labview数据写入excel的步骤教程4基于LabVIEW FPGA模块程序设计特点的FIFO深度设定详解5NI VST

2019-06-13 15:37:39

一侧的所有信号都同步于读时钟。设计要求设计宽度为8、缓冲深度为256、输入速率为100MHz、输出速率为50MHz和各类标志信号的FIFO。设计原理FPGA内部没有FIFO的电路,实现原理为利用FPGA

2020-09-02 19:24:24

请问2812型DSP的SCI模块中,接收和发送数据都是16级的FIFO深度是什么意思?对这个16级深度的FIFO不太理解

2023-03-17 11:19:05

嗨,以下条件的FIFO深度是多少?8位并行数据连续出现(即没有突发长度)写入和读取没有理想的循环。写频率= 100MHz读频率= 70MHz谢谢娜文G K.

2020-05-21 07:45:14

嗨,我在逻辑中使用单端口RAM模块,深度为208896,长度为12位。我想通过增加内存深度和字长来提高计算的精度。请让我知道我的fpga的深度和宽度的兼容值。最大块RAM存储器的数据表是14,976 Kb。问候,Tanay

2019-10-31 10:21:53

`立即学习—60天FPGA工程师入门就业项目实战特训营(3月16日开班) 谈谈FIFO阈值的阈值设置及深度计算1.什么是FIFO2.什么情况下使用FIFO3.什么FIFO的阈值4.FIFO的阈值

2020-02-19 21:09:35

首先介绍异步FIFO 的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法; 在传统设计的基础上提出一种新颖的电路结构并对其进行综合仿真和FPGA 实现。

2009-04-16 09:25:29 46

46 使用 LabVIEW FPGA 模块和可重新配置I/O 设备开发测量与控制应用通过使用LabVIEW FPGA 模块和可重新配置I/O(RIO)硬件,NI 为您提供了一种直观可用的解决方案,它可以将FPGA威廉希尔官方网站

的灵活性

2009-07-23 08:09:28 66

66 介绍了PCI 9054 接口芯片的性能及数据传输特点,提出了一种基于PCI 9054 外扩异步FIFO(先进先出)的FPGA(现场可编程门阵列)实现方法。由于PCI 9054 内部FIFO存储器主要用于数据

2010-01-06 15:20:10 44

44 本文主要研究了用FPGA 芯片内部的EBRSRAM 来实现异步FIFO 设计方案,重点阐述了异步FIFO 的标志信号——空/满状态的设计思路,并且用VHDL 语言实现,最后进行了仿真验证。

2010-01-13 17:11:58 40

40 对于利用LabVIEW FPGA实现RIO目标平台上的定制硬件的工程师与开发人员,他们可以很容易地利用所推荐的组件设计构建适合其应用的、可复用且可扩展的代码模块。基于已经验证的

2010-01-18 08:27:15 189

189 介绍了异步FIFO在Camera Link接口中的应用,将Camera Link接口中的帧有效信号FVAL和行有效信号LVAL引入到异步FIFO的设计中。分析了FPGA中设计异步FIFO的难点,解决了异步FIFO设计中存在的两

2010-07-28 16:08:06 32

32 设计工程师通常在FPGA上实现FIFO(先进先出寄存器)的时候,都会使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其针对性变差,某些情况下会变得不方便或者将增加硬

2010-10-27 15:40:30 38

38 摘要:首先介绍异步FIFO的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法;在传统设计的基础上提出一种新颖的电路结构并对其进行

2009-06-20 12:46:50 3661

3661

基于FPGA的FIFO设计和应用

引 言

在利用DSP实现视频实时跟踪时,需要进行大量高速的图像采集。而DSP本身自带的FIFO并不足以支持系统中大量数据的暂时存储

2009-11-20 11:25:45 2126

2126

FPGA设计的高速FIFO电路威廉希尔官方网站

本文主要介绍高速FIFO电路在数据采集系统中的应用,相关电路主要有高速A/D转换器、FPGA、SDRAM存储器等。图1为本方案的结构框图。在大容量

2010-05-27 09:58:59 2225

2225

本文采用VHDL描述语言,充分利用Xilinx公司Spartan II FPGA的系统资源,设计实现了一种非对称同步FIFO,它不仅提供数据缓冲,而且能进行数据总线宽度的转换。

2011-01-13 11:33:43 1743

1743 文中给出了异步FIFO的实现代码和FPGA与DSP的硬件连接电路。经验证,利用异步FIFO的方法,在FPGA与DSP通信中的应用,具有传输速度快、稳定可靠、实现方便的优点。

2011-12-12 14:28:22 51

51 借助NI LabVIEW,将嵌入式应用程序设计、建模并部署到各类处理目标(包括:现成的实时系统和基于FPGA的系统,以及自定义微处理器与微控制器设备)。包括LabVIEW RT模块、LabVIEW FPGA 模块

2012-08-01 15:47:49 369

369 本文探讨如何透过 USB 来设定各种采用FPGA的系统与实现现场升级的弹性。 这种方法还可用来取代热门的 JTAG 组态介面,让用户不再需要用到机板上分立的JTAG连结器,就能降低成本并减

2013-01-10 15:26:35 41

41 为实现目标识别与跟踪的应用目的 ,在基于 TMS320DM642 的 FIFO 基础上扩展存储空间 ,提出一种基于

FPGA实现 SDRAM 控制器的方法。分析所用 SDRAM 的特点和工作原理

2015-10-29 14:05:57 2

2 异步FIFO结构及FPGA设计,解决亚稳态的问题

2015-11-10 15:21:37 4

4 [NI威廉希尔官方网站

]-LabVIEW-FPGA代码模块设计,入门级资料。

2016-05-17 16:41:51 34

34 通过 labview fpga定制硬件。

2016-05-17 17:47:59 24

24 异步FIFO在FPGA与DSP通信中的运用

2016-05-19 11:17:11 0

0 将LabVIEW可编程FPGA模块内嵌到示波器中,同时,内嵌到此系列示波器中的FPGA模块,可以通过LabVIEW FPGA开发工具进行重新编程和定向话设计,本系列示波器主要包括PXIe5170R,PXIe-5171R两种型号。

2018-06-30 07:37:00 4093

4093

基于异步FIFO在FPGA与DSP通信中的运用

2017-10-19 10:30:56 10

10 摘要 利用异步FIFO实现FPGA与DSP进行数据通信的方案。FPGA在写时钟的控制下将数据写入FIFO,再与DSP进行握手后,DSP通过EMIFA接口将数据读入。文中给出了异步FIFO的实现

2017-10-30 11:48:44 1

1 I/O模块;或者在LabVIEW FPGA编程中访问I/O模块从而实现最大的灵活性及性能。您还能通过全新的测试面板及I/O强置功能来快速启动、运行,实现高级调试及系统性能监测。

2017-11-17 08:55:09 2927

2927

每个FPGA芯片(FPGA)是由有限个带有可编程连接预定义资源组成。这些互连资源通过LabVIEW FPGA模块实现用户设计的数字电路。用户创建FPGA VI时设计一个电路示意图,以说明FPGA逻辑

2017-11-18 05:57:01 729

729

可以用来为测试测量系统创建PWM接口。与专用的PWM I/O设备不同的是,LabVIEW FPGA允许自定义应用程序的PWM通道特性和行为,并且可以与其它的测量设备集成和同步。 1. 应用程序概述 LabVIEW FPGA模块和可重配置的I/O板卡可以用来实现各种自定义接口。

2017-11-18 07:18:21 9646

9646

,LabVIEW Real-Time模块和LabVIEW FPGA模块以及PXI-7931R可重配置I/O板卡完成实时仿真,并对I/O信号实现精确、灵活的定时与同步。

2017-11-18 18:24:14 1623

1623 在现代电路设计中,一个系统往往包含了多个时钟,如何在异步时钟间传递数据成为一个很重要的问题,而使用异步FIFO可以有效地解决这个问题。异步FIFO是一种在电子系统中得到广泛应用的器件,文中介绍了一种基于FPGA的异步FIFO设计方法。使用这种方法可以设计出高速、高可靠的异步FIFO。

2018-07-17 08:33:00 7873

7873

对于利用LabVIEW FPGA实现RIO目标平台上的定制硬件的工程师与开发人员,他们可以很容易地利用所推荐的组件设计构建适合其应用的、可复用且可扩展的代码模块。基于已经验证的设计进行代码模块开发

2017-11-24 15:36:03 2153

2153

设计工程师通常在FPGA上实现FIFO(先进先出寄存器)的时候,都会使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其针对性变差,某些情况下会变得不方便或者将增加硬件成本。此时,需要进行自行

2018-11-28 08:10:00 6709

6709

为了解决基于LabVIEWFPGA模块的DMAFIFO深度设定不当带来的数据不连续问题,结合LabVIEWFPGA的编程特点和DMA FIFO的工作原理,提出了一种设定FIFO深度的方法。对FIFO

2019-01-04 14:25:07 4225

4225

根据FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同时发生读写操作。异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

2019-11-29 07:08:00 1608

1608 FPGA电路FIFO设计的源代码

2020-07-08 17:34:37 15

15 问题的有效方法。异步FIFO是一种在电子系统中得到广泛应用的器件,多数情况下它都是以一个独立芯片的方式在系统中应用。本文介绍一种充分利用FPGA内部的RAM资源,在FPGA内部实现异步FIFO模块的设计方法。这种异步FIFO比外部 FIFO 芯片更能提高系统的稳定性。

2020-07-21 17:09:36 1326

1326

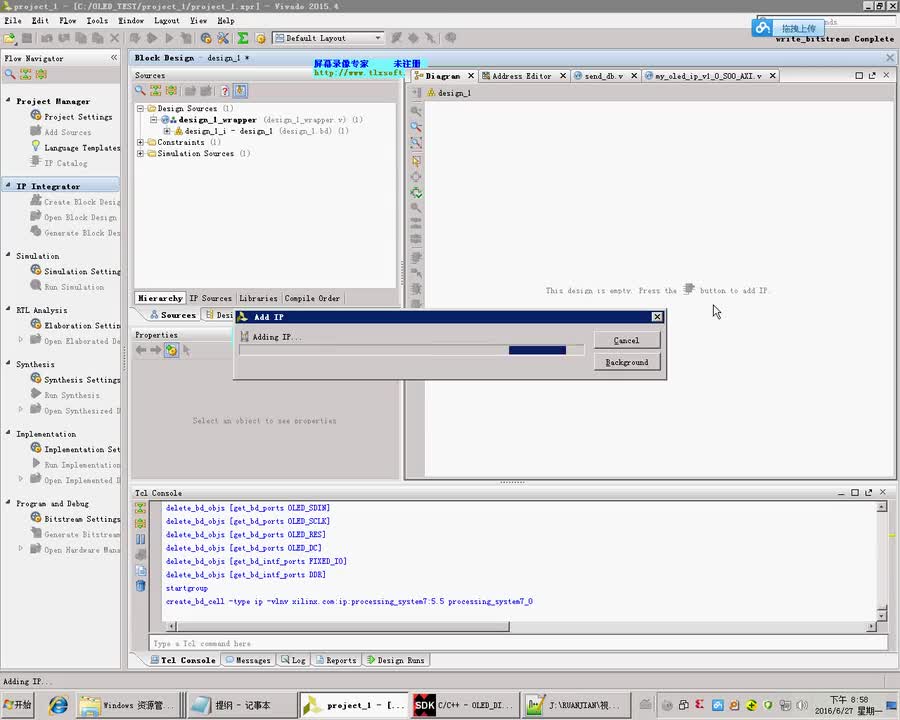

FIFO是FPGA应用当中非常重要的模块,广泛用于数据的缓存,跨时钟域数据处理等。学好FIFO是FPGA的关键,灵活运用好FIFO是一个FPGA工程师必备的技能。本章主要介绍利用XILINX提供的FIFO IP进行读写测试。

2021-02-02 06:24:38 11

11 提出了一种节能并可升级的异步FIFO的FPGA实现。此系统结构利用FPGA内自身的资源控制时钟的暂停与恢复,实现了高能效、高工作频率的数据传输。该系统在Xilinx的VC4VSX55芯片中实现,实际

2021-02-02 15:15:00 16

16 一:fifo是什么 FIFO的完整英文拼写为FirstIn First Out,即先进先出。FPGA或者ASIC中使用到的FIFO一般指的是对数据的存储具有先进先出特性的一个存储器,常被用于数据

2021-03-12 16:30:48 2795

2795

数据缓存下来,那么我们需要开多大的空间缓存这些数据呢?缓存开大了会浪费资源,开小了会丢失数据,如何去计算最小FIFO深度是本文的重点。 本文涵盖了FIFO最小深度计算所有情况: 假如模块A不间断的往FIFO中写数据,模块B同样不间断的从FIFO中读数据

2021-05-11 14:37:08 1950

1950

基于FPGA的UART模块设计与实现介绍说明。

2021-06-01 09:43:30 19

19 FIFO是在FPGA设计中使用的非常频繁,也是影响FPGA设计代码稳定性以及效率等得关键因素。在数据连续读取时,为了能不间断的读出数据而又不导致FIFO为空后还错误的读出数据。可以将FIFO

2021-09-09 11:15:00 6293

6293 FIFO 最小深度计算 例子 - 1:f_wr 》 f_rd,连续读写 写时钟80MHz。 读时钟50MHz。 Burst_Len = 120,也就是要求至少安全写入120个数据。 连续写入和连续

2021-09-10 09:23:28 1505

1505

的基础上。连续无止境的突发不考虑。比如写时钟100M,读时钟50M,无限制的读写,那么FIFO的深度只能是无穷大了,因为写比读快,FIFO一定永远都不够用。所以在实际运用中,不会存在无限制的对FIFO

2022-02-26 17:41:52 3045

3045

FIFO是FPGA项目中使用最多的IP核,一个项目使用几个,甚至是几十个FIFO都是很正常的。通常情况下,每个FIFO的参数,特别是位宽和深度,是不同的。

2022-03-08 11:06:12 4520

4520

在FPGA中对图像的一行数据进行缓存时,可以采用FIFO这一结构,如上图所示,新一行图像数据流入到FIFO1中,FIFO1中会对图像数据进行缓存,当FIFO1中缓存有一行图像数据时,在下一行图像数据来临的时候,将FIFO1中缓存的图像数据读出,并传递给下一个FIFO

2022-05-10 09:59:29 3056

3056 由于平时我们工作中,FIFO都是直接调用IP核,对于FIFO深度选择并没有很在意,而在笔试面试过程中,经常被问及的问题之一就是如何计算FIFO深度。

2022-07-03 17:25:28 2222

2222 无论何时,在复杂的 FPGA 设计过程中,都不可避免地需要在模块之间发送数据,实现这一点的常用的是 FIFO。

2022-09-20 09:10:27 1883

1883 FIFO 是FPGA设计中最有用的模块之一。FIFO 在模块之间提供简单的握手和同步机制,是设计人员将数据从一个模块传输到另一个模块的常用选择。

2023-06-14 08:59:29 223

223 FIFO 是FPGA设计中最有用的模块之一。FIFO 在模块之间提供简单的握手和同步机制,是设计人员将数据从一个模块传输到另一个模块的常用选择。 在这篇文章中,展示了一个简单的 RTL 同步

2023-06-14 09:02:19 461

461 FIFO(First In First Out)是一种先进先出的存储结构,经常被用来在FPGA设计中进行数据缓存或者匹配传输速率。

2023-08-07 15:39:50 445

445 上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

2023-09-07 18:31:35 759

759

电子发烧友App

电子发烧友App

评论