|

基于柔性锁相环路的动态电压恢复器控制方案的研究 摘要:动态电压恢复器(DVR)是一种新型电能质量调节装置,它能有效抑制电网电压波动对敏感负载的影响。介绍了应用于DVR的一种新型的锁相威廉希尔官方网站 —柔性锁相环路〔soft phase locked loop(SPLL)〕和以此为基础的控制方案。 关键词:动态电压恢复器;锁相威廉希尔官方网站 ;电压跌落 1 概述 动态电压恢复器(dynamic voltage restorers简称DVR)是一种保证电网供电质量的新型电力电子设备,主要用于补偿供电电网产生的电压跌落,闪变和谐波等。它的基本结构和在电网中的接入方式如图1所示。DVR本身相当于一个受控电压源[1],它可在电源和敏感负载之间插入一个任意幅值和相位的电压。当电源电压畸变时,通过改变DVR的电压,达到稳定敏感负载电压的目的。

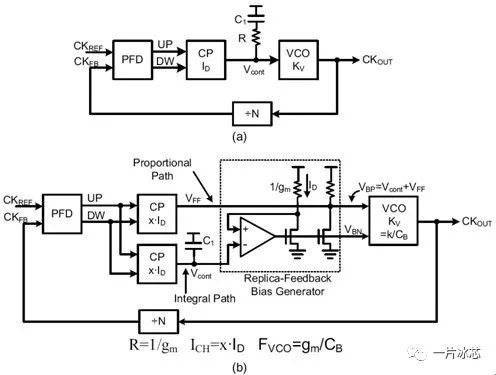

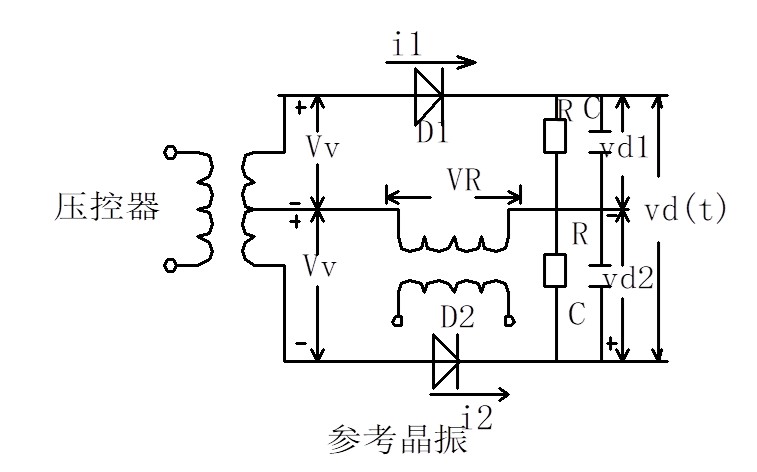

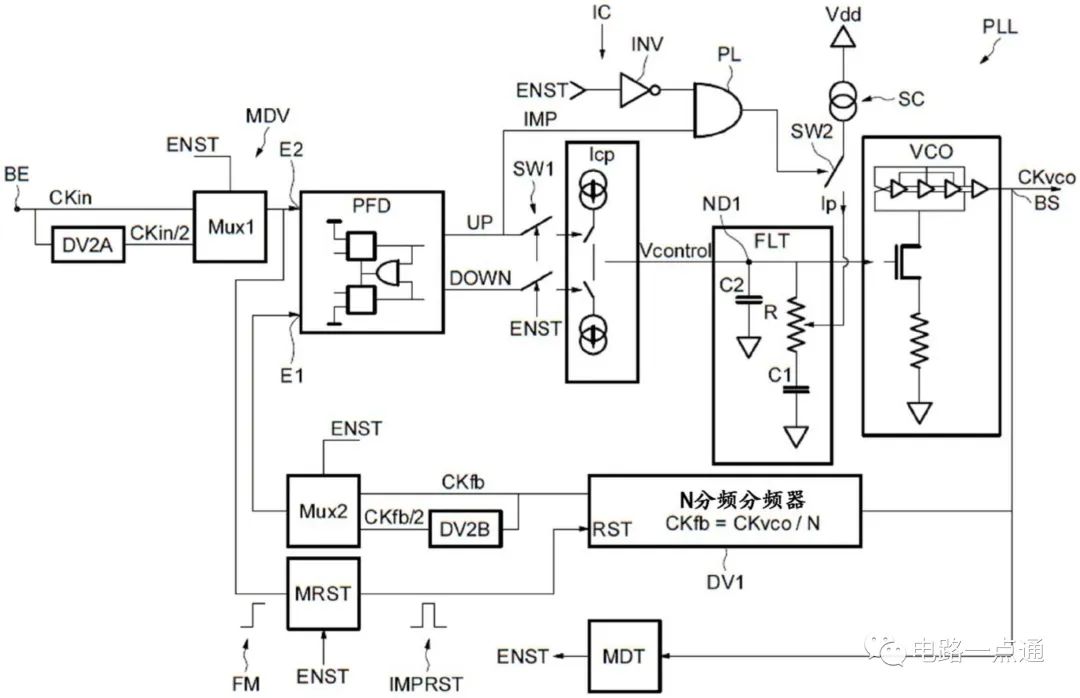

图1 动态电压恢复器的结构和连接图 DVR的主要补偿对象是电网电压的跌落,闪变和谐波,因此,要求其控制系统应具有足够的响应速度,同时,对畸变的输入电压应具有很强的抑制作用。本文提出的基于瞬时无功理论[3]的柔性锁相环路(SPLL)[4]和以此为基础的控制方案能够很好地达到这一要求。 2 柔性锁相环路 为实现以DVR补偿电源侧畸变电压的目的,则获得电源侧电压的相位是首要的任务。获得相位信息的方法有过零比较,最小二乘法,小波分析等多种方法。过零比较结构简单,实现较为容易,但动态响应速度慢,对畸变电压的抑制较差;最小二乘法动态响应速度快,能准确地锁定正序电压的相位,但输入电压存在谐波时性能较差;小波分析性能较好,但结构复杂,实现起来较为困难。 本文介绍的SPLL结构比较简单,动态响应速度快,对畸变输入电压有很强的抑制作用。 SPLL的基本结构如图2所示。把三相输入电压采样后做32变换,即把电压转换到αβ坐标系中。再经pq变换得到uq,变换所使用的角度是锁相的输出θ*,uq的值代表输入电压a相相位和锁相输出相位θ*的差,然后利用一个PI环节将该差调整到零,从而达到相位捕获的目的。下面对原理做详细阐述。

图2 SPLL的控制流程图 如果输入三相电源电压中仅含三相基波正序,则设输入三相电压为 ua= ub= uc= 式中:ω1为角频率; φ为相位。 经过C32变换由三相变至两相,有 如果,此时锁相环输出的角频率为ω,相位为0,则利用锁相环输出的角度进行pq变换,有 频率没有锁定时,uq是一个交流分量,在频率锁定,相位没有锁定时,它是一个直流分量,其大小代表锁相输入与输出之间的相位差信息。在频率,相位完全捕获的情况下,有ω1=ω,φ=0,此时uq=0,它是恒定的直流分量,而且它并不随电源电压幅值的变化而变化。可以看出,只有频率和相位完全捕获的情况下才有uq=0,所以通过把uq调节为0,就可以达到锁相的目的,该结构利用PI环节达到这一目的。同时,因在数字系统中正弦和余弦的值靠查表得到,所以θ*的值不能太大,故每隔一个工频周期复位一次。 假设三相输入电源电压畸变即电压中含有零序、负序和谐波分量。对于零序,做C32变换后其值为0,对结果没有影响,所以不予考虑。此时的三相电压为 ua= ub= uc= 式中:下标为1的表示正序,下标为2的表示负序; n表示谐波次数(当n等于1时表示基波); U表示电压有效值; φ表示初相角; ω为电网电压角频率。 从而可以得到 uq= 由式(5)可以看出,仅有基波正序转换为直流分量,其他分量经过转换都是频率较高的分量。经过滤波,将这些高频分量滤除,则SPLL的输出就不受负序、零序和谐波的影响。这就保证了在畸变输入电压的情况下,SPLL能够正确地锁定输入电压的基波正序。关于滤波,因系统中存在两个积分环节,对高频分量有较强的抑制作用,所以,一般不需要额外的滤波环节。但是当在三相输入电压严重不平衡时,负序分量很大,若要将其完全滤除,所需时间较长,从而影响系统的动态响应时间。为此,可在pq后加入一个滤波环节来加速负序分量的滤除,如图3所示,从而在保证滤除负序分量的情况下,系统有较短的动态响应时间。

图3 改进的SPLL结构框图 3 以SPLL为基础的控制方案 由式(3)可知,uq代表输入电压的相位信息,up代表输入电压的幅值信息。在相位锁定的情况下,前者为零,后者是一仅和幅值有关的直流分量。利用uq构建SPLL达到锁相的目的,而利用up可将理想负载电压转换为一常数和实际输入的电源侧电压经转换后相减,得到有功分量上需要补偿的值,再经反变换即可得到最终的指令。其控制框图如图4所示。

图4 利用瞬时无功获得指令 图4中的上半部分是SPLL,它保证准确的锁定电源侧畸变输入电压的基波正序相位;下半部分是为保持负载电压有恒定的幅值。这种方案对电压的幅值和相位分开考虑,物理意义比较明显。而且,若目标补偿电压的幅值改变,仅须对目标输入up*进行修改,所以比较灵活。如果使用空间矢量PWM调制(SVPWM)就不须对指令进行反变换,从而节省大量资源,该方案就更为适用。 使用这种控制方案,得到DVR的补偿指令,通过三角波比较等跟踪方式控制逆变器的工作,即可达到补偿畸变电压的目的。其流程如图5所示。

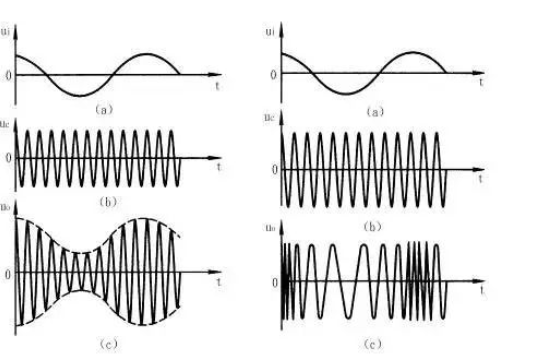

图5 DVR工作流程图 4 试验结果 以一台三相四线制6kW的DVR为平台,对该控制方案进行试验验证。控制方案的实现采用TI公司的DSP2000系列的C32。利用此装置进行电压跌落下的锁相和补偿试验。 图6是三相输入电压中a相电压和锁相输出的电压波形,可以看出,该锁相方式具有很快的响应速度,很好的精度,并且对畸变电压有很强的抑制作用。

图6 a相输入电压和SPLL输出 图7是采用本文所提出的控制方案时,补偿电压跌落的试验结果。可以看出,此时负载电压和网侧电压同相位,网侧的电压跌落和谐波得到了很好的补偿。

图7 网侧电压和补偿后的负载电压 5 结语 本文提出了一种以瞬时无功理论为基础的锁相方式——SPLL和以此为基础的控制方案,由理论分析和试验验证可以看出SPLL的动态响应速度快,同时,对畸变输入电压有很强的抑制作用,而控制方案具有物理意义明显,动态响应速度快,控制灵活简便和补偿效果好等优点。该方案对DVR控制方案的研制提供了一种新的选择。 |

基于柔性锁相环路的动态电压恢复器控制方案的研究

- 恢复器(5112)

相关推荐

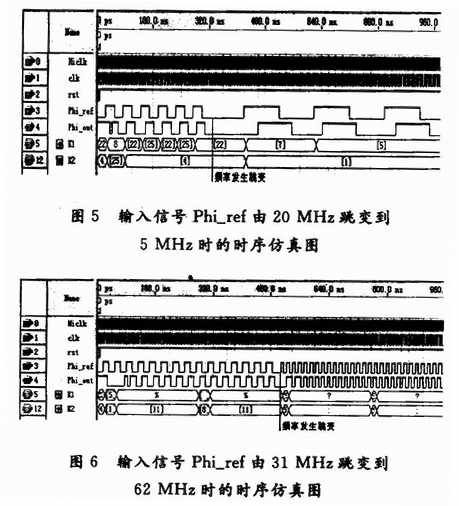

基于DSP Builder系统模型的数字锁相环设计

本文采用一种基于比例积分(PI)控制算法的环路滤波器应用于带宽自适应的全数字锁相环,建立了该锁相环的数学模型

2010-10-14 10:03:25 1270

1270

1270

1270

锁相环锁定时间取决于哪些因素

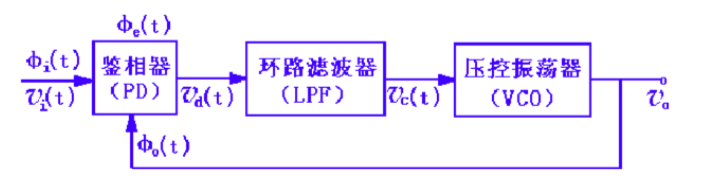

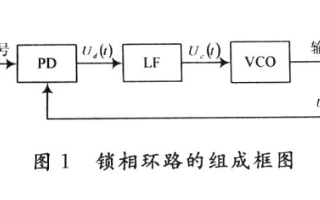

锁相环路是由鉴相器《简称PD》、还路滤波器〔(简称LPF或LE和压控振荡器(简称VCO〕三个部件组成闭合系统。这是一个基本环路,其各种形式均由它变化而来。

2024-01-31 15:54:51 596

596

596

596

锁相威廉希尔官方网站 教程下载

;/strong><br/><strong>第1章&nbsp; 锁相环路的基本工作原理</strong>

2009-10-08 15:37:53

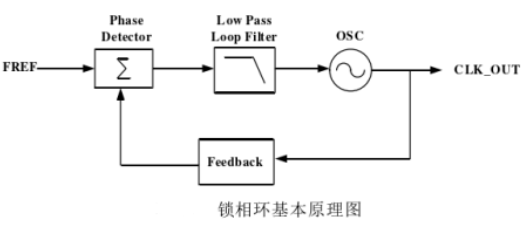

锁相环控制频率的原理

保证环路所要求的性能, 增加系统的稳定性。压控振荡器受滤波器输出的电压控制, 使得压控振荡器的频率向输入信号的频率靠拢, 也就是使差拍频率越来越低, 直至消除频率差而锁定。锁相环在开始工作时, 通常输入

2022-06-22 19:16:46

锁相环在电力系统中的应用

、软件锁相环原理软件锁相环采用瞬时无功理论锁相原,其基本结构如下图所示。三相电压usa,u***,usc经坐标变换后得到usd,usq,这里的坐标变换相当于硬件锁相环中的鉴相器,PI调节器相当于环路滤波器

2015-01-04 22:57:15

锁相环的原理,特性与分析

本帖最后由 gk320830 于 2015-3-7 20:18 编辑

锁相环的原理,特性与分析所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL 表示。

2008-08-15 13:18:46

锁相环知识

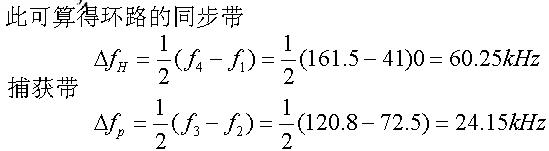

、压控振荡器(VCO) 四、环路滤波器(LPF) 五、固有频率ωn和阻尼系数x 的物 理意义 六、同步带和捕捉带 •第二部分:锁相环实验 •实验一、PLL参数测试 •一、压控灵敏度KO的测量 •二

2011-12-21 17:35:00

锁相环环路滤波器电路问题

如图所示,该锁相环电路VCOin的电压波形如右图所示,我需要得到的是该稳定的电压,如果把C18由0.1uf改成10uF,锁相环又不锁相了,输出电压一直为5V。需要如何选择滤波电容的参数来将该电压进行滤波。

2016-09-11 22:23:46

锁相环路是什么?有何特点

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号

2022-01-11 06:34:28

AD9957锁相环一直失锁

如题,AD9957的锁相环一直失锁,不用锁相环输出点频信号时正常的,用了锁相环后,PLL_LOCK信号一直为低,sync_clk输出信号也不是稳定的周期信号,环路滤波器的值有点误差,因为现有的器件没有那么精确的电容电阻值,问下锁相环的控制除了控制CFR3之外还有别的要注意的么?

2018-12-10 09:30:24

SFS11000Y-LF锁相环

`SFS系列是一个固定频率PLL解决方案,集成了鉴相器,环路滤波器,VCO和PIC控制器。它消除了对任何外部编程的需求,从而将设计复杂性降至最低。它是需要500 MHz至15 GHz范围内的单个频率

2021-04-03 17:05:46

一种基于ADF4106的锁相环频率合成器应用实例介绍

介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。 关键词:ADF4106,锁相环,频率合成器,环路滤波器

2019-07-04 07:01:10

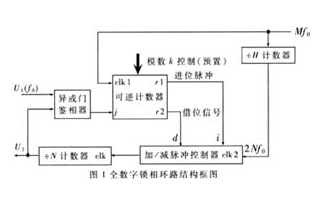

全数字锁相环的设计及分析

Phase-Locked Loop)逐步发展起来。所谓全数字锁相环,就是环路部件全部数字化,采用数字鉴相器、数字环路滤波器、数控振荡器构成锁相环路,并且系统中的信号全是数字信号。与传统的模拟电路实现的锁相环

2010-03-16 10:56:10

关于锁相环的组成你了解多少?

锁相环路是一种反馈控制电路,简称锁相环(PLL)。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。锁相环通常由鉴相器(PD)、环路滤波器(LF

2019-03-17 06:00:00

基于锁相环的可变量程转速控制系统

在电机转速控制系统中,经常需要对电机的转速信号进行测量和处理,以达到精确控制转速的目的。通常采用旋转编码器、测速发电机等传感器测量转速,不但体积大、安装不便,而且价格高;而利用锁相环路可用很低的成本

2011-07-13 17:08:51

基于双dq坐标系的自解耦三相锁相环算法

0引言锁相环广泛应用于如电能质量分析、电力系统保护、并网变换器以及无功补偿等现代工业控制领域。已有研究人员对单dq坐标系三相锁相环算法进行了分析,通过对电压矢量的坐标变换及PI控制,实现理想电压工况

2021-09-06 09:24:01

如何配置锁相环并为总线提供时钟呢

由于一般的晶振受限于工艺与成本,做不到很高的频率,可在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路来实现稳定且高频的时脉冲讯号。本例通过MC9S12XS128这款

2021-12-10 06:26:47

高频锁相环路LMX2430电子资料

概述:LMX2430是一款高频锁相环路芯片,它可在2.25V至2.75V的电压范围内操作。这三款芯片的其他功能包括可随意选择的同步或异步停机模式、1mA或4mA的可编程电荷泵电流、内置超时计数器的快速锁定威廉希尔官方网站

、...

2021-04-08 07:24:00

高频锁相环路LMX2433相关资料分享

LMX2433是一款高频锁相环路芯片,它可在2.25V至2.75V的电压范围内操作。这三款芯片的其他功能包括可随意选择的同步或异步停机模式、1mA或4mA的可编程电荷泵电流、内置超时计数器的快速锁定

2021-04-13 07:27:00

锁相威廉希尔官方网站 教程下载

第1章 锁相环路的基本工作原理.ppt第2章 环路跟踪性能.ppt第3章 环路噪声性能.ppt 第4章 环路捕获性能.ppt第5章 集成锁相环

2008-04-21 15:09:30 0

0

0

0pll锁相环

所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称

2008-08-15 12:41:05 332

332

332

332模拟锁相环应用实验

一、实验目的1、掌握模拟锁相环的组成及工作原理。2、学习用集成锁相环构成锁相解调电路。3、学习用集成锁相环构成锁相倍频电路。

二、锁相环路的基本原理

2009-03-22 11:44:37 126

126

126

126用锁相环路实现任意频率变换威廉希尔官方网站

介绍了锁相环路的工作原理以及MM74HC4046AN锁相环芯片的引脚功能。给出了利用锁相环进行频率变换的方案和用方波信号进行频率变换的实际电路,并对环路和相位进行了分析。

2009-04-27 15:42:23 50

50

50

50集成锁相环路解码器LM567及其在检测电路中的应用

美国国家半导体公司生产的集成锁相环路解码器LM567以其优良的性能和低廉的价格而在各种解码电路中获得了广泛的应用.本文详细介绍了LM567的内部结构、工作原理、性能指标和选择

2009-04-30 15:22:57 156

156

156

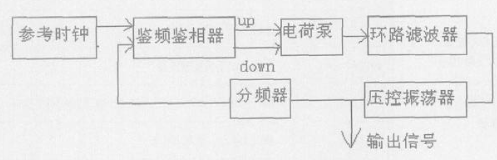

156基于时钟恢复系统中的锁相环电路的设计

本文主要设计了基于相位控制威廉希尔官方网站

的时钟恢复系统的PLL 锁相环路。分别对各单元电路结构——鉴频鉴相器、电荷泵、环路滤波器、压控振荡器、分频器进行设计。采用2.5V,0.25μm

2009-06-01 15:51:53 54

54

54

54智能全数字锁相环的设计

智能全数字锁相环的设计:在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智能配

2009-06-25 23:32:57 72

72

72

72基于FPGA的全数字锁相环路的设计

介绍了应用VHDL威廉希尔官方网站

设计嵌入式全数字锁相环路的方法。详细叙述了其工作原理和设计思路,并用可编程逻辑器件FPCA予以实现。

2009-07-21 16:46:41 0

0

0

0锁相环的应用

在载波调制信号的相干解调中,必须提取相干载波,如何从接收信号中提取相干载波,一般方法是采用锁相环路。它能从淹埋在噪声中的微弱信号中提取出相干载波,从而大大提高接

2009-08-03 10:09:06 4

4

4

4锁相环频率合成器(Motorola集成电路应用威廉希尔官方网站 丛书)

锁相环频率合成器(Motorola集成电路应用威廉希尔官方网站

丛书):锁相环路设计基础,鉴相器,压控振荡器,程序分频器,前置分频器,单片集成锁相环路等内容。

2009-09-05 08:20:52 0

0

0

0基于虚拟磁链和锁相环的无电网电压传感器并网逆变器的研究

基于虚拟磁链和锁相环的无电网电压传感器并网逆变器的研究:为了提高并网逆变器的可靠性和抗电网电压波动,同时进一步降低并网逆变器的成本,提出了一种基于锁相环和虚

2010-02-18 13:16:58 42

42

42

42锁相环动态频相跟踪特性分析

在分析锁相环工作原理的基础上,利用传递函数法建立了锁相环跟踪误差的二阶等效模型,并对锁相环的动态频相跟踪特性进行了理论分析.利用MATLAB构建了锁相环的仿真

2010-03-01 18:14:11 32

32

32

32锁相环原理

锁相环原理

锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。其作用是使得电路上的时钟和某一外部时钟的相位同步。因锁相环可以

2007-08-21 14:46:04 4879

4879

4879

4879锁相环路跟踪特性的测量方法

锁相环路跟踪特性的测量方法:锁相环路的跟踪特性是可以测量的。以CMOS集成锁相环路5G4046构成的跟踪滤波器如图6-2(a)。在电源电压为10V,中心频率fo=1

2008-04-21 11:53:40 1225

1225

1225

1225

锁相环的研究和频率合成

锁相环的研究和频率合成一、实验目的:1. 振荡器(VCO)的V—f 特性的研究2. 对称波锁相环基本特性的研究3. 利用锁相环实现频率合成二、锁相环原理:

2009-03-06 20:02:52 1939

1939

1939

1939

基于ADF4106的锁相环频率合成器

介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。

2009-05-05 19:57:57 2585

2585

2585

2585

智能全数字锁相环的设计

摘要: 在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智

2009-06-20 12:39:32 1408

1408

1408

1408

模拟锁相环,模拟锁相环原理解析

模拟锁相环,模拟锁相环原理解析

背景知识:

锁相威廉希尔官方网站

是一种相位负反馈控制威廉希尔官方网站

,它利用环路的反馈原理来产生新的频率点。它的主要

2010-03-23 15:08:20 5780

5780

5780

5780CMOS高速锁相环设计

本文涉及的锁相环路是基于相位控制的时钟恢复系统。目的是用锁相环电路-PLL和DLL实现USB2.0收发器宏单远UTM的时钟恢复木块。其中PLL环路构成的时钟发生器奖外部晶振的12MHZ的正弦信号

2011-03-03 14:58:34 50

50

50

50集成锁相环芯片应用 PPT培训资料

集成锁相环芯片类型较多,现介绍CC4046(或CD4046)和J691以及NE564(工作频率可达 50MHz)集成锁相环。 一、CC4046集成锁相环芯片 CC4046和J691均为CMOS单片锁相环路,工作频率1MHz,其逻辑结构和

2011-03-15 10:05:11 263

263

263

263FPGA在锁相频率合成中的应用

锁相环路由于具有高稳定性、优越的跟踪性能及良好的抗干扰性,在频率合成中得到了广泛应用。但简单的锁相环路对输出频率、频率分辨率等指标往往不能满足要求,所以要对简单锁相环

2011-05-28 13:42:13 943

943

943

943

扩频通信的数字锁相环设计

针对扩频通信系统的载波同步,提出一套完善的数字锁相环设计方案. 该方案利用新颖的可控根法完成1~3阶模拟锁相环(APLL)环路参数设计,并实现从模拟域到数字域的转换,得到的数字锁相

2011-08-26 16:10:38 122

122

122

122基于PSpice的动态电压恢复器研究

随着现代电力电子设备的广泛应用, 电压跌落已日益成为电力部门和用户关注的电能质量问题。介绍了减少电压跌落的几种方法,分析了采用动态电压恢复器(Dynamic Voltage Restorer)的优

2011-11-03 10:46:35 24

24

24

24锁相环在不同领域中的应用汇总

由于锁相环路有上述种种优良的特性,再加上集成锁相环的出现,使锁相环路在电子威廉希尔官方网站

等各个领域获得了广泛的应用,下面对锁相环在不同领域中的应用情况作一简单的概述。 1 在通

2012-09-21 10:09:10 3819

3819

3819

3819pLL射频锁相环基础知识详解

锁相环路为什幺能够进入相位跟踪,实现输出与输入信号的同步呢?因为它是一个相位的负反馈控制系统。这个负反馈控制系统是由鉴相器(PD)、环路滤波器(LF)和电压控制振荡器(VCO)三个基本部件组成的,基本构成如图:

2017-04-25 12:03:00 0

0

0

0PLL锁相环的特性、应用与其基本工作过程

PLL(Phase Locked Loop),也称为锁相环路(PLL)或锁相环,它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

2017-05-22 10:11:40 8672

8672

8672

8672

锁相环是什么?锁相环原理及锁相环在调制和解调电路中的应用

锁相环就是锁定相位的环路,它一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。

2017-07-24 15:07:12 27903

27903

27903

27903

基于LMX2315的读写器锁相环应用

锁相环路在通信系统中得到了广泛的应用。本文针对超高频RFID读写器的工作特点,设计了基于数字频率合成器LMX2315的锁相环路,给出了锁相环伪随机跳频程序流程图。

2017-09-07 18:54:00 18

18

18

18基于DSP电网动态电压恢复器模拟系统装置

本文旨在通过设计一款分布式电网动态电压恢复器模拟系统装置,解决电力设备运行过程中电压暂降或中断情况下的动态电能安全问题,.装置采用直流一交流及交一直一交双重结构,控制系统采用TMS320F28335

2017-11-10 17:26:56 6

6

6

6锁相环捕捉过程的定性分析

锁相环捕捉过程的定性分析 若环路原本是失锁的,但环路能够通过自身的调节由失锁进入锁定的过程称为捕捉过程。一般情况下,捕捉带不等于同步带,且前者小于后者,锁相环路的捕捉过程属于非线性过程,在工程上广泛

2017-11-16 15:37:35 4

4

4

4基于DSP的逆变电源锁相环的设计与研究

采用基于DSP的数字锁相环(DPLL )对高频逆变电源输出频率的实时控制,可实现逆变器工作频率对负载谐振频率的同步跟踪 ,确保逆变器开关器件工作在零电压电流软开关( ZV ZCS)状态 ,显著减小

2017-12-11 13:57:33 14

14

14

14锁相环在调制和解调中的应用及概念解析

许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

2018-01-22 11:18:45 13404

13404

13404

13404

中压动态电压恢复器的虚拟阻抗控制策略

中压动态电压恢复器(dynamic voltage restorer,DVR)可用于有效保护大范围的用户不受电压暂降的影响,但不能补偿其下游馈线上发生故障时的电压扰动。提出了将DVR控制为虚拟阻抗

2018-02-02 09:53:23 18

18

18

18正点原子开拓者FPGA视频:PLL锁相环实验

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

2019-09-20 07:05:00 3503

3503

3503

3503

采用Spartan2系列FPGA器件实现全数字锁相环路的设计和仿真验证

威廉希尔官方网站

的发展,不仅能够制成频率较高的单片集成锁相环路,而且可以把整个系统集成到一个芯片上去,实现所谓片上系统SOC(System on a chip)。因此,可以把全数字锁相环路作为一个功能模块嵌入SOC,构成片内锁相环。下面介绍采用VHDL威廉希尔官方网站

设计DPLL的一种方案。

2020-07-23 16:23:25 1087

1087

1087

1087

采用二阶无源环路滤波器实现三阶电荷泵锁相环的设计

,为了减小压控振荡器控制电压的纹波,它采用了二阶无源环路滤波器,这样就构成了三阶电荷泵锁相环。系统级设计与仿真验证是锁相环设计的第一步和关键的一步。本文对一种用作时钟倍频器的三阶电荷泵锁相环进行了系统级设计与仿真验证,仿真环境采用SIMULINK。

2020-07-24 09:59:51 2564

2564

2564

2564

锁相环路的组成、的基本特性和应用分析

锁相环路(Phase Lock Loop,PLL)是一种自动相位控制(APC)系统,是现代电子系统中应用广泛的一个基本部件。它的基本作用是在环路中产生一个振荡信号(有时也称本地振荡),这个信号的频率

2020-08-05 14:15:24 5088

5088

5088

5088

使用FPGA实现数字锁相环的设计资料说明

锁相环路是一种反馈控制电路,简称锁相环( PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 所以锁相环通常

2020-08-06 17:58:25 24

24

24

24锁相环路的典型应用实例详细说明

基本锁相环路是由鉴相器、低通滤波器以及压控振荡器构成的相位负反馈系统,具有一个频率输入端口,一个电压输出端口以及一个频率输出端口,通常,模拟模拟锁相环的鉴相器由模拟乘法器承担,压控振荡器由弛张振荡器承担。

2020-12-04 08:00:00 3

3

3

3基于锁相环路实现CPFSK中频调制器的设计方案

,具有广泛的应用价值。本文介绍在我国磁悬浮列车车地通信系统中应用的一种CPFSK中频调制器,其核心是基于锁相环路的CPFSK信号调制威廉希尔官方网站

。系统要求中频频率为280 MHz,在信道带宽25 MHz以内

2021-04-05 09:22:00 2491

2491

2491

2491

锁相环(PLL)的工作原理及应用

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

2022-03-29 09:54:55 11472

11472

11472

11472锁相环是如何实现倍频的?

锁相环是如何实现倍频的? 锁相环(Phase Locked Loop, PLL)是一种电路,用于稳定和恢复输入信号的相位和频率。它可以广泛应用于通信、计算机、音频等领域中。其中一个重要的应用就是

2023-09-02 14:59:37 1594

1594

1594

1594如何用锁相环恢复载波同步信号?

如何用锁相环恢复载波同步信号? 锁相环(PLL)是一种电路,可用于恢复和跟踪输入信号的频率和相位。PLL常用于电信、通讯和控制系统中,以恢复和跟踪载波同步信号。本文将介绍锁相环如何恢复载波同步信号

2023-10-30 10:56:38 356

356

356

356基于柔性锁相环路的动态电压恢复器控制方案的研究

简介:动态电压恢复器(DVR)是一种新型电能质量调节装置,它能有效抑制电网电压波动对敏感负载的影响。介绍了应用于DVR的一种新型的锁相威廉希尔官方网站

—柔性锁相环路〔softphase locked loop(SPLL)〕和以此为基础的控制方案。

2023-11-09 08:31:40 0

0

0

0锁相环路的工作原理

简介:锁相环路的工作原理

§1-2 锁相环路的工作原理

锁相环路实质上是一个相差自动调节系统。为了掌握环境的工作原理,理解环 路工作过程中发生的物理现象,必须导出环路的相位

2023-11-09 15:16:24 0

0

0

0环路的跟踪状态和锁定状态的区别?锁相环路的锁定状态应满足什么条件?

环路的跟踪状态是指锁相环锁定后的状态,即环路中的压控振荡器(VCO)的输出信号的相位能够自动跟踪输入信号的相位,从而保持恒定的稳态相位差。

2024-01-30 14:18:32 196

196

196

196为什么说锁相环相当于一个窄带跟踪滤波器

锁相环路与自动频率控制电路有何区别?为什么说锁相环相当于一个窄带跟踪滤波器 锁相环路(PLL)和自动频率控制电路(AFC)是常见的频率调节电路,它们的主要区别在于功能和应用场景。 首先,我们来探讨

2024-01-31 15:24:57 180

180

180

180锁相环路锁定状态的条件及类型

基本锁相环通常由锁相检测器(Phase Detector)、低通滤波器(Loop Filter)和令牌圈振荡器(VCO)组成。它是最简单的锁相环形式,用于频率和相位同步。

2024-01-31 16:00:55 217

217

217

217

电子发烧友App

电子发烧友App

评论