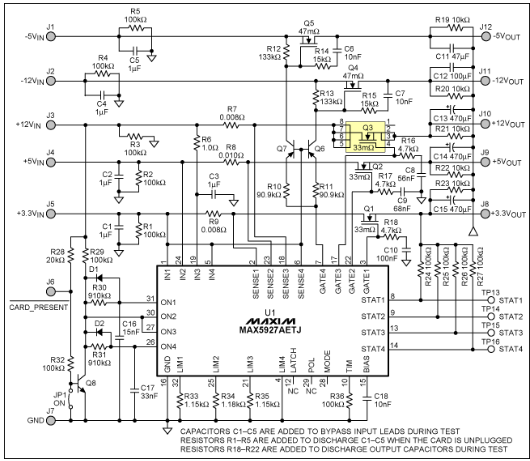

摘要:本文介绍5通道热插拔电路,它可以同时处理顺序接通的正负输入电压。其独特的配置支持两路没有断路器保护的负压通道,以及由一个MAX5927A正电压热插拔控制器控制的3路正电源通道。提供的测试数据表明,电路满足5路电源所要求的负载供电和上电排序要求。

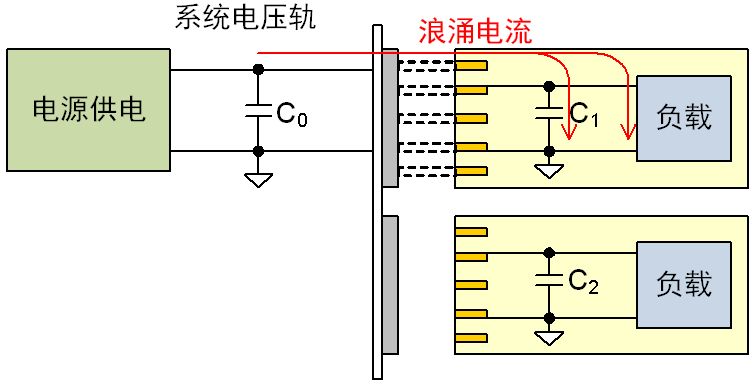

图1. 5通道热插拔电路控制3路正电源和2路负电源

虽然延迟要求和故障管理是针对这一设计的,但可以改变这一延迟以满足其他时序要求。如果需要,故障管理可以改为自动重试模式。

通过(R29 + R30) - C16时间常数将通道1相对于通道2和通道3延时11.8ms接通;可以增大C16以加大延时。通道1开始接通10.8ms后,STAT1变为高电平。

通过(R29 + R31) - C17时间常数将通道4和通道5相对于通道2和通道3延时28ms接通;可以增大C17以加大延时,或者减小R31,以缩短延时。通道4和通道5开始接通10.8ms后,STAT4变为高电平。

MODE置位(开引脚28)以配置MAX5927A为上电排序模式。

内部上拉把LATCH置为高电平,将MAX5927A配置为锁存故障管理。如果通道1至通道3中的任意一个出现故障,所有通道将被关断,直到低电平有效CARD_PRESENT进入下一关断和接通周期。

GATE4的栅极充电电流输出是60µA至100µA,但是在对称电路R4–Q7和R5-Q6中被分成30µA至50µA。GATE4的电压可以比VIN4(3.3V)高5.3V,或者接通时≤+8.6V,关断时接近0V。接通时,VQ6(BASE) = VQ7(BASE) = 3.3V,VQ6(EMITTER) = VQ7(EMITTER) ≈ 3.9V,关断时为0V。R4和R5上相等的压降使得Q6和Q7均分电流。R6和R7上相等的电流在Q4和Q5上产生相等的栅极驱动。关断状态下,GATE4 = 0V时的栅极驱动为0V。Q4和Q5的关断速度取决于流过R6至R7的栅极放电电流。

+5V和+12V通道的+3.3V延时 = 11.8ms (请参考图2)

+3.3V通道的-5V延时 = 16.2ms (请参考图3)

-5V负载关断时间 = 1ms (请参考图4和图5)

-12V负载关断时间 = 4ns (请参考图6和图7)

-12V输出电压摆率 ≈ 1V/ms (请参考图8)

-12V负载电容充电电流 ≈ 80mA (请参考图9)

-5V输出电压摆率 ≈ 1V/ms (请参考图10)

-5V负载电容充电电流 ≈ 55mA (请参考图11)

+3.3V输出电压摆率 ≈ 1V/ms (请参考图12)

+3.3V负载电容充电电流 ≈ 400mA (请参考图12)

3A负载+3.3V接通,不触发断路器(请参考图13)

+3.3V断路器在3.22A时关断(请参考图14)

+5V负载电容充电电流 ≈ 500mA (请参考图15)

+5V输出电压摆率 ≈ 1V/ms (请参考图15)

2.4A负载+5V接通,不触发断路器(请参考图16)

+5V断路器在2.87A时关断(请参考图17)

+12V负载电容充电电流 ≈ 500mA (请参考图18)

3A负载+12V接通,不触发断路器(请参考图19)

+12V断路器在3.1A时关断(请参考图20)

+5V在 ≈ 4A时启动短路电路(请参考图21)

+12V在 ≈ 5.7A时启动短路电路(请参考图22)

图2. +12V至+3.3V接通延时,没有负载

Ch1 = Q8BASE(CARD_PRESENT), Ch2 = +3.3VOUT, Ch3 = +12VOUT, Ch4 = -5VOUT

注释:+12VOUT和+3.3VOUT之间有11.8ms延时。

图3. +3.3V至-5V接通延时,没有负载

Ch1 = Q8BASE, Ch2 = +3.3VOUT, Ch3 = +12VOUT, Ch4 = -5VOUT

注释:+3.3VOUT和-5VOUT之间有16.2ms延时。

图4. -5V栅极相对于+3.3VGATE关断,没有负载

Ch1 = Q8BASE, Ch2 = +3.3VGATE, Ch3 = +5VGATE, Ch4 = -5VGATE

注释:-5V栅极关断较慢;当1 < VGATE < 3V (2.5V,典型值)时,FET关断。由此,正电压通道关断1.5ms至4ms后,-5V栅极完全关断。

图5. -5V负载关断,50mA负载

Ch1 = Q8BASE, Ch2 = -5VGATE, Ch3 = -5VOUT, Ch4 = IIN(-5V)

注释:虽然由于输出电容放电导致VOUT(-5V)没有达到0V,-5V在1ms内下降至零。

图6. -12V栅极关断,没有负载

Ch1 = Q8BASE, Ch2 = +3.3VGATE, Ch3 = +12VGATE, Ch4 = -12VGATE

注释:-12V栅极关断较慢;当1 < VGATE < 3V (2.5V,典型值)时,FET关断。由此,正电压通道关断1ms至4ms后,-12V栅极完全关断。

图7. -12V负载关断,150mA负载

Ch1 = Q8BASE, Ch2 = -12VGATE, Ch3 = -12VOUT, Ch4 = IIN(-12V)

注释:虽然由于输出电容放电导致VOUT(-12V)没有达到0V,-12V输入在4ms内降到零。

图8. -12V接通波形

Ch1 = Q8BASE, Ch2 = -12VGATE, Ch3 = -12VOUT, Ch4 = IIN(-12V)

注释:接通顺序,80Ω阻性负载 = 150mA。

图9. -12V接通波形,没有负载

Ch1 = Q8BASE, Ch2 = -12VGATE, Ch3 = -12VOUT, Ch4 = IIN(-12V)

注释:IIN(PK) = 80mA,对输出电容充电。

图10. -5V接通波形,100Ω阻性负载 = 50mA

Ch1 = Q8BASE, Ch2 = -5VGATE, Ch3 = -5VOUT, Ch4 = IIN(-5V)

注释:-5V摆率大约为1V/ms。

图11. -5V接通波形,没有负载

Ch1 = Q8BASE, Ch2 = -5VGATE, Ch3 = -5VOUT, Ch4 = IIN(-5V)

注释:IIN(PK) = 55mA,对输出电容充电。

图12. +3.3V接通波形,没有负载

Ch1 = Q8BASE, Ch2 = +3.3VGATE, Ch3 = +3.3VOUT, Ch4 = IIN(+3.3V)

注释:IIN(PK) = 400mA,对输出电容充电;+3.3V摆率大约为1V/ms。

图13. +3.3V接通波形,1.1Ω负载 = 3A

Ch1 = Q8BASE, Ch2 = +3.3VGATE, Ch3 = +3.3VOUT, Ch4 = IIN(+3.3V)

图14. +3.3V过流关断

Ch1 = STAT1, Ch2 = VGATE (+3.3V), Ch3 = +3.3VOUT, Ch4 = IOUT(+3.3V) 0.5A/div

注释:IOUT和VOUT减小是由于输出电容向恒阻负载放电。测得的触发电流为3.22A。*

图15. +5V接通负载电容充电电流,没有负载

Ch1 = Q8BASE, Ch2 = +5VGATE, Ch3 = +5VOUT, Ch4 = IIN(+5V)

注释:IIN(PK) = 500mA,对输出电容充电。

图16. +5V接通电流,2.083Ω负载 = 2.4A

Ch1 = Q8BASE, Ch2 = +5VGATE, Ch3 = +5VOUT, Ch4 = IIN(+5V)

图17. +5V过流关断

Ch1 = STAT2, Ch2 = VGATE (+5V), Ch3 = +5VOUT, Ch4 = IOUT(+5V) 0.5A/div

注释:IOUT和VOUT减小是由于输出电容向恒阻负载放电。测得的触发电流为2.87A。

图18. +12V启动电流,没有负载

Ch1 = Q8BASE, Ch2 = +12VGATE, Ch3 = +12VOUT, Ch4 = IIN(+12V)

注释:IIN(+12Vpk) = 500mA,对输出电容充电。

图19. +12V接通电流,4Ω负载 = 3A

Ch1 = Q8BASE, Ch2 = +12VGATE, Ch3 = +12VOUT, Ch4 = IIN(+12V)

图20. +12V过流关断

Ch1 = STAT3, Ch2 = VGATE (+12V), Ch3 = +12VOUT, Ch4 = IOUT(+3.3V) 0.5A/div

注释:IOUT和VOUT减小是由于输出电容向恒阻负载放电。测得的触发电流为3.1A。

图21. 短路电路的+5V启动电流

Ch1 = Q8BASE, Ch2 = +5VOUT, Ch3 = +5VGATE, Ch4 = IIN(+5V)

注释:触发时的4A负载电流。

图22. 短路电路的+12V启动电流

Ch1 = Q8BASE, Ch2 = VOUT, Ch3 = VGATE, Ch4 = IOUT

注释:触发时的5.7A负载电流。

更详细的图(PDF, 237kB)

图23. 参考设计PCB元件布局

更详细的图(PDF, 330kB)

图24. 顶层

图25. 底层

*注意,图14、图17和图20使用了特殊的电流探针,只显示了真值的72%。使用可调恒流负载测量断路器电流,标出了关断时的点。

引言

本文介绍的5通道电路虽然只采用了一个MAX5927A 4通道热插拔控制器,却可以实现3路正电源和2路负电源的热插拔功能。图1电路满足以下负载供电和上电排序要求:- 2A时,Ch1 = +3.3V (电路在 ≥ 3A时断电)

- 1.6A时,Ch2 = +5V (电路在 ≥ 2.4A时断电)

- 2A时,Ch3 = +12V (电路在 ≥ 3A时断电)

- 150mA时,Ch4 = -12V (没有电路断电动作)

- 50mA时,Ch5 = -5V (没有电路断电动作)

- 启动顺为:通道2 (+5V)和通道3 (+12V)在低电平有效CARD_PRESENT变为低电平时立即接通。STAT2和STAT3在低电平有效CARD_PRESENT变为低电平10.8ms后,变为高电平。

- 通道1 (+3.3V)相对于通道2和通道3延迟11.8ms接通。通道1接通10.8ms后,STAT1变为高电平。

- 通道4 (-12V)和通道5 (-5V)相对于通道2和通道3延迟27.8ms接通。通道4和通道5接通10.8ms后,STAT4变为高电平。

- 锁存故障管理。如果通道1至通道3中的任意一个出现错误,所有通道将被关闭,直到低电平有效CARD_PRESENT进入下一关断和接通周期。

图1. 5通道热插拔电路控制3路正电源和2路负电源

虽然延迟要求和故障管理是针对这一设计的,但可以改变这一延迟以满足其他时序要求。如果需要,故障管理可以改为自动重试模式。

热插拔控制器选择

之所以选择MAX5927A,是由于它具有特殊的+15V绝对最大输入电压,而MAX5927是14V。如果12V供电电路采用了镜像电路电感,断路器过载时电路开路,使得12V电路可能出现供电电压振铃和过冲,那么这一电压优势就显得非常重要。接通时序

电阻R36 (在IC引脚10)将每一通道的接通时间设置为10.8ms ±2.8ms。在此期间,MAX5927A的内部低速比较器被禁止,使负载电容充电电流能够达到通道1至通道3每一通道预设电流触发值的两倍,以满足要求。在此期间,不需要触发断路器,负载电容很容易充电至最终值。在4kΩ和500kΩ之间调整R36,可以使启动延时设置在400µs (最小)到50ms (最大)之间的任意值。在这一启动时间的最后,STAT输出从FALSE至TRUE的瞬变。STAT输出为正,但也可以通过接地POL (引脚29)设置为负。通过(R29 + R30) - C16时间常数将通道1相对于通道2和通道3延时11.8ms接通;可以增大C16以加大延时。通道1开始接通10.8ms后,STAT1变为高电平。

通过(R29 + R31) - C17时间常数将通道4和通道5相对于通道2和通道3延时28ms接通;可以增大C17以加大延时,或者减小R31,以缩短延时。通道4和通道5开始接通10.8ms后,STAT4变为高电平。

MODE置位(开引脚28)以配置MAX5927A为上电排序模式。

输出电压摆率

所有通道输出电压摆率设置为约1V/ms,数值与负载电容(C11至C15)值无关。可以修改C6至C10栅极电容值以改变摆率。摆率计算为ΔV/Δt = IGATE/CGATE。由于计算中并没有包括FET栅极电容,因此,该方程并不是很精确。GATE1、GATE2和GATE3的栅极充电电流约为100µA。由于R10和R11电流的原因,Q4和Q5的栅极充电电流为30µA到50µA。负载电容充电电流可以计算为ICHARGE = CLOAD × ΔV/Δt。它由IGATE/CGATE = ICHARGE/CLOAD得出。电容C8至C10使通道1到通道3的输出达到约1V/ms摆幅。没有负载时,C13至C15以大约0.5A的电流充电,直到达到满幅输出。如果没有C8至C10,输出以两倍于上面计算电流触发值的电流对负载电容进行充电。电容C6和C7为10nF,使通道4和通道5的摆幅大约为1V/ms。断路器门限

21mV至27.5mV的慢速比较器阈值以及R7 = R9 = 8.3mΩ设置了通道1 (+3.3V)和通道3 (+12V)的限流值。默认值乘以1.13以及R33 = R35 = 1.15kΩ,得到大约3.1A至3.8A的最终值。21mV至27.5mV的慢速比较器阈值以及R8 = 10mΩ设置通道2 (+5V)限流值。默认值乘以1.15以及R34 = 1.18kΩ,得到大约2.415A至3.625A的最终值。通过调整检测电阻R7到R9以及ISET电阻R33到R35来设置其他的限流值。可以从数据资料提供的曲线中确定默认乘数。限流断路器不对低电流通道4 (-12V)和通道5 (-5V)提供保护。内部上拉把LATCH置为高电平,将MAX5927A配置为锁存故障管理。如果通道1至通道3中的任意一个出现故障,所有通道将被关断,直到低电平有效CARD_PRESENT进入下一关断和接通周期。

负电压通道4和通道5

MAX5927A设计用于控制正电压电路。然而,从MAX5927A的GATE4输出可以获得负电压通道Q4和Q5大约4.2V的栅极驱动,这一输出由晶体管Q5和Q6以及电阻R4–R7进行修改。GATE4的栅极充电电流输出是60µA至100µA,但是在对称电路R4–Q7和R5-Q6中被分成30µA至50µA。GATE4的电压可以比VIN4(3.3V)高5.3V,或者接通时≤+8.6V,关断时接近0V。接通时,VQ6(BASE) = VQ7(BASE) = 3.3V,VQ6(EMITTER) = VQ7(EMITTER) ≈ 3.9V,关断时为0V。R4和R5上相等的压降使得Q6和Q7均分电流。R6和R7上相等的电流在Q4和Q5上产生相等的栅极驱动。关断状态下,GATE4 = 0V时的栅极驱动为0V。Q4和Q5的关断速度取决于流过R6至R7的栅极放电电流。

FET选择

所有通道,除了+12V通道,采用了SOT23封装的n通道MOSFET直通晶体管;每一FET原理图列出了VGS = 4.5V和TJ = +25°C时的最大RDS(ON)。VGS(max) = 20V (Si9410)的MOSFET被用于+12V通道。总结

电路满足所有的负载和上电排序设计要求—处理3个正电压和2个负电压通道,具有合适的顺序接通时序、大于所需最小值的过电流触发点,以及大约1V/ms的输出摆率,达到了设计要求。+5V和+12V通道的+3.3V延时 = 11.8ms (请参考图2)

+3.3V通道的-5V延时 = 16.2ms (请参考图3)

-5V负载关断时间 = 1ms (请参考图4和图5)

-12V负载关断时间 = 4ns (请参考图6和图7)

-12V输出电压摆率 ≈ 1V/ms (请参考图8)

-12V负载电容充电电流 ≈ 80mA (请参考图9)

-5V输出电压摆率 ≈ 1V/ms (请参考图10)

-5V负载电容充电电流 ≈ 55mA (请参考图11)

+3.3V输出电压摆率 ≈ 1V/ms (请参考图12)

+3.3V负载电容充电电流 ≈ 400mA (请参考图12)

3A负载+3.3V接通,不触发断路器(请参考图13)

+3.3V断路器在3.22A时关断(请参考图14)

+5V负载电容充电电流 ≈ 500mA (请参考图15)

+5V输出电压摆率 ≈ 1V/ms (请参考图15)

2.4A负载+5V接通,不触发断路器(请参考图16)

+5V断路器在2.87A时关断(请参考图17)

+12V负载电容充电电流 ≈ 500mA (请参考图18)

3A负载+12V接通,不触发断路器(请参考图19)

+12V断路器在3.1A时关断(请参考图20)

+5V在 ≈ 4A时启动短路电路(请参考图21)

+12V在 ≈ 5.7A时启动短路电路(请参考图22)

测试结果

图2. +12V至+3.3V接通延时,没有负载

Ch1 = Q8BASE(CARD_PRESENT), Ch2 = +3.3VOUT, Ch3 = +12VOUT, Ch4 = -5VOUT

注释:+12VOUT和+3.3VOUT之间有11.8ms延时。

图3. +3.3V至-5V接通延时,没有负载

Ch1 = Q8BASE, Ch2 = +3.3VOUT, Ch3 = +12VOUT, Ch4 = -5VOUT

注释:+3.3VOUT和-5VOUT之间有16.2ms延时。

图4. -5V栅极相对于+3.3VGATE关断,没有负载

Ch1 = Q8BASE, Ch2 = +3.3VGATE, Ch3 = +5VGATE, Ch4 = -5VGATE

注释:-5V栅极关断较慢;当1 < VGATE < 3V (2.5V,典型值)时,FET关断。由此,正电压通道关断1.5ms至4ms后,-5V栅极完全关断。

图5. -5V负载关断,50mA负载

Ch1 = Q8BASE, Ch2 = -5VGATE, Ch3 = -5VOUT, Ch4 = IIN(-5V)

注释:虽然由于输出电容放电导致VOUT(-5V)没有达到0V,-5V在1ms内下降至零。

图6. -12V栅极关断,没有负载

Ch1 = Q8BASE, Ch2 = +3.3VGATE, Ch3 = +12VGATE, Ch4 = -12VGATE

注释:-12V栅极关断较慢;当1 < VGATE < 3V (2.5V,典型值)时,FET关断。由此,正电压通道关断1ms至4ms后,-12V栅极完全关断。

图7. -12V负载关断,150mA负载

Ch1 = Q8BASE, Ch2 = -12VGATE, Ch3 = -12VOUT, Ch4 = IIN(-12V)

注释:虽然由于输出电容放电导致VOUT(-12V)没有达到0V,-12V输入在4ms内降到零。

图8. -12V接通波形

Ch1 = Q8BASE, Ch2 = -12VGATE, Ch3 = -12VOUT, Ch4 = IIN(-12V)

注释:接通顺序,80Ω阻性负载 = 150mA。

图9. -12V接通波形,没有负载

Ch1 = Q8BASE, Ch2 = -12VGATE, Ch3 = -12VOUT, Ch4 = IIN(-12V)

注释:IIN(PK) = 80mA,对输出电容充电。

图10. -5V接通波形,100Ω阻性负载 = 50mA

Ch1 = Q8BASE, Ch2 = -5VGATE, Ch3 = -5VOUT, Ch4 = IIN(-5V)

注释:-5V摆率大约为1V/ms。

图11. -5V接通波形,没有负载

Ch1 = Q8BASE, Ch2 = -5VGATE, Ch3 = -5VOUT, Ch4 = IIN(-5V)

注释:IIN(PK) = 55mA,对输出电容充电。

图12. +3.3V接通波形,没有负载

Ch1 = Q8BASE, Ch2 = +3.3VGATE, Ch3 = +3.3VOUT, Ch4 = IIN(+3.3V)

注释:IIN(PK) = 400mA,对输出电容充电;+3.3V摆率大约为1V/ms。

图13. +3.3V接通波形,1.1Ω负载 = 3A

Ch1 = Q8BASE, Ch2 = +3.3VGATE, Ch3 = +3.3VOUT, Ch4 = IIN(+3.3V)

图14. +3.3V过流关断

Ch1 = STAT1, Ch2 = VGATE (+3.3V), Ch3 = +3.3VOUT, Ch4 = IOUT(+3.3V) 0.5A/div

注释:IOUT和VOUT减小是由于输出电容向恒阻负载放电。测得的触发电流为3.22A。*

图15. +5V接通负载电容充电电流,没有负载

Ch1 = Q8BASE, Ch2 = +5VGATE, Ch3 = +5VOUT, Ch4 = IIN(+5V)

注释:IIN(PK) = 500mA,对输出电容充电。

图16. +5V接通电流,2.083Ω负载 = 2.4A

Ch1 = Q8BASE, Ch2 = +5VGATE, Ch3 = +5VOUT, Ch4 = IIN(+5V)

图17. +5V过流关断

Ch1 = STAT2, Ch2 = VGATE (+5V), Ch3 = +5VOUT, Ch4 = IOUT(+5V) 0.5A/div

注释:IOUT和VOUT减小是由于输出电容向恒阻负载放电。测得的触发电流为2.87A。

图18. +12V启动电流,没有负载

Ch1 = Q8BASE, Ch2 = +12VGATE, Ch3 = +12VOUT, Ch4 = IIN(+12V)

注释:IIN(+12Vpk) = 500mA,对输出电容充电。

图19. +12V接通电流,4Ω负载 = 3A

Ch1 = Q8BASE, Ch2 = +12VGATE, Ch3 = +12VOUT, Ch4 = IIN(+12V)

图20. +12V过流关断

Ch1 = STAT3, Ch2 = VGATE (+12V), Ch3 = +12VOUT, Ch4 = IOUT(+3.3V) 0.5A/div

注释:IOUT和VOUT减小是由于输出电容向恒阻负载放电。测得的触发电流为3.1A。

图21. 短路电路的+5V启动电流

Ch1 = Q8BASE, Ch2 = +5VOUT, Ch3 = +5VGATE, Ch4 = IIN(+5V)

注释:触发时的4A负载电流。

图22. 短路电路的+12V启动电流

Ch1 = Q8BASE, Ch2 = VOUT, Ch3 = VGATE, Ch4 = IOUT

注释:触发时的5.7A负载电流。

测试PCB布板

更详细的图(PDF, 237kB)

图23. 参考设计PCB元件布局

更详细的图(PDF, 330kB)

图24. 顶层

图25. 底层

材料清单

| Qty | Designator | Description | Manufacturer and Part Number |

| 5 | C1, C2, C3, C4, C5 | 1µF ±10%, 25V X7R ceramic capacitors (0805) | — |

| 3 | C6, C7, C18 | 10nF ±10%, 25V X7R ceramic capacitors (0805) | — |

| 1 | C8 | 56nF ±10%, 25V X7R ceramic capacitor (0805) | — |

| 1 | C9 | 68nF ±10%, 25V X7R ceramic capacitor (0805) | — |

| 1 | C10 | 100nF ±10%, 25V X7R ceramic capacitor (0805) | — |

| 1 | C11 | 47µF ±20%, 6.3V X5R electrolytic capacitor (1210) | TDK C3225X5R0J476M |

| 1 | C12 | 100µF +80%, -20%; 16V Y5V ceramic capacitor (2220) | TDK C5750Y5V1C107Z |

| 3 | C13, C14, C15 | 470µF ±20%, 16V electrolytic capacitors | — |

| 1 | C16 | 15nF ±10%, 25V X7R ceramic capacitor (0805) | — |

| 1 | C17 | 33nF ±10%, 25V X7R ceramic capacitor (0805) | — |

| 2 | D1, D2 | 75V, 200mW silicon diodes (SOD-323) | Diodes Inc. MMBD4148WS |

| 2 | Q1, Q2 | 20V, 4.9A, 33mΩ n-channel MOSFETs (SOT23) | Vishay Si2314BDS |

| 1 | Q3 | 30V, 6.9A, 33mΩ n-channel MOSFET (8-SO) | Vishay Si9410BDY |

| 2 | Q4, Q5 | 30V, 4A, 47mΩ n-channel MOSFETs (SOT23) | Vishay Si2306BDS |

| 2 | Q6, Q7 | 60V, 800mA bipolar PNP transistors (SOT23) | Fairchild MMBT2907 |

| 1 | Q8 | 40V, 1A bipolar NPN transistor (SOT23) | Fairchild MMBT2222A |

| 10 | R1, R2, R3, R4, R5, R24, R25, R26, R27, R32 | 100kΩ ±5%, 1/16W thick-film resistors (0805) | — |

| 1 | R6 | 1Ω ±5%, 1/16W thick-film resistor (0805) | — |

| 2 | R7, R9 | 0.008Ω ±1%, 1/4W thick-film resistors (2512) | — |

| 1 | R8 | 0.010Ω ±1%, 1/4W thick-film resistor (2512) | — |

| 2 | R10, R11 | 90.9kΩ ±1%, 1/16W thick-film resistors (0805) | — |

| 2 | R12, R13 | 133kΩ ±1%, 1/16W thick-film resistors (0805) | — |

| 2 | R14, R15 | 15kΩ ±1%, 1/16W thick-film resistors (0805) | — |

| 3 | R16, R17, R18 | 4.7kΩ ±1%, 1/16W thick-film resistors (0603) | — |

| 5 | R19, R20, R21, R22, R23 | 10kΩ ±5%, 1/16W thick-film resistors (0805) | — |

| 1 | R28 | 20kΩ ±5%, 1/16W thick-film resistor (0805) | — |

| 2 | R29, R36 | 100kΩ ±1%, 1/16W thick-film resistors (0805) | — |

| 2 | R30, R31 | 910kΩ ±1%, 1/16W thick-film resistors (0805) | — |

| 2 | R33, R35 | 1.15kΩ ±1%, 1/16W thick-film resistors (0805) | — |

| 1 | R34 | 1.18kΩ ±1%, 1/16W thick-film resistor (0805) | — |

| 1 | U1 | Quad hot-swap controller IC, 32-TQFN-EP | Maxim MAX5927AETJ |

*注意,图14、图17和图20使用了特殊的电流探针,只显示了真值的72%。使用可调恒流负载测量断路器电流,标出了关断时的点。

电子发烧友App

电子发烧友App

评论