布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在高速 PCB 设计中

2015-01-12 14:53:57

下面从直角走线、差分走线、蛇形线三个方面来阐述PCB LAYOUT的走线。

2021-03-17 07:25:46

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在高速 PCB 设计中

2019-06-10 10:11:23

的设计理论也要最终经过 Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。主要从直角走线,差分走线

2017-07-07 11:45:56

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-05-23 08:52:37

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2014-08-13 15:44:05

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-08-05 06:40:24

打孔换层,换层优先选择两边是GND的层面处理。尽量收发信号布线在不同层,如果空间有限,需收发信号走线同层时,应加大收发信号之间的布线距离。

针对以上高速信号还有如下方面的要求:

一、BGA焊盘区域挖

2023-08-01 18:02:03

:认为保持等间距比匹配线长更重要。在实际的PCB布线中,往往不能同时满足差分设计的要求。由于管脚分布,过孔,以及走线空间等因素存在,必须通过适当的绕线才能达到线长匹配的目的,但带来的结果必然是差分对的部分

2019-08-21 07:30:00

PCB布线的直角走线、差分走线和蛇形线基础理论

2015-05-21 11:48:54

PCB布线这几种走线方式,你会吗?在我们学习嵌入式开发的过程中,PCB布线是必不可少的。好的布线方式,轻则看着美观、布局合理,重则可以节约生产成本,达到良好的电路性能和散热性能,使元器件的性能达到

2020-02-28 10:50:28

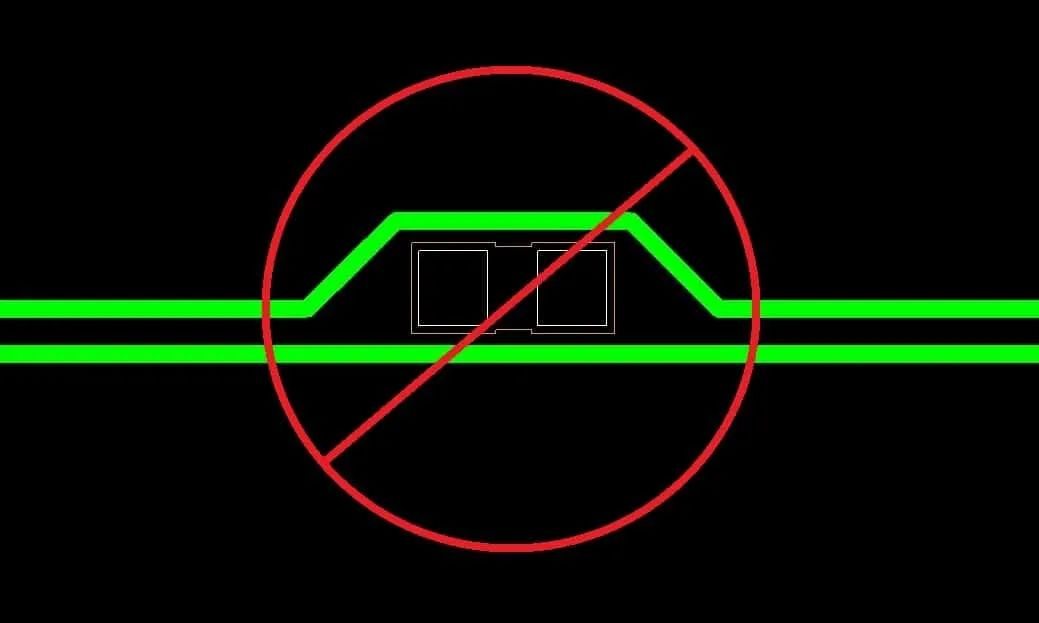

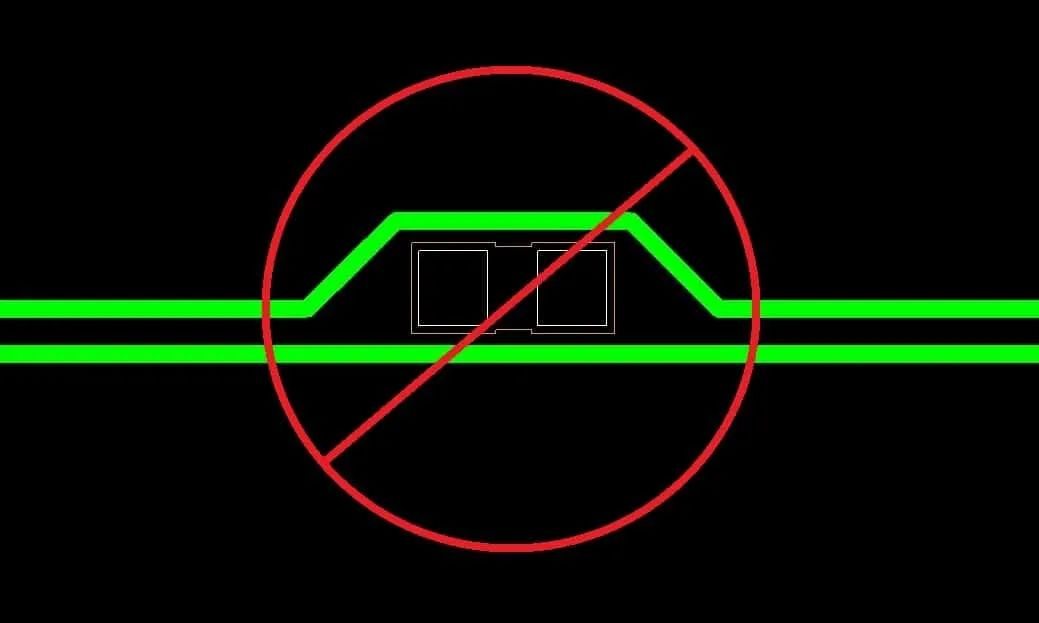

线角度 直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢? 从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续

2019-08-20 15:27:06

的线宽间距,并设置到约束管理器。 差分线通过互相耦合来减少共模干扰,在条件许可的情况下要尽可能平行布线,两根线中线不能有过孔或其他信号。 差分对需要严格控制相位,所以对内需要严格控制等长。 为减少

2023-04-12 15:08:27

的地环。以避免从大地受到干扰噪声. USB方面的考虑 USB的差分信号线保持平行走线,以达到90 ohm的差分阻抗。由于PCB和走线的因素这样的平行走线的要求是很难达到的。为了避免这样的偏差尽可能

2023-04-13 16:09:54

夹杂在差分信号之间的非查份(单独一条)走线方式有什么要求吗?这就是要画的连接线PCB高速差分信号线四层怎么弄,还要求阻抗,就是一个连接线

2023-04-07 17:46:45

经过 Layout 得以实现并验证,由此可见,布线在高速 PCB 设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。主要从直角走线,差分走线,蛇形线

2017-09-03 13:25:35

过孔走线和层数(1)过孔采用通孔设计中,5个BGA焊盘球需要三层进行出线,因布线不能在贯通孔下面通过,第一个和第二个焊盘球可以表层出线,第三个和第四个焊盘球要通过孔换到第二个层中出线,第五个焊盘球

2020-07-06 15:58:12

可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。 主要从直角走线,差分走线,蛇形线等三个方面来阐述。 1. 直角走线 直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量

2018-09-17 17:31:52

1.1 PCB板上预划分数字、模拟、DAA信号布线区域。1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。1.3 高速数字信号走线尽量短。1.4 敏感模拟信号走线尽量短。1.5

2019-05-30 06:58:19

在pcb上靠近平行走高速差分信号线对的时候,在阻抗匹配的情况下,由于两线的相互耦合,会带来很多好处。但是有观点认为这样会增大信号的衰减,影响传输距离,为什么?我在一些大公司的评估板上看到高速布线有的

2012-03-03 12:37:52

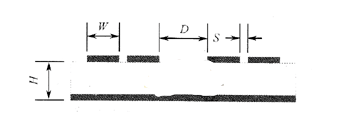

、差分布线方式是如何实现的?差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两种,一为两条线走在同一走线层

2012-08-05 19:33:41

(topology)架构等。解决的方式是靠端接(termination)与调整走线的拓朴。4、差分布线方式是如何实现的?差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗

2015-12-16 16:40:24

(output impedance),走线的特性阻抗,负载端的特性,走线的拓朴(topology)架构等解决的方式是靠端接(termination)与调整走线的拓朴4、差分布线方式是如何实现的?差分对的布线有

2015-10-30 15:25:15

(termination)与调整走线的拓朴。4、差分布线方式是如何实现的?差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两种

2017-07-07 13:03:12

分布线方式是如何实现的? 差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两 种,一为两条线走在同一走线层

2015-01-09 11:14:05

线的拓朴(topology)架构等。解决的方式是靠端接(termination)与调整走线的拓朴。 4、实现差分布线方式 差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距

2018-11-28 11:35:36

(termination)与调整走线的拓朴。4、差分布线方式是如何实现的?差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持

2016-09-12 14:53:53

)与调整走线的拓朴。4、差分布线方式是如何实现的?差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两种,一为

2021-09-19 14:47:06

方式是如何实现的?差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两种,一为两条线走在同一走线层

2011-03-17 10:05:21

1. 一般规则1.1 PCB板上预划分数字、模拟、DAA信号布线区域。1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。1.3 高速数字信号走线尽量短。1.4 敏感模拟信号走线尽量

2014-03-14 17:44:44

很多冲突。 但基本原则是因EMI所加的电阻电容或ferrite bead, 不能造成信号的一些电气特性不符合规范。 所以, 最好先用安排走线和PCB叠层的技 巧来解决或减少EMI的问题, 如高速信号走

2012-12-17 12:29:48

,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。 高速数字PCB板的等线长是为了使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读

2019-05-22 02:48:05

(output impedance),走线的特性阻抗,负载端的特性,走线的拓朴(topology)架构等。解决的方式是靠端接(termination)与调整走线的拓朴。 差分对的布线有两点要注意,一是两条线的长度

2012-09-28 11:15:18

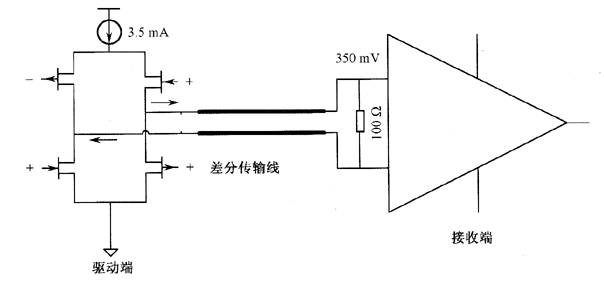

为了避免不理想返回路径的影响,可以采用差分对走线。为了获得较好的信号完整性,可以选用差分对来对高速信号进行走线,如图1所示,LVDS电平的传输就采用差分传输线的方式。 图1 差分对走线实例

2018-11-27 10:56:15

信号的特性阻抗连续规则高速信号,在层与层之间切换的时候必须保证特性阻抗的连续,否则会增加EMI的辐射。也就是说,同层的布线的宽度必须连续,不同层的走线阻抗必须连续。规则五、高速PCB设计的布线方向规则

2021-03-31 06:00:00

,不同层的走线阻抗必须连续。规则五、高速PCB设计的布线方向规则 相邻两层间的走线必须遵循垂直走线的原则,否则会造成线间的串扰,增加EMI辐射。 简而言之,相邻的布线层遵循横平竖垂的布线方向,垂直的布线可以

2022-04-18 15:22:08

管脚分布,过孔,以及走线空间等因素存在,必须通过适当的绕线才能达到线长匹配的目的,但带来的结果必然是差分对的部分区域无法平行,这时候我们该如何取舍呢?在下结论之前我们先看看下面一个仿真结果。 从上

2012-12-18 12:03:00

管脚分布,过孔,以及走线空间等因素存在,必须通过适当的绕线才能达到线长匹配的目的,但带来的结果必然是差分对的部分区域无法平行,这时候我们该如何取舍呢?在下结论之前我们先看看下面一个仿真结果。从上

2012-12-19 16:52:38

一系列阻抗问题。 高速设计的另一个关键领域是差分对的布线。差分对通过以互补的方式驱动两个信号迹线来操作。差分对提供出色的抗噪声能力和更高的S / N比。然而,实现这些优势有两个限制: 1、两条走线

2023-04-12 15:20:37

,工程师应该尽可能地用最少层数满足实际设计需要,从而致使布线密度不可避免地增大,而在PCB布线设计中,其走线宽度越细,间隔越小,信号间串扰就越大,其能传送功率越小。因此,走线尺寸的选择必须考虑到各方面

2018-11-27 09:57:50

影响各自的特性阻抗, 变的较小, 根据分压原理(voltage divider)这会使信号源送到线上的电压小一点。 至于, 因耦合而使信号衰减的理论分析我并没有看过, 所以我无法评论。 对差分对的布线方式

2012-08-15 20:35:17

在未布板之前,先将高速USB主控制器和一些相关的主要器件摆放好。尽可能缩短走线长度,优先考虑对高速时钟信号和高速USB差分线的布线,尽可能的避免高速时钟信号与高速USB差分线和任何的接插件靠近走线

2019-05-30 07:36:38

PCI-Clk,AGPCIK,IDE,DIMM等信号线。(2)若在一般普通PCB板中,除了具有滤波电感的作用外,还可作为收音机天线的电感线圈等等。如2.4G的对讲机中就用作电感。(3)对一些信号布线长度要求

2019-03-22 06:20:09

高速中的蛇形走线,适合在那种情况?有什么缺点没,比如对于差分走线,又要求两组信号是正交的。回答:”蛇形走线,因为应用场合不同而具不同的作用:(1)如果蛇形走线在计算机板中出现,其主要起到一个滤波电感

2019-05-09 07:35:35

我的AD9446的工作在LVDS模式下,请问对于AD9446(100MHz),LVDS信号线的PCB走线的差分对间等长有没有要求?(PS:16对差分线,都做等长好复杂)谢谢!

2023-12-18 06:26:51

请问,pcb中已经布完差分对后,发现有部分差分对需要调整线宽和线间距,现在只知道修改RULES,然后重新走一遍布线,相当于重新布线了,量大很麻烦。有没有便捷的方法呢?

2016-08-03 14:50:36

我看别人的板子差分对走线之间的过孔距离很宽,而我的这个差分对走线过孔离得很近,这个之间的规则是怎么设置的啊?没找到呢,。。

2018-08-13 10:42:05

如何在 Altium Designer 6 中快速进行差分对走线1: 在原理图中让一对网络前缀相同,后缀分别为_N 和_P,并且加上差分队对指示。在原理图中,让一对网络名称的前缀名相同,后缀分别为

2019-07-10 08:38:05

PCB布线中,有着许多需要注意的点,比如:1.高频时钟线需要蛇形走线2.有些信号线需要设置差分对,差分走线

2019-05-31 06:23:05

来说,最关注的是如何确保在实际走线中能完全发挥差分线的这些优势。(1)定义差分对信号:在Router中,同时选定需要走差分线的网络(Net),右击后选择Make Differential Net,如下

2015-01-12 15:38:59

,布线在高速PCB设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。主要从直角走线,差分走线,蛇形线等三个方面来阐述。1. 直角走线直角走线一般

2010-03-16 09:23:41

为了保证良好的信号质量, USB 2.0 端口数据信号线按照差分线方式走线。为了达到USB 2.0 高速 480MHz 的速度要求,建议 PCB 布线设计采用以下原则:差分数据线走线尽可能短、直,差分数据线对内走线长度严格等长,走线长度偏差控制在±5mil 以内。

2019-05-23 08:52:33

(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在高速 PCB 设计中是至关重要

2009-05-31 10:08:49

,布线在高速PCB设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。主要从直角走线,差分走线,蛇形线等三个方面来阐述。

2009-08-20 20:58:49

是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。主要从直角走线,差分走线,蛇形线等三个方面来阐述。01直角走线直角走线一般是PCB布线中要求尽量避免

2018-07-08 13:28:36

;提取未布线差分对拓扑的优先设置 8.6 提取差分对拓扑 8.7 差分对拓扑分析的激励定制 8.8 差分对拓扑分析 8.9 耦合线

2009-07-10 13:14:18

现在学习cadence,PCB布线时,感觉命令不听使唤,总是绕的乱不七八糟,但是取消差分对采单个模式又担心达不到效果,求有经验的前辈说说看

2015-12-28 22:38:54

还不够深入。 误区二:认为保持等间距比匹配线长更重要。在实际的PCB布线中,往往不能同时满足差分设计的要求。由于管脚分布,过孔,以及走线空间等因素存在,必须通过适当的绕线才能达到线长匹配的目的,但

2018-09-21 11:53:08

的拓朴(topology)架构等。解决的方式是靠端接(termination)与调整走线的拓朴。 4、差分布线方式是如何实现的? 差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线

2018-09-12 20:53:55

打孔换层,换层优先选择两边是GND的层面处理。尽量收发信号布线在不同层,如果空间有限,需收发信号走线同层时,应加大收发信号之间的布线距离。

针对以上高速信号还有如下方面的要求:

01

BGA焊盘区域挖

2023-08-03 18:18:07

阻抗连续,否则在传输线各段之间也将会出现反射。这就要求在进行高速PCB布线时,必须要遵守以下布线规则: (1)LVDS布线规则。要求LVDS信号差分走线,线宽7mil,线距6mil,目的是控制HDMI

2017-01-20 11:44:22

:认为保持等间距比匹配线长更重要。在实际的PCB布线中,往往不能同时满足差分设计的要求。由于管脚分布,过孔,以及走线空间等因素存在,必须通过适当的绕线才能达到线长匹配的目的,但带来的结果必然是差分对的部分

2019-03-18 21:38:12

新人,第一次用allegro,在pcb editor里布线,设置了差分对规则,返回布线的时候,选中差分对其中的一个引脚布线,但是只拉出来了一根线,右键里也没有单根走线模式可选。求解。。。。。。

2015-04-15 17:38:54

(termination)与调整走线的拓朴。 4、差分布线方式是如何实现的? 差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行

2019-09-06 18:54:23

, 是否有足够的约束条件控制蛇行线(serpentine)蜿蜒的方式, 能否控制差分对的走线间距等。 这会影响到自动布线出来的走线方式是否能符合设计者的想法。 另外, 手动调整布线的难易也与绕线引擎的能力

2009-03-20 14:07:39

大神手把手教你如何进行pcb高速线布线

2021-05-13 06:22:15

开关电源PCB布线原则及走线技巧

2019-03-06 11:43:16

怎样计算PCB布线中走线允许的最大长度?走线太长了都有哪些影响呢?

2023-04-10 17:10:25

在PCB设计中,布线是完成产品设计的重要步骤,PCB走线的好坏直接影响整个系统的性能,布线在高速PCB设计中是至关重要的。布线的设计过程限定高,技巧细、工作量大。PCB布线有单面布线、 双面布线

2014-12-16 09:47:09

,那我们就要知道哪些线是需要走差分形式的,然后我们就要对这些线进行差分对的定义,这样软件才能识别。添加差分属性一般有两种方式,一种手动,一种自动。先介绍下手动添加方式。首先,我们在PCB状态栏点击ADD

2018-01-12 17:09:48

T.K. Chin在他的博客文章《差分对:你真正需要了解的内容》里谈论了对于差分对的要求。在现实应用中,我们用印刷电路板(PCB)内的铜走线或线缆组装件内的铜质导线来实现差分对。较长的PCB走线或

2018-09-04 14:25:47

的要求一个良好设计差分对是成功进行高速数据传输的关键因素。根据应用的不同,差分对可以是一对印刷电路板 (PCB) 走线,一对双绞线或一对共用绝缘和屏蔽的并行线(通常称为Twin-axial电缆)。在这

2018-09-11 11:50:09

也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。主要从直角走线,差分走线,蛇形线

2012-07-21 14:22:45

的连续,否则会增加EMI的辐射。也就是说,同层的布线的宽度必须连续,不同层的走线阻抗必须连续。 图4 特性阻抗连续规则 规则五:高速PCB设计的布线方向规则 相邻两层间的走线必须遵循垂直走线的原则

2018-09-20 10:38:01

线的拓朴。 4、差分布线方式是如何实现的? 差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两种,一为

2018-11-27 10:00:59

@我的AD9446的工作在LVDS模式下,请问对于AD9446(100MHz),LVDS信号线的PCB走线的差分对的对间等长有没有要求?(PS:16对差分线,都做等长好复杂)谢谢!

2018-09-19 09:47:36

HDMI差分对PCB怎么走线?要计算匹配阻抗吗?差分对走多长有要求吗?四对差分对要走一样长吗?

2019-05-31 05:35:21

,最好先用安排走线和PCB迭层的技巧来解决或减少EMI的问题,如高速信号走内层。最后才用电阻电容或 ferrite bead 的方式, 以降低对信号的伤害。9.如何解决高速信号的手工布线和自动布线之间

2018-08-14 15:41:11

在高速 PCB 设计中,差分信号(DIFferential Signal)的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。为什么这样呢?和普通的单端信号走线相比,差分信号有抗干扰能力强

2020-09-29 09:12:19

在高速 PCB 设计中,差分信号(DIFferential Signal)的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。为什么这样呢?和普通的单端信号走线相比,差分信号有抗干扰能力强

2022-06-07 14:26:13

,即交越点。因此,信号须同时到达接收器才能正常工作。差分对内的走线布线须彼此靠近,如果一对中的相邻线路之间的距离大于电介质厚度的2倍,则其间的耦合会很小。此规则也是基于差分信号相等但相反这一事实,如果

2018-12-27 11:30:22

的? 差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两种,一为两条线走在同一走线层

2018-09-21 16:26:48

规范。 所以,最好先用安排走线和PCB迭层的技巧来解决或减少EMI的问题,如高速信号走内层。最后才用电阻电容或 ferrite bead 的方式, 以降低对信号的伤害。9.如何解决高速信号的手工布线

2019-09-28 08:00:00

)与调整走线的拓朴。4、差分布线方式是如何实现的?差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两种,一为

2017-01-20 10:29:29

高效差分对布线指南:提高 PCB 布线速度

2023-11-29 16:00:52 690

690

电子发烧友App

电子发烧友App

评论