故事是这样子的:这是某电力产品的一个真实案例:一批电计量产品存在仓库没上线,刚好南方天湿气重PCB上凝露,出现大量32768停振情况。所以今天我们要跟大家分享的就是32768晶振,后面我们还会提到几个相关的案例和注意事项。1一张图看尽石英晶振家族 图片中已经对Tuning ...

2021-07-27 08:08:24

我发现PCB板上有很多32.768的插件晶振,PCB板上不是插件封装而是贴片封装,直接将插件晶振焊到PCB表面,为什么要这样设计?也有选择插到板子上的,但有很多板子是选择贴片封装,这样有什么好处?哪位大神解答一下,不胜感激

2016-07-23 10:40:05

在电子产品设计中,PCB 布局布线是最重要的一步,PCB 布局布线的好坏将直接影响电路的性能。随着信号频率不断提升,很多时候,工程师需要了解有关 PCB 布局布线的最基本的原则和技巧,这样才可以让

2014-11-18 10:01:25

MCU时钟往往外接晶振、电容,有的会并一个1M电阻,PCB布局时怎么布局好?MCU出来是先晶振后电容好还是先电容后晶振好?还有1M的电阻放那个位置比较好?布线应该注意什么?

2019-09-29 03:47:29

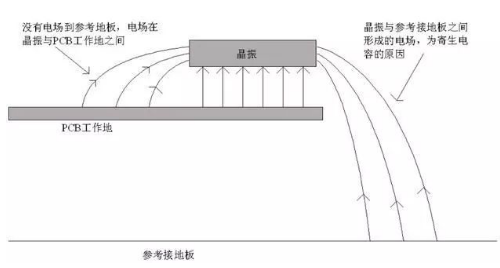

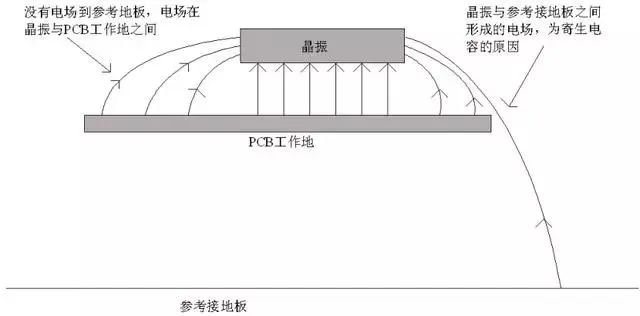

时电场分布如下:PCB 边缘的晶振与参考接地板之间的电场分布示意图PCB 中间的晶振与参考接地板之间的电场分布示意图从图中可以看出,当晶振布置在 PCB 中间,或离 PCB 边缘较远时,由于 PCB

2020-04-21 07:00:00

元器件为中心,围绕他来进行布局。元器件应均匀、整体、紧凑的排列在PCB上,尽量减少和缩短各元器件之间的引线和连接。 对于大多数PCB初学者来说,了解和掌握PCB的布局原则和规则是非常重要的,本文只是

2019-08-20 04:36:05

晶振选择和电路板设计 晶振的选择和PCB板布局会对VCXO CLK发生器的性能参数产生一定的影响。选择晶体时,除了频率、封装、精度和工作温度范围,在VCXO应用中还应注意等效串联电阻和负载电容

2018-09-13 16:09:28

晶振设计指导手册,ENHANCED GUIDELINES TO IMPLEMENT 19.2 MHZ CRYSTAL FOR SMALL PCB-HIGH THERMAL LAYOUTS。通过晶振 PCB 设计初步了解 高频信号的设计基础。

2023-09-20 06:37:54

晶振,在板子上看上去一个不起眼的小器件,但是在数字电路里,就像是整个电路的心脏。数字电路的所有工作都离不开时钟,晶振的好坏,晶振电路设计的好坏,会影响到整个系统的稳定性。所以更多的了解晶振,选择好

2015-01-26 15:29:22

使用匹配的电容晶振不起振,换电容起振,再换回原来的不起振的电容,晶振起振了,这是什么原因?哪位高手可以指点 谢谢。

2017-07-14 15:23:22

工程师工作效率,助力大家更快更轻松地开发新产品,华秋电子联合扬兴科技开启直播,为大家带来“硬件工程师必备的晶振干货”。相信硬件工程师会遇到以下烦恼:焊好的板子,电路怎么都调试不出来;板子上的晶振布局不合理;特殊晶

2022-07-19 11:53:11

` 本帖最后由 azsxdcfv1871514 于 2013-1-6 14:55 编辑

遇到单片机晶振不起振是常见现象,那么引起晶振不起振的原因有哪些呢?(1) PCB板布线错误;(2

2012-06-10 19:56:26

晶振不起振问题归纳晶振其他不良问题归纳晶振设计过程中的建议

2021-03-03 06:44:24

振荡电路对晶振输出的激励电平。一般而言,激励电平越小越好,处理功耗低之外,还跟振荡电路的稳定性和晶振的使用寿命有关。4、 晶振内部水晶片上附有杂质或者尘埃等也会导致晶振不起振晶振的制程之一是水晶片镀

2019-07-16 04:20:09

什么是晶振晶振与单片机周期单片机晶振的作用指令周期晶振与晶体的区别

2021-03-04 07:00:10

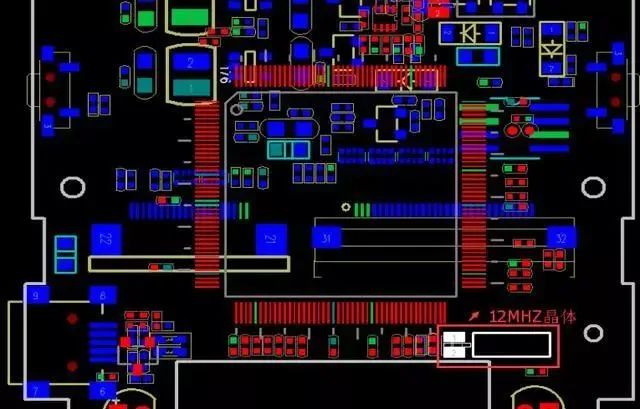

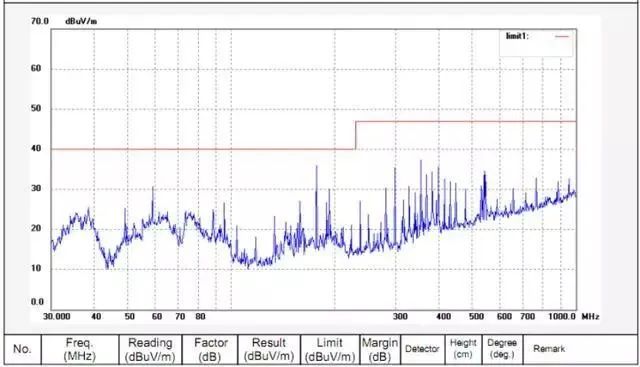

,其上有一个频率为16MHz的晶振。由此可见,160MHz的辐射应该与该晶振有关(注意:并不是说辐射超标是晶振直接辐射造成的,可能是倍频产生的)。图1所示的是该产品局部PCB布局实图,从图1中可以明显

2020-12-25 15:02:07

短小的风潮导致晶振尺寸日趋微型化。但小型化的结果直接抬高了产品的价格,选择晶振时往往需要在小型化和价格之间做出取舍。“设计者在选择晶振外形、尺寸上不应盲目追求越小越好,而应根据电路板的具体情况合理选择

2017-06-29 14:26:49

我有一块STM32U575的板子,没焊外部高速晶振,本来上面标着16兆晶振,四个脚的,我在淘宝上买了一些32M的晶振。

淘宝上写着匹配晶振8pF,我忘买了,搞了两个4.7pF的晶振,用STM32CubeMX生成代码,就是让一个灯闪。

可是灯一直不闪。我想会不会是匹配晶振的原因。请高手指教,谢谢!

2023-06-02 16:42:20

体积较大,但现在许多有源晶振是表贴的,体积和晶体相当,有的甚至比许多晶体还要小。几点注意事项:1、需要倍频的DSP需要配置好PLL周边配置电路,主要是隔离和滤波;2、20MHz以下的晶体晶振基本上都是

2010-01-20 21:46:05

体积较大,但现在许多有源晶振是表贴的,体积和晶体相当,有的甚至比许多晶体还要小。几点注意事项:1、需要倍频的DSP需要配置好PLL周边配置电路,主要是隔离和滤波;2、20MHz以下的晶体晶振基本上都是

2010-01-20 21:48:08

晶振,电子元器件产品的一种,晶振体积超小型薄型,高性能,低耗电,是电子产品的最佳搭档。 通常电子工程师在设计PCB的时候,一般先是按照自己的想法来设计,到PCB板成型只差晶振时,才会叫采购

2013-11-14 15:49:03

线外围成一圈用于屏蔽干扰的导线环, 一般要求理论上没有电流从该导线环上经过)下直接敷地有助于将晶振和来自其他PCB 层的噪声隔离开来。要注意接地平面要紧临晶振但只限于晶振下面, 而不要将此接地平面敷满

2022-04-14 14:32:45

方法使得对一个计时器进行编程,令其每秒发作60次接连成为可能。晶振是指从一块石英晶体上按一定方位角切下薄片,石英晶体谐振器,简称为石英晶体或晶体、晶振;而在封装内部添加IC组成振荡电路的晶体元件称为

2017-07-13 15:02:58

一、简介晶振是数字电路的心脏,就是因为所有的数字电路都需要一个频率高度稳定的工作时钟信号,为电路的工作提供时序基准,使各个模块的工作能够有条不紊的进行下去。而LC振荡器稳定性较差,频率容易漂移(即

2022-02-14 06:11:34

的分立RC振荡器。基于晶振与陶瓷谐振槽路的振荡器通常能提供非常高的初始精度和较低的温度系数。RC振荡器能够快速启动,成本也比较低,但通常在整个温度和工作电源电压范围内精度较差,会在标称输出频率的5%至

2015-01-27 15:28:28

与CO为2pf,CPCB=4pF可以得出CL1为6.8pf.左右注意:CPCB,CS 在不同的芯片,不同的PCB布局当中是不同的,因此在计算当中我做了修改,在实际的运用当中,我们贴片式晶振中电容一般选

2021-08-12 08:27:58

` 本帖最后由 music_mc 于 2016-3-25 00:07 编辑

电路如下图,STC单片机,上电晶振不起振用线把晶振任意一脚跟GND短接就能起振,或者用手摸摸晶振引脚也能起振,但关掉重新上电,又不能了,真晕无源晶振 22.1184mhz`

2016-03-24 21:00:56

晶振的作用是给机器提供一个时钟信号,晶振通过频率发生器的放大或缩小后就成了电脑中各种不同的总线频率。计算机都有个计时电路,虽然叫做“时钟”,但它们实际上并不是通常意义的时钟,把它们称为计时器更恰当

2018-07-13 09:33:02

的距离相当的接近,在这个极窄的频率范围内,晶振等效为一个电感,所以只要晶振的两端并联上合适的电容它就会组成并联谐振电路。这个并联谐振电路加到一个负反馈电路中就可以构成正弦波振荡电路,由于晶振等效为电感

2014-12-25 15:12:28

频率高,干扰谐波能量强;干扰谐波除了从其输入与输出两条走线传导出来,还会从空间辐射出来,若布局不合理,容易造成很强的杂讯辐射问题,而且很难通过其他方法来解决,因此在PCB 板布局时对晶振和CLK 信号线

2018-09-19 16:31:11

[^) n0 f1 v/ y0 I分析:1.晶振的布局不合理,电容的位置需要调整9 K6 |d, QB$ ]9 \2.布线的线宽不一致3.晶振的布线没有以类似差分形式布线,分散太开了,且其中的一信

2014-10-20 16:05:14

和晶振的使用寿命有关。 4、晶振内部水晶片上附有杂质或者尘埃等也会导致晶振不起振 晶振的制程之一是水晶片镀电极,即在水晶片上镀上一次层金或者银电极,这要求在万级无尘车间作业完成。如果空气中的尘埃

2020-10-21 06:42:08

、温度范围、输出电压、功率、输出波形、封装尺寸和外形。PCB布线位置:晶振容易损坏,所以要原理板边,靠近MCU。耦合电容:耦合电容应尽量靠近晶振的电源引脚。如果多个电容耦合,要按照电流流入的方向,依次容值从大到小摆放。走线:高速时钟信号线优先级最高。一般在布线时,需要优先考虑主时钟信号线。时钟线信

2022-02-11 08:02:03

源晶振要好。XAL1就是一个两脚的无源晶振,11.0592MHZ振荡频率,匹配电容是两个30P的瓷片电容。每种芯片的手册上都会提供外部晶振输入的标准电路,会表明芯片的最高可使用频率等参数,在设计电路

2012-10-16 13:26:21

:晶振的负载电容=[(Cd*Cg)/(Cd Cg)] Cic △C式中Cd,Cg为分别接在晶振的两个脚上和对地的电容,Cic(集成电路内部电容) △C(PCB上电容)一般为3至5pf. 所以我们在采购

2016-05-18 20:38:27

产品做EMC测试时辐射超标,44MHz和88MHz,应该是使用的22.1184MHz无源晶振辐射导致的,除了优化PCB外另外考虑晶振本身的辐射特性,不知道在相同条件下无源晶振辐射小 还是有源晶振辐射更小?望有类似经验的朋友不吝赐教。

2019-05-05 17:51:36

`大家好,想听听大家如何看待如何避免晶振的谐波辐射问题(晶振布局位置、芯片供电电压、电缆长度)?`

2015-08-22 23:41:00

只能采用整体的晶振隔振器(座)形式,其弹性阻尼特性及结构示意图如左图所示,晶振一次隔振系统试验示意图见下图 晶振隔振器主要由以下部分组成?①上支板,与晶振相连:②下支板,与基板或频综器相连;③可调

2015-01-08 09:18:00

给芯片上电后,各电源引脚电压正常,用示波器看不到晶振引脚的波形。晶振两个引脚都是大约0.8V电压,SYNC_CLK也看不到波形。晶振用的是25M无源晶振并两个39pF电容。请教各位这是什么原因呢?不胜感激。

2018-11-08 09:52:09

://www.eepw.com.cn/article/201706/360796.htm IC在运行中,各微型元器件工作时,肯定要分先后顺序。晶振和IC都是通过PCB板铜线相连的,PCB就像是马路一样,汽车

2017-06-22 11:29:41

时,肯定要分先后顺序。晶振和IC都是通过PCB板铜线相连的,PCB就像是马路一样,汽车都是运行的电流或者电压,而红路灯就是指挥交流安全的,红路灯工作职能就像晶振一样。为什么IC旁边总有晶振的身影?扬兴

2017-06-13 16:10:32

晶振与晶体的区别是什么?MEMS硅晶振与石英晶振区别是什么?晶振与晶体的参数有哪些?

2021-06-08 07:03:42

`MSP430晶振布局要领`

2013-05-17 21:36:03

在学习设计过程中,有一些地方不怎么明白,网上搜到的答案不满意,希望有经验的人给予指导。在STM32F103C8T6的数据手册中,低速外部时钟32.678khz的晶振。手册上写到:CL1和CL2,建议

2017-06-05 15:02:25

STM32外部晶振和内部晶振切换以前做STM32的项目都是移植的正点原子官方的Demo,晶振是默认使用外部晶振8MHz,倍频到72MHz来实际运用的,实际上大家为了麻烦也都是用的这种方法。最近有几个

2021-08-10 06:25:22

PLL周边配置电路,主要是隔离和滤波;2、20MHz以下的晶体晶振基本上都是基频的器件,稳定度好,20MHz以上的大多是谐波的(如3次谐波、5次谐波等等),稳定度差,因此强烈建议使用低频的器件,毕竟倍频

2010-01-20 21:45:40

我们为什么做这场直播?作为硬件工程师中的一员,你是不是遇到这些烦恼:焊好的板子,电路死活调试不出来;板子上的晶振布局不合理;特殊晶振料交期慢,开发的产品进度一直催等等......那如何解决这些

2022-07-08 14:30:53

振荡电路对晶振输出的激励电平。一般而言,激励电平越小越好,处理功耗低之外,还跟振荡电路的稳定性和晶振的使用寿命有关。4、 晶振内部水晶片上附有杂质或者尘埃等也会导致晶振不起振晶振的制程之一是水晶片镀

2017-10-25 15:09:17

不用 32.768晶振 用外部32M晶振怎么改寄存器???RTC 不需要低功耗???怎么改???我需要实时时钟但是板子上没32.768K晶振 只有外部32M晶振 怎么改程序啊??? 你们教我一下改

2022-09-27 07:03:48

`主板上晶振主要分为时钟晶振:与时钟芯相连 频率为14.318MHz 工作电压为1.1--1.6V实时晶振:与南桥相连 频率为32.768MHz 工作电压为0.4V左右声卡晶振:与志卡芯片相连

2013-03-21 14:59:58

就非常重要了。主板上的晶振如何检测?下面扬兴简单的介绍下检测晶振两种的方法:使用万用表测量晶振电阻和电压,根据测量数值能快速有效的判断晶振的好坏。最常用的方法就是万用表,所有电子元器件基本都是用万用表来测量该

2017-07-03 15:00:46

本帖最后由 yundishangwu183 于 2013-5-13 11:02 编辑

了解晶振知识就上 (上上电子网) QQ:1833283916晶体振荡器也分为无源晶振和有源晶振两种类型。无

2013-05-13 10:47:28

。每种晶振使用都有着不同之处,普通石英晶振,通常都是使用在一般的电器产品上,如电脑周边的电子数码产品,基本上都需要使用石英晶振,陶瓷晶振,32.768K表晶系列,就好比千赫晶体,32.768K通常是在

2012-12-10 14:02:58

可由两个极限温度的频差可算出最小温度频飘可以做到20PPM,这个数值越小,相对的该产品质量也越好,当然在成本上也是高了很多的。工业级晶振与普通民用级晶振比有什么区别呢? 与民用级晶振相比,工业级晶振在

2016-08-04 15:15:00

)。 2、针对采购32.768K晶振,我们需要掌握晶振的精度、型号(或体积)。如果型号是贴片晶振,就不需要问脚位了,只需要掌握晶振的负载和精度就可以了。因为从型号可以看出晶振的体积,晶振属于什么表面封装

2014-02-27 16:16:35

的稳定性。

五、晶体晶振的PCB可制造性检查

在PCB布局和布线设计完成后,为确保顺利制造并避免潜在的可制造性问题,进行可制造性检查是至关重要的一步。特别是对于晶体和晶振的PCB设计,应对线宽、线距、孔

2024-01-04 11:54:47

,美得冒泡的饶萧萧打来电话,告诉毛毛说有个无源的晶振物料有问题,装配不进孔里去。

还给毛毛发了个图片。

毛毛一看图片,就感觉两眼发懵,这……

PCB上阻焊没开窗,孔内塞了绿油,导致插件孔无法插件

2023-07-31 14:29:38

包括晶振的选型,匹配电容的计算还有PCB布局

2016-08-12 14:29:48

遇到单片机晶振不起振是常见现象,那么引起晶振不起振的原因有哪些呢?(1) PCB板布线错误;(2) 单片机质量有问题;(3) 晶振质量有问题;(4) 负载电容或匹配电容与晶振不匹配或者电容质量有

2019-09-25 08:27:35

1、单片机晶振不起振原因分析遇到单片机晶振不起振是常见现象,那么引起晶振不起振的原因有哪些呢?(1) PCB板布线错误;(2) 单片机质量有问题;(3) 晶振质量有问题;(4) 负载电容或匹配

2021-11-25 09:04:03

请问单片机上的晶振两端的电压可以测量么?是多少?为什么我测模块开发板上晶振两端的电压是0啊?还有就是示波器看晶振两端的波形怎么不一样?另一块板子晶振两端怎么测不了波形?

2017-07-25 16:09:00

现在数据中心的交换机产品硬件上设计越来越大,一张板卡上时钟数量少的几路,多的要十几二十几路。经常使用一个晶振、多个buffer的设计。那么在这种情况下晶振的冗余设计是否有必要?如果有必要如何设计晶振的冗余才好呢?能在主时钟挂掉的时候,备用时钟能迅速的顶替?请大神们发表下看法!

2016-01-13 09:10:12

请教因为晶振旁边连接2个电容来谐振,所以我判断是无源晶振靠谱吗?还有怎么判断这个晶振的好坏,我只有万用表和一个还不会用的示波器。(晶振在PCB上,不拆下来的前提下)多谢指点。

2018-11-19 14:17:56

事项.引起晶振不起振的原因有:(1) PCB板布线错误;(2) 单片机质量有问题;(3) 晶振质量有问题;(4) 负载电容或匹配电容与晶振不匹配或者电容质量有问题;(5) PCB板受潮,导致阻抗失配而不能起振

2018-02-07 10:55:51

电容值不正确。

3. PCB Layout 分析

**·**检查布局:使用电路设计软件或手动检查PCB Layout,确保晶振电路与单片机或芯片引脚的布局尽可能靠近,以减少信号传输的干扰和损耗

2024-03-06 17:22:17

://www.kaiyuexiang.com/index.aspx 插件圆柱晶振一般都是两脚直插型,凯越翔的圆柱晶振可以根据客户的要求剪脚或者套管印字等等。圆柱晶振体积上分为1x5mm、2x6mm、3x8mm以及

2017-06-09 17:16:46

如何用频稳测试系统快速地了解高稳晶振的性能?频率误差倍增法测频的基本原理是什么?测试系统怎样设计?频稳测试系统怎样设计?

2021-04-07 06:31:28

`普通晶振就是市面上最常见的那种,主要应用在消费类产品上,像MP3、U盘、DVD、遥控玩具音响等电子产品,普通晶振最常用价格也最便宜,这样的普通消费类电子产品在使用过程中没有发热以及震荡环境方面

2017-07-12 15:53:37

比较常用的晶振PCB封装

2017-12-13 09:32:26

谁知道FPGA CYCLONE IV E系列板上晶振的使用,我用了一个PLL,需要配置引脚 inclk0,怎么连接到开发板上的50Mhz晶振

2014-11-24 19:15:52

谁知道FPGA CYCLONE IV E系列板上晶振的使用,我用了一个PLL,需要配置引脚 inclk0,怎么连接到开发板上的50Mhz晶振

2014-11-24 19:22:56

深圳回收晶振 收购晶振深圳回收晶振 收购晶振,优势回收◆◆ 我司专业收购晶振,回收有源晶振,收购无源晶振,帝欧电子长年专业收购壹:回收日本晶振品牌如下:爱普生Epson、日本电波NDK、京瓷

2021-01-04 17:11:46

温度变化产生的振荡频率变化量削减的一种石英晶体振荡器。 2、凡是需要提供电源电压的都是有源晶振,它大致包括普通晶振、压控晶振、温补晶振、恒温晶振。 3、温补晶振属于有源晶振,它是在普通晶振的基础上

2013-08-14 16:03:58

就是晶体与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电容也会越大,晶体在PCB边缘与在PCB中间时电场分布如下:PCB边缘的晶振与参考接地板之间

2020-06-09 15:44:58

晶振有两脚和三脚之分,这是晶振电路符号 这是晶振在PCB板电路上正面图 这是晶振内部结构和电路符号 这是石英晶体的压电效应示意图 这是晶振等效电路和实验电路 这是恒温晶体振荡器原理框图 这是MCXO数字温补晶振原理框图

2017-04-10 11:10:06

调节振荡电路对晶振输出的激励电平。一般而言,激励电平越小越好,处理功耗低之外,还跟振荡电路的稳定性和晶振的使用寿命有关。4、 晶振内部水晶片上附有杂质或者尘埃等也会导致晶振不起振晶振的制程之一是水晶

2017-11-07 15:21:22

调节振荡电路对晶振输出的激励电平。一般而言,激励电平越小越好,处理功耗低之外,还跟振荡电路的稳定性和晶振的使用寿命有关。4、 晶振内部水晶片上附有杂质或者尘埃等也会导致晶振不起振晶振的制程之一是水晶片镀

2017-10-25 14:35:47

`繁多复杂的型号是晶振行业公认的特点,除了型号之外客户还会问到晶振的负载电容、频差、脚位、电阻以及温度,当然还有各种加工条件,一个刚入行的新人想彻底搞明白这些也得费一番功夫,最难的是有时候客户也

2017-06-15 14:21:16

、可以改变晶体两端的电容,说不定晶振就能正常工作了,电容的大小请参考晶振的使用说明。 五、在线路板布线时晶振电路的走线应尽量短且尽可能靠近IC,杜绝在晶振两脚间走线。 相信使用这五大方法,一般来说也就能解决线路板上晶振不起振的情况了,如果您还有疑问的话,可直接咨询联系深圳市松季电子有点公司。

2013-10-21 16:02:20

`请问线路板布局设计需要掌握哪些要点?`

2020-03-20 15:04:04

(PF)和精度(PPM); 第二点,采购32.768K的晶振时,需要掌握晶振的精度、型号或者体积,如果是贴片晶振,那么只需要掌握晶振的负载和精度就可以了,如果在晶振不知道型号的情况下,需要具体描述插件晶

2016-04-26 12:02:36

大家好!新购买回来的CC2541空白芯片,焊接到PCB板上后,其外部晶振是否会起振?外部晶振不启振的情况下,是否可以使用CC Debuger下载程序?我做的板子晶振离芯片有点远,是否因为这个而不起振,导致CC Debuger不能连接上芯片呢??下图是我的PCB板

2019-09-26 10:10:39

本帖最后由 一只耳朵怪 于 2018-6-14 09:56 编辑

各位: F28035使用外部有源晶振时和使用内部晶振在寄存器的配置上除了选择外部晶振源还有其他的注意事项吗? 我在实验时,同样

2018-06-14 05:05:47

PCB板上的功用是相同的,即可以进行相互替换,举例来说,我们常用的U盘上用的的晶振12.000MHZ无源,那么你可以用圆柱型晶振AT308 12MHZ,也可以用HC-49S 12MHZ晶振。 不同的地方

2013-11-04 16:54:20

`采购晶振,我们需要掌握晶振的型号、负载、频差;如果是贴片晶振,从型号就可以看出晶振的体积、封装。只需要掌握晶振的负载和精度就可以了。插件晶振也如此。插件晶振在不知道型号的时候,需要具体描述插件晶振

2017-06-08 14:30:47

时钟(Clock)在一般SoC电路上是必不可少的,精准的时钟通常由晶振提供,晶振很难集成到芯片中去,而是作为分立元件设计在PCB上

2022-06-23 08:47:30

电子发烧友App

电子发烧友App

评论