概述:CD4060是一款14级二进制串行计数/分频器,它是由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。所有的计数器位均为主从触发器。

2021-04-08 07:40:14

如何用multisim软件仿真双时钟加/减计数器CT74LS192和译码器CC4511和译码器SM4205构成的30进制加法计数器和30进制减法计数器,求仿真接线图。PCB打样找华强 http://www.hqpcb.com/3 样板2天出货

2012-10-07 21:13:28

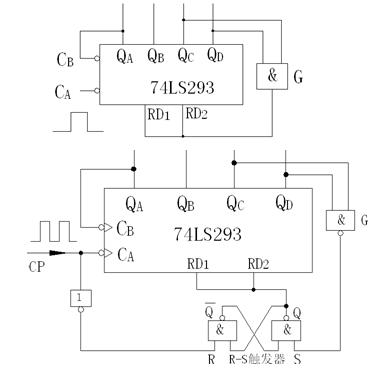

缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入

2011-08-01 16:25:44

用protues 怎么做多级十进制分频器

2016-06-04 07:55:03

十进制 好,那就让我们来看看十进制 所谓十进制就是以10为基数的计数体制,其计数规律是逢十进一。 图1.3.1展示了十进制的位号和位权之间关系的图解。位号3210-1-2-3十进制数

2009-04-06 23:47:02

计数器。4、用74390两个宏连接成八位十进制异步计数器。5、用74161用清零和置数法组成六进制和十二进制计数器。6、分别用D触发器和同步计数器加译码电路的方法构成7进制电路实现如下编码:[0→2→5

2009-10-10 11:47:02

刚开始接触Multisim,我用的是Multisim14,今天画了一个电路图 实现十进制计数器显示的功能,但仿真是报错 Transient time point calculation did not converge ,找不出原因,希望大家帮我找找错在哪里了哈

2016-08-14 20:18:16

计数器。如图9-4所示为一个由CC40192十进制计数器接成的6进制计数器。(2) 利用预置功能获M进制计数器图9-5为用三个CC40192组成的421进制计数器。外加的由与非门构成的锁存器可以克服器件

2009-10-11 10:00:11

内含有共阴、共阳十进制计数器的原理图和芯片文档

2013-12-03 16:03:53

随着fpga学习深入,有以下问题求高手帮忙1,复位信号往往高扇出,那复位越少越好,有的就不需要复位,比如分频器的计数,那哪些地方都可以不复位呢?2,verilog中使用数值判断之类的,使用十进制

2014-03-06 19:49:09

本帖最后由 lianyicq 于 2015-7-23 08:49 编辑

请教一个简单的问题,在Proteus下用4个带复位端的边沿触发JK触发器构成一个十进制加法计数器,清零信号在状态为

2015-07-20 11:27:01

; S92 Q2 Q1 GNDT4290(T1290、74LS290、T210),是一个二-五-十进制计数器,能够进行二进制、五进制计数、通过简单联线组成十进制计数

2008-07-05 13:41:26

请问给位大神,只用触发器和简单的逻辑门怎样设计一个同步清零的二十进制的计数器

2013-10-16 22:00:52

这是一个可以对照显示0~9这10个数字的二进制和十进制的电路。二进制数字用4个发光二极管显示;它们排成一行,亮表示1,灭表示0。十进制数字用一个数码管表示。数字的变化采用CD4040组成加法计数器,手动加1计数。

2021-04-27 07:21:40

具体的思路是这样的十进制加法:开关高电平,从0计数到9,然后又跳到0十进制减法:开关低电平,从9计数到0,然后又跳到9这俩都是循环的还有就是要清零,按下j1之后,数码管马上显示0,计数器重新从0开始

2013-12-25 20:47:27

求一份关于数电的四位十进制的加减法计数器!!!感谢各路大神!!!

2016-03-10 13:28:19

1、实现一个24进制加法计数器的设计本实验设计实现一个24进制的加法计数器,它由晶体振荡器、分频器、计数器和数码管显示器组成,图6.1是该加法计数器的示意图。晶体振荡器产生稳定的50MHz的脉冲信号

2022-07-05 15:14:27

这种方式只消耗不多的逻辑单元就可以达到对时钟的操作目的。2、整数倍分频器的设计2.1 偶数倍分频 偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频

2014-06-19 16:15:28

我想知道我们如何使用代码而不是 UI 更改 STM32 中定时器的预分频器和计数器周期的值。请帮忙。

2023-02-02 08:17:12

目录一、顶层程序二、系统产生测试信号单元三、400HZ分频器单元四、控制信号单元五、8位十进制计数器5.1一位十进制计数器六、锁存器单元七、LED控制顶层程序7.1 400Hz分频器7.2 计数器

2022-01-18 07:36:48

描述带预分频器的 Arduino 射频频率计数器SAB6456 预分频器用于除以 64/256,上限为 1 GHz。固件可在:https ://github.com/imsaiguy/Frequency-Counter-Board

2022-07-04 07:02:14

模M的十进制加/减可逆计数器设计、仿真与实验学习目标:熟悉常用MSI集成计数器的功能和应用,掌握利用集成计数器构成任意进制计数器的一般设计方法;学会利用EDA软件(Proteus)对模M的可逆计数器

2009-09-16 15:06:52

请教一个数电的问题,我想设计一个可预置数 六十进制 (从60开始倒计时)减法计数器 ,可是我做出来的只能从59开始倒计时,不知道怎么改进啊,求赐教啊。 附件为我做的Proteus 的电路仿真。

2013-05-09 00:03:04

求74ls161十进制减计数器接法,有电路图最好,我正在用multisim软件来仿真,谢谢了!!

2013-05-22 10:58:35

`朋友们好!我想求一个,可加减计数器0-99999 ,6位。能给出仿真电路和程序那就太好了。`

2013-06-05 16:20:03

求高手帮忙,整一个FPGA 8位 计数器 十进制 的怎么搞!

2012-11-02 00:18:20

计数器(Counter)由基本的计数单元和控制门所组成,是在数字系统中对脉冲的个数进行计数,以实现测量、计数和控制功能,且兼有分频功能的仪器。计数器按进位制不同,分为二进制计数器和十进制计数器;按

2021-12-08 08:32:28

EDA初学者,求各位同路人帮忙设计一个十进制计数器,用VHLD语言

2014-04-27 09:59:48

)分频器、预分频器与计数器两大类,覆盖的频率范围都包含我需要的2GHz,我想知道,(1)和(2)这两类分频器有什么不同吗?是否是输入信号格式要求不同?第(1)的手册中没有提到相噪,是否(1)比(2)的相噪

2019-01-11 13:39:43

谁能说说计数器和分频器有什么异同呢?

2013-06-20 16:55:20

本人用原理图输入法设计二位十进制计数器,下面是一本书上的图:用Quartus 2编译时出现下面错误:请求各位大侠解决 啊,谢谢了。

2011-05-14 14:14:18

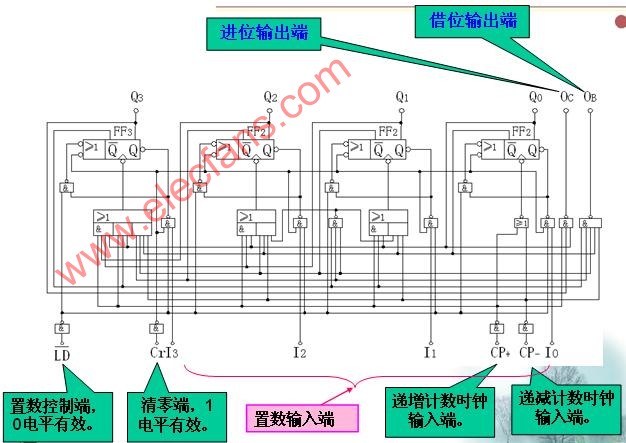

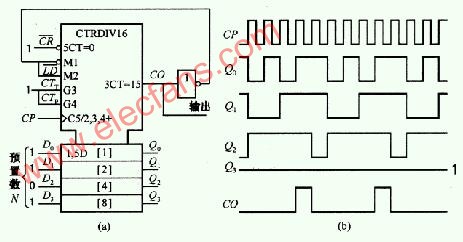

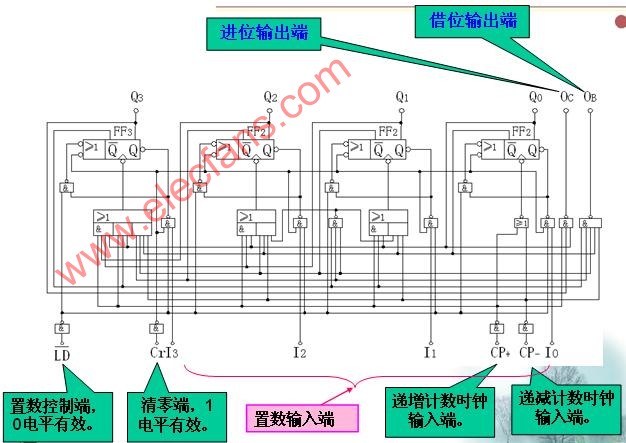

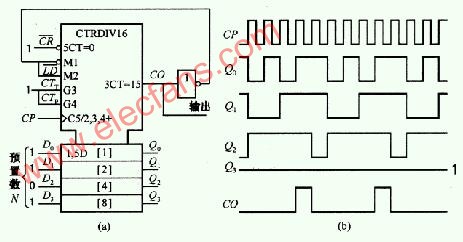

④ 构成脉冲分频器集成十进制计数器【74LS290】集成十进制计数器【74LS390】1. 集成四位二进制计数器【74LVC161】(1) 逻辑符号CR:CR:CR: 异步置0端。优先级最高。PE:PE:PE:并行置数端。次高优先级。TC:TC:TC:进位信号。CEP,CET:CEP

2021-07-29 07:20:09

面试官问道针对一个大数分频器(比如1千分频1万分频)的计数器,有什么好方法可以节省一点资源? 当时想了很久,就说按实际分频用到多少位就分配几位,避免一些无用寄存器的使用。然后他摇了摇头,我向他请教

2016-08-16 16:39:47

TTL 二进制同步可逆计数器

2009-08-03 09:05:53 26

26 4026 CMOS 7段显示十进制计数 分频器:

2009-08-08 09:08:02 29

29 CD4017 十进制计数/分配器 *CD4020 14位二进制串行计数器/分频器 *CD4022 八进制

2006-04-17 21:18:42 3874

3874 十进制计数器

二进制计数器具有电路结构简单、运算方便等特点,但是日常生活中我们所接触的大部分都是十进制数,特别是当二进制数的位数较多时,阅读非常困难,还

2007-06-20 13:46:05 4188

4188 十进制可逆计数器74LS192引脚图管脚及功能表

2011-05-19 11:22:27 121074

121074 计数器的级连使用

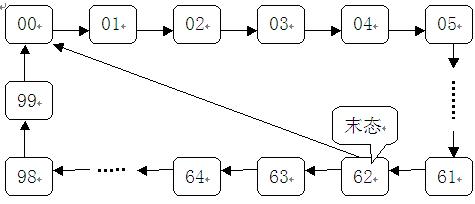

一个十进制计数器只能显示0~9十个数,为了扩大计数器范围,常用多个十进制计数器级连使用。

2007-11-22 12:53:25 3379

3379

2位十进制可加减计数器电路-74LS190应用电路

2007-12-07 00:12:12 9926

9926

十进制计数器工作原理

同二进制计数器相比,十进制计数器较为复杂。分析步骤一般是:

2008-01-21 13:15:22 28596

28596

60进制计数器,由于24进制、60进制计数器均由集成计数器级联构成,且都包含有基本的

2008-06-30 00:00:41 15785

15785

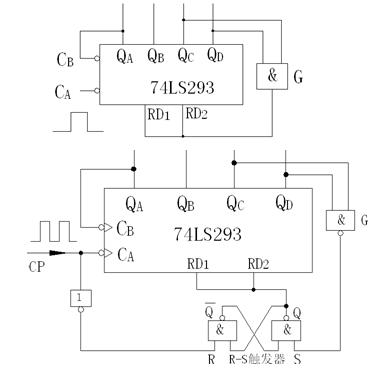

用16进制计数器先级联后预置数构成的63

2008-07-05 13:54:55 2831

2831

先级联后预置数构成的63进制计数器:我们同样也可以先用级联法组成10i计数器、或16i计数器,再用预置

2008-07-05 13:58:00 1507

1507

两片4位二进制数加法计数器74LS161级联成五十进制计数器。

2009-03-28 10:10:23 34301

34301

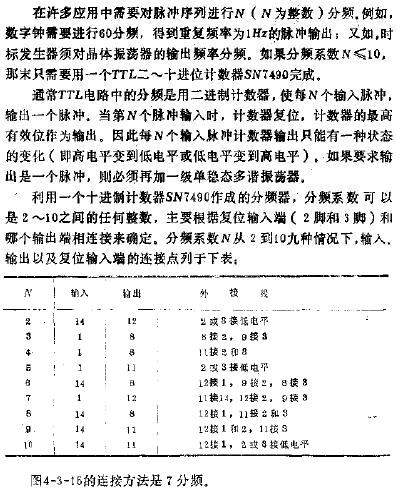

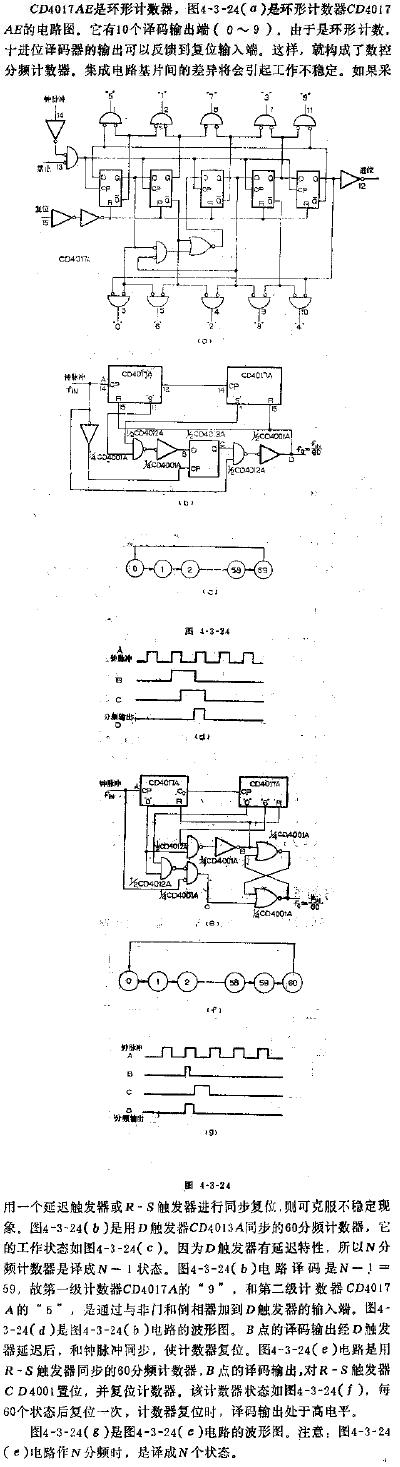

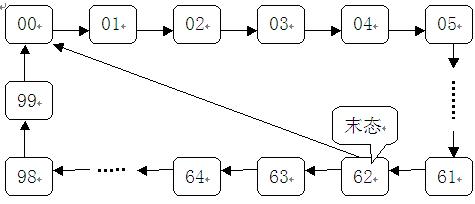

TTL十进位计数器构成的分频器

2009-04-11 10:14:57 1163

1163

用CMOS集成电路构成的数控分频计数器

2009-04-11 10:27:52 697

697

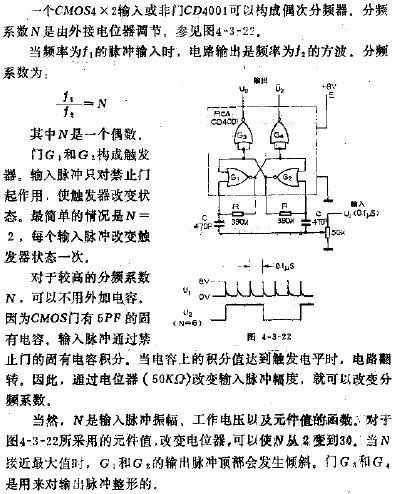

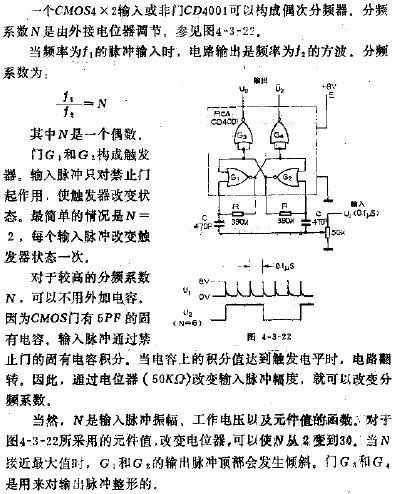

由CMOS门构成的可调分频器

2009-04-11 10:28:20 962

962

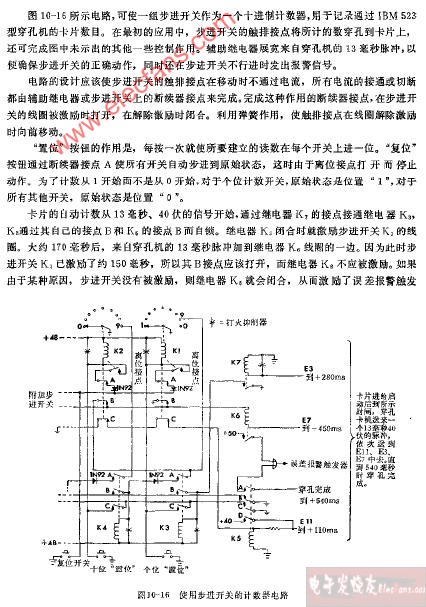

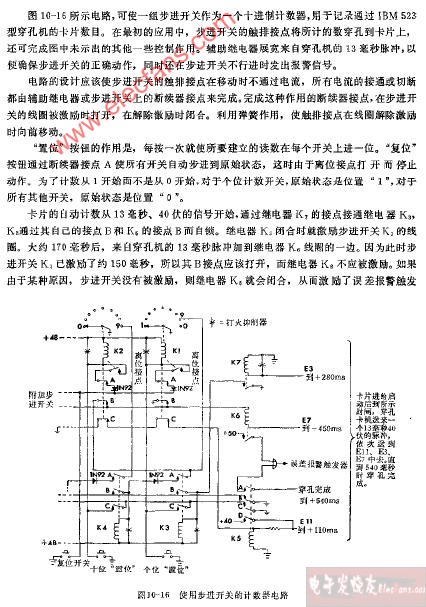

步进开关作为十进制计数器电路图

2009-06-30 13:08:13 944

944

8421码同步十进制递增计数器

2009-09-24 11:09:34 6125

6125

T1192型同步十进制可逆计数器

2009-09-24 11:10:59 1352

1352

异步十进制递增计数器

2009-09-24 11:12:05 1195

1195

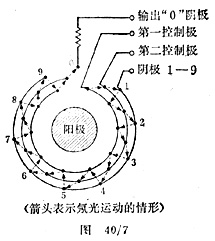

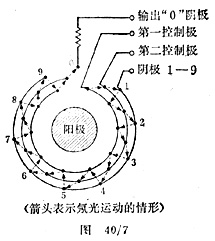

十进制计数管 十进制计数管是由中央的圆板状阳极和围绕着它放置的三十根线状的电极组成。这些线状电极三根一组,共十组,每

2009-10-13 15:05:12 1490

1490

可编程分频器电路

可编程分频器:计数器可以对计数脉冲分频,改变计数器的模便可以改变分频比。根据这个原理,可以用集成计数

2010-01-12 13:58:07 3187

3187

十进制计数器,十进制计数器原理是什么?

二进制计数器具有电路结构简单、运算方便等特点,但是日常生活中我们所接触的大部分都是十进制数,特

2010-03-08 13:19:54 24108

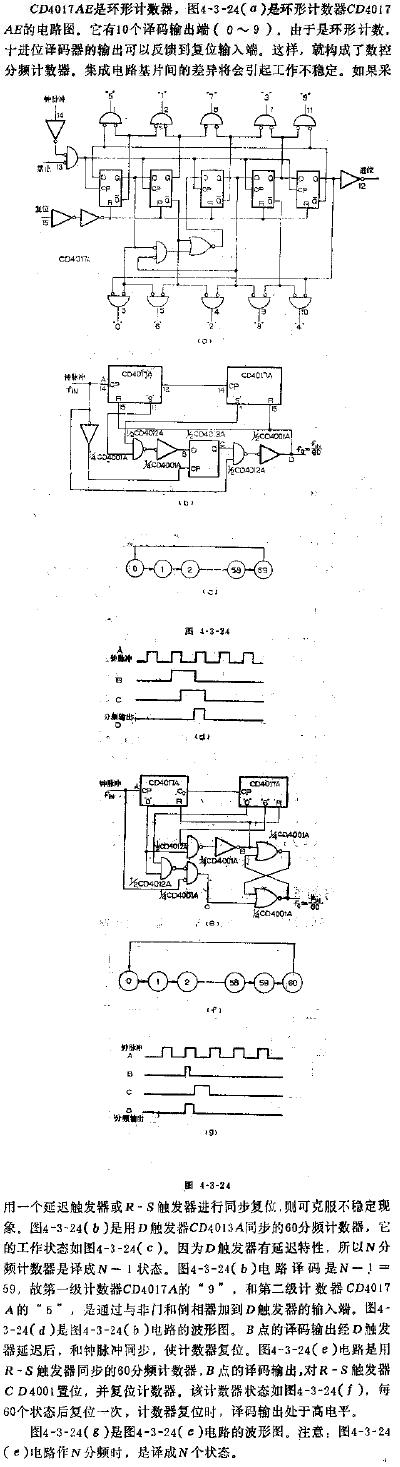

24108 图中所示是用C180 2-10进制同步加法计数器组成的时基分频器(多级串行计数)线路.图中晶体振荡器采用振荡频率为

2010-10-19 15:03:29 1574

1574

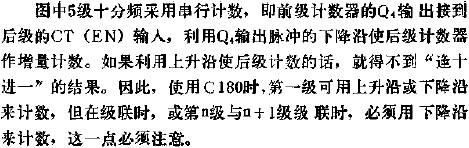

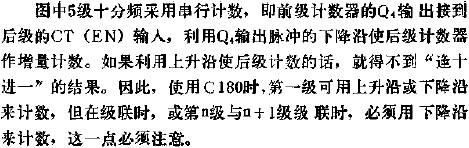

分频器及量程选择电路 分频器是由多级计数器完成,目的是得到不同的标准时基信号。采用4片双十进制中规模计数器CD4518级联可获得10

2010-11-06 11:57:17 1834

1834

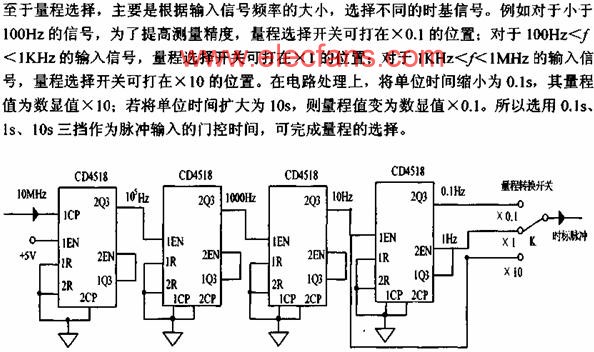

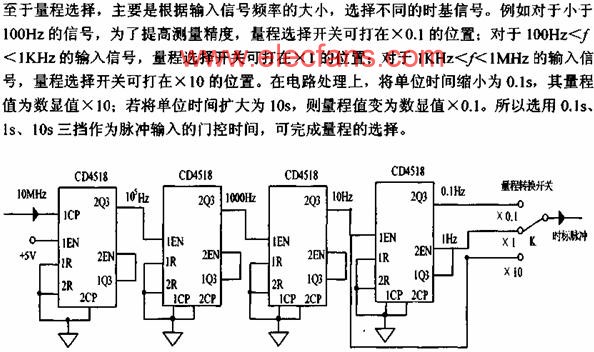

使用一片ICM7217A配4只共阴极LED数码管,可构成4位十进制可逆计数器,其

2010-12-10 13:55:24 7311

7311

数字电子威廉希尔官方网站

--中规模集成计数器及其应用--同步、异步二五十进制计数器-PPT

2016-03-22 14:33:06 0

0 HL配套C实验例程分频器1(计数器实现),配合开发板学习效果更好。

2016-04-11 17:14:06 7

7 CD4017 十进制计数器的应用实验

2022-05-11 16:58:25 0

0 约翰逊MC14017B是五级十进制计数器内置代码转换器。 高速运行和约翰逊spike-free输出是通过使用十进制计数器的设计。 十个解码输出通常是低,只在适当的十进制时间走高。 输出的正向变化的时钟脉冲。 这部分可用于分频应用程序以及十进制计数器或十进制译码显示应用程序。

2017-04-06 09:03:48 28

28 集成计数器常见的是多位二进制计数器及十进制计数器,当需要实现其它进制计数器时,通常利用现有的集成计数器进行适当的连接而构成。对于当设计要求没有限定计数器的状态编码时电路设计的灵活性问题已有文献进行

2017-11-09 16:36:16 81

81 针对任意进制(N进制)计数器的设计目的,采用反馈复零法对基于同步十进制计数器7415160进行设计,分别采用异步清零法实现了6进制计数器和同步置数法实现7进制计数器的设计,通过应用EWB软件对所设

2017-12-21 17:08:37 62805

62805

60进制计数器,由于24进制、60进制计数器均由集成计数器级联构成,且都包含有基本的十进制计数器,从设计简便考虑,芯片选择同步十进制计数器

2017-12-22 13:55:48 153475

153475

使用两片74LS161芯片级联的形式来构成六十进制计数器,一片控制个位,为十进制;另一片控制十位,为六进制。

2018-01-17 13:58:47 56134

56134

本文主要介绍了74ls160十进制计数器电路的设计与实现。74LS160是二~十进制同步可预置计数器,1脚Cr为清零端,低电平有效.2脚CP为时钟脉冲输人端,上升沿触发.3~6V脚D1一D4为数据

2018-01-18 15:14:45 199667

199667

本文主要介绍了74ls160构成24进制计数器电路设计。本设计采用异步清零。由两片十进制同步加法计数器74LS160和一片与非门74LS00以及相应的电阻开关组成。由外加送来的计数脉冲送入两个计数器

2018-01-18 15:43:05 153589

153589

74LS290为异步二-五-十进制加法计数器。本文为大家介绍74ls290构成31进制计数器电路。

2018-01-25 14:36:39 17741

17741

74ls290是一个二,五,十进制计数器,本文为大家介绍由74ls290构成的各种进制计数器的电路。

2018-01-26 09:26:11 112216

112216

本文主要介绍了74ls163实现十进制计数器电路。改变74LS163二进制计数器为十进制计数器,即用一FDS4435BZ个与非门,其两个输人取自QA和QD,输出接清零端α‘R。当第9个脉冲结束时

2018-05-08 11:31:20 48594

48594

功能,并且具有进位信号输出,可串接计数使用。重点分析了构成N进制计数器、以74LS163为基础设计一个6分频电路等。

2018-05-08 14:27:23 59407

59407

本文主要介绍了74ls161分频电路图大全(脉冲分频电路\同步加法计数器)。计数器又称为分频器。N进制计数器的进位输出脉冲就是计数器输入脉冲的N分频。N进制计数器可直接作为N分频器。用同步加法计数器

2018-05-08 14:41:38 102553

102553

本文主要介绍了两个74LS192级联构成两位十进制计数器。以两个74LS192级联构成两位十进制计数器控制实现0.0~9.9V的切换为例。低位计数器输出Qo、Qi、Q2、Q3分别提供0.1V

2018-05-09 09:52:23 56277

56277

,S8424是两组RS T触发器.S8480是4×2输入与非门。二-八进制拨盘开关用来确定分频器的分频系数,以保证触发器复位。如果采用二-十进制拨盘开关,另外再加一个触发器和两个二极管。则可构成分频系数为1~10的分频器。

2018-10-03 18:37:02 427

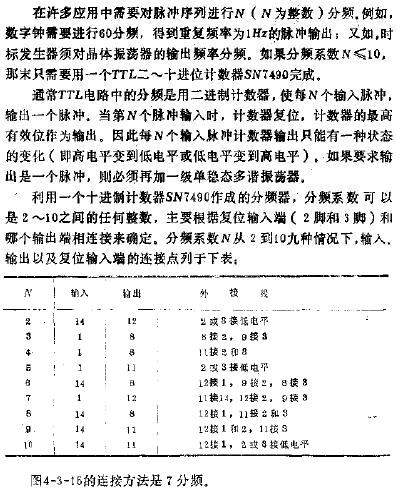

427 关键词:SN74150 , SN7442 , SN7490 , 数字分频器 如图所示为数字分频电路。该电路由3块集成电路构成,分频系数可以从1~9变化。计数器SN7490输出的二-十进制数送至译码器

2018-10-08 07:58:01 1750

1750 偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。

2019-02-01 01:49:00 1029

1029

40110 为十进制可逆计数器/锁存器/译码器/驱动器,具有加减计数,计数器状态锁存,七段显示译码输出等功能。

2019-04-30 08:00:00 6

6 十进制计数器是人们最常用的计数器,但在某些特殊的计数场合下,也需要其他进制的计数器。

2020-01-14 09:46:48 7192

7192

电子秒表一般由振荡器、分频器、计数器、译码器、显示器等几部分组成。其中振荡器和分频器组成标准秒信号发生器,由不同进制的计数器、译码器和显示器组成计时系统。信号送入计数器,累计结果以分、秒、分秒的数字显示出来,分、分秒由十进制计数器构成,秒由六十进制计数器构成。

2020-10-16 08:00:00 1

1 芯片74ls160是十进制计数器,这种同步可预置十进计数器是由四个D型触发器和若干个门电路构成。

2021-06-05 14:35:38 14045

14045 电子发烧友网站提供《带预分频器的Arduino射频频率计数器.zip》资料免费下载

2022-07-06 09:26:04 0

0 二进制编码的十进制是一个串行数字计数器,可计数十位数字,它会为每个新的时钟输入重置。由于它可以通过10种独特的输出组合,因此也被称为“十进制(BCD)计数器”。十进制计数器可以计数0000、0001、0010、1000、1001、1010、1011、1110、1111、0000和0001等。

2022-10-31 16:25:37 15920

15920

偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。

2022-11-21 09:41:24 751

751 本方案是一个基于 FPGA 的十进制计数器。共阳极 7 段显示器上的 0 到 9 十进制计数器,硬件在 Xilinx Spartan 6 FPGA 板上实现。

2022-12-20 14:52:25 2

2 双十进制纹波计数器-74HC_HCT390

2023-02-15 19:06:31 0

0 带 10 个解码输出的 Johnson 十进制计数器-74HC_HCT4017

2023-02-16 20:29:32 0

0 带 10 个解码输出的 Johnson 十进制计数器-74HC_HCT4017_Q100

2023-02-17 19:59:07 1

1 可预置同步BCD十进制计数器;异步复位-74HC160

2023-02-20 20:05:50 10

10 基于51单片机的分频器1(计数器实现)例程源代码

2023-05-18 09:54:09 0

0 电子发烧友网站提供《在Verilog HDL中使用分频器的8位计数器的设计.zip》资料免费下载

2023-06-15 10:14:44 0

0

正在加载...

电子发烧友App

电子发烧友App

评论