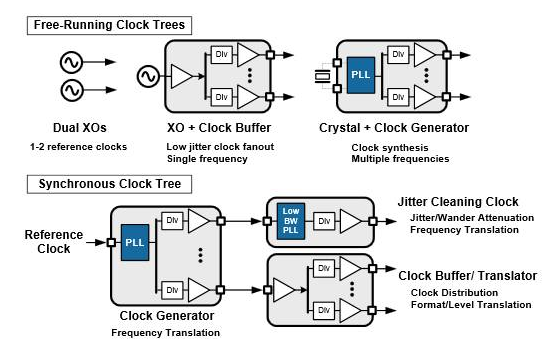

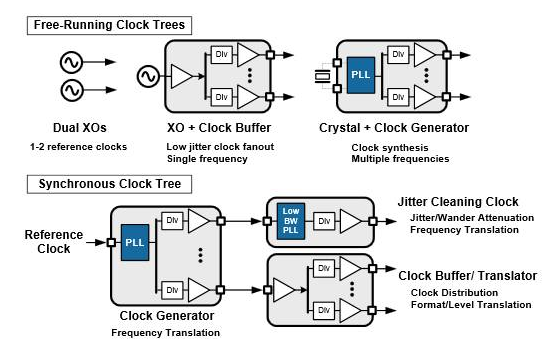

树设计时, “ 一成不变 ” 的策略并不适用,优化时钟树以满足性能和成本的要求取决于多种因素,包括系统架构、集成电路( IC )时序需求(频率、信号格式等)和终端应用的抖动需求。

2017-10-31 09:45:13 5550

5550

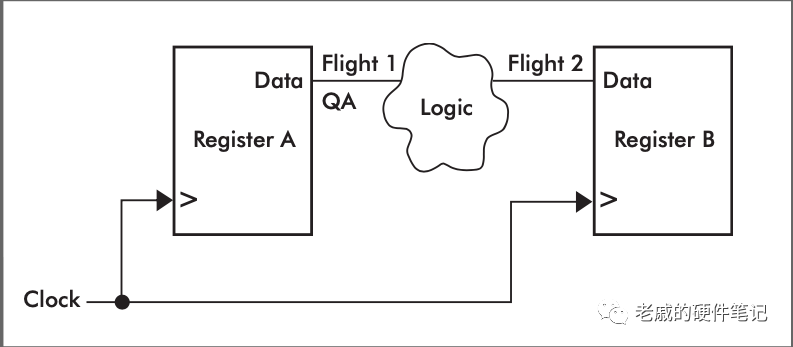

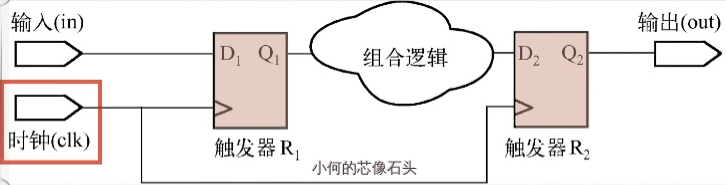

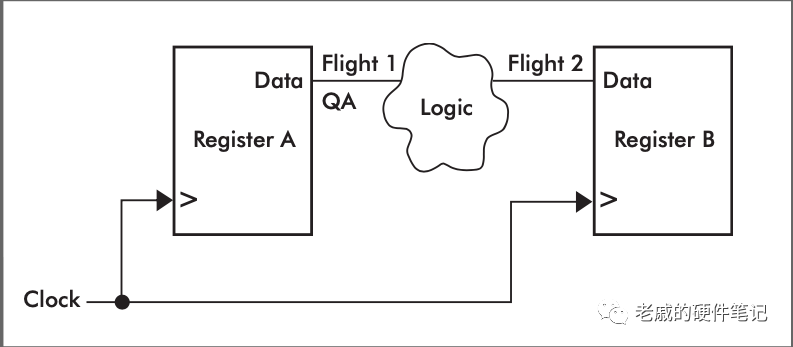

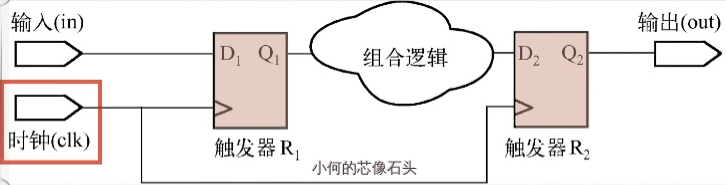

时钟使能电路是同步设计的重要基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但是由于这些时钟是同源的,可以将它们转化为单一的时钟电路处理。在FPGA的设计中,分频时钟和源时钟的skew不容易

2020-11-10 13:53:41 4795

4795

电路设计人员了解到,这些老化效应会改变器件的 Vt,进而减慢时钟信号的上升和下降时间。随着时间的推移,这些老化效应会扭曲时钟的占空比,实际上会导致时钟电路出现故障。

2022-10-17 11:38:10 678

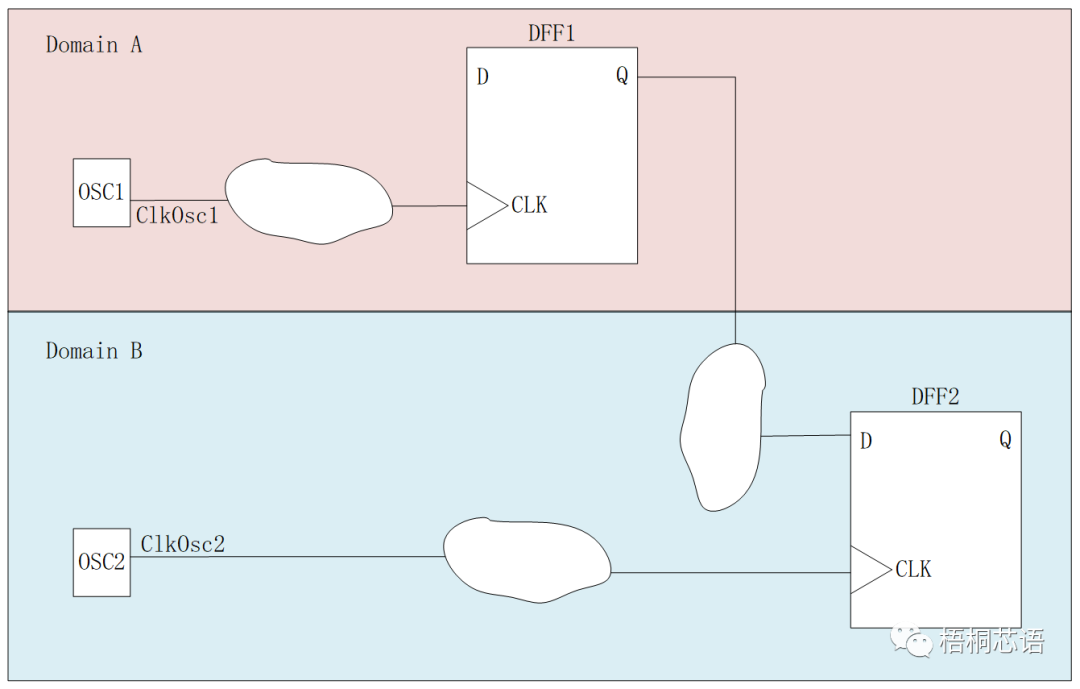

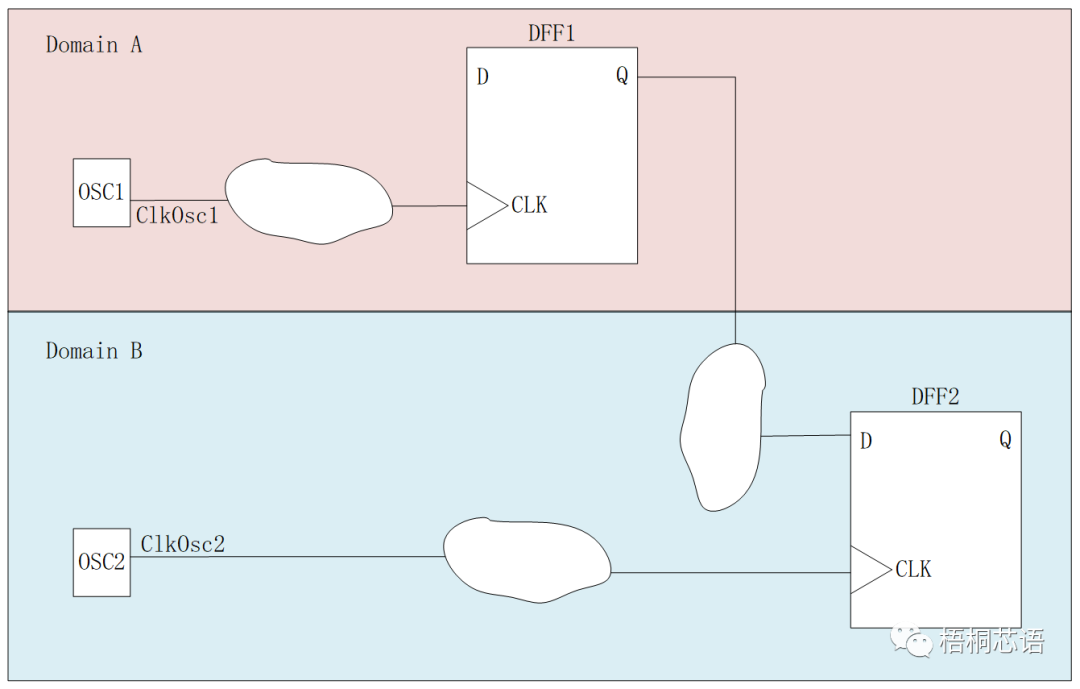

678 在一个复杂的SoC(System on Chip)系统中,不可能只有一个时钟。我们一般认为,一个时钟控制的所有寄存器集合处于该时钟的时钟域中。

2023-08-01 15:48:20 1052

1052

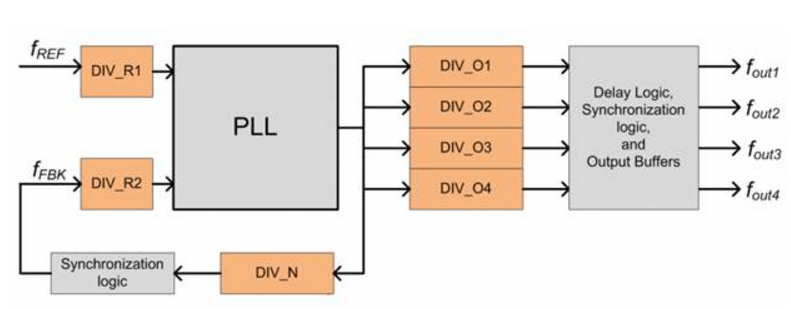

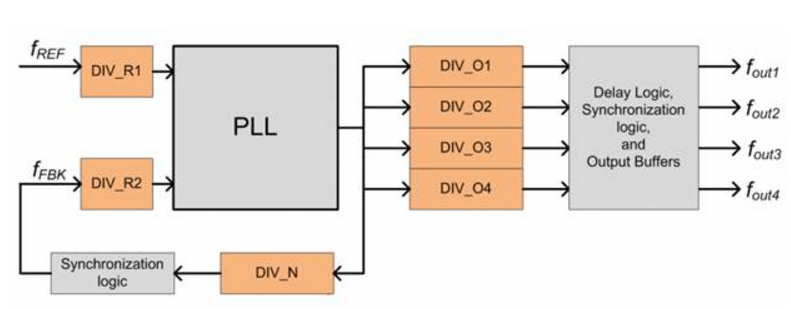

25MHz的时钟源如何得到4路200MHz的时钟信号

2019-01-10 10:19:05

MPC92433 - 1428 MHz Dual Output LVPECL Clock Synthesizer - Freescale Semiconductor, Inc

2022-11-04 17:22:44

你好现在遇到一个问题,MPC5644A芯片的时钟配置方式是从同事那里学来的,发现如果要将MPC5644A系统配置为80M,必须先配置为40M,想知道这个过程是否合理?如果我直接把系统时钟配置成80M

2023-04-18 07:54:14

种噪声有可能非常严重,导致系统的性能大大降低。即使你使用了高性能器件(当然价钱也很高),如果你使用的时钟由于种种原因导致边沿发生了抖动,也会让你的系统产生灾难性的后果。实际电路中的时钟信号会发

2019-05-06 09:16:07

时钟设备设计使用 I2C 可编程小数锁相环 (PLL),可满足高性能时序需求,这样可以产生零 PPM(百万分之一)合成误差的频率。高性能时钟 IC 具有多个时钟输出,用于驱动打印机、扫描仪和路由器等

2019-08-12 06:50:43

在很多设计中,虽然内部不同模块的处理速度不同,但是由于这些时钟是同源的,可以将它们转化为单一的时钟电路处理。在FPGA的设计中,分频时钟和源时钟的skew不容易控制,难以保证分频时钟和源时钟同相

2013-01-08 09:06:49

非常多,但是并非所有外设都需要系统时钟这么高的频率,比如看门狗和RTC只需要几十K的时钟即可。同一个电路,时钟越快,功耗越大,同时抗电磁干扰能力也会越弱,所以对于较为复杂的MCU一般采用多时钟源的方法来

2021-08-12 06:45:07

的主要缺点是,您放弃了实现dc、地震、音频和更高带宽应 用的绝对最高可能性能所需的自定义和优化。在急于重用和完 成设计的过程中,往往会牺牲精确性能。其容易忽略和忽视 的一个主要方面是时钟。在本文中,我们将讨论时钟的重要性, 并为正确设计高性能转换器提供指导。

2021-01-27 07:27:36

的晶体时钟源给不同的芯片提供时钟信号,会提高系统成本,增大电路板面积,而且会带来时间同步的问题,好的系统设计会选择使用单一主时钟振荡器作为时钟源,再将时钟信号通过时钟缓冲分配给整个系统中的各个芯片。时钟

2022-06-08 12:54:33

时钟设备设计使用 I2C 可编程小数锁相环 (PLL),可满足高性能时序需求,这样可以产生零 PPM(百万分之一)合成误差的频率。高性能时钟 IC 具有多个时钟输出,用于驱动打印机、扫描仪和路由器等

2018-08-27 09:46:58

检测电路,以适应于不同电机及不同控制方式的要求;同时由于采用了高性能的MCU,更多类型的通信接口可被灵活应用,如:URAT、CAN、RJ45等。

2019-07-09 08:24:02

在外的高速PCB布线使还会带来串扰、信号完整性等非常严重的问题。如果可以在中低端FPGA上实现高速时钟数据恢复电路,则可降低成本且提高整个电路系统的性能。 &

2009-10-24 08:38:08

AD芯片采用外部时钟时,外部时钟源可以是不规则的TTL电平吗?

该TTL电平具体表现为,频率由低到高,再由高到低,最大100K,每一个电平高电平是恒定的,低电平在不停的变化。

这样的TTL电平能作为AD芯片的采样时钟吗

2023-12-22 08:31:46

由锁相环构成的间接式频率合成器在无线通信领域发挥着非常重要的作用。通常采用锁相频率合成器的输出信号来作为无线接收机中的本振信号,以使直接频率调制器、频率解调器能够从输入信号中再生载波。如果用MB1504/MAX2620的话怎么能够实现锁相时钟频率源?

2021-04-14 06:47:07

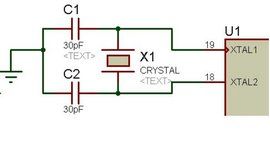

STM32时钟时钟源:时钟源用来为环形脉冲发生器提供频率稳定且电平匹配的方波时钟脉冲信号。它通常由石英 晶体振荡器和与非门组成的正反馈振荡电路组成,其输出送至环形脉冲发生器。晶振脉冲时钟频率(又译

2021-08-18 07:21:56

STM32有以下4个时钟源:高速外部时钟(HSE):以外部晶振作时钟源,晶振频率可取范围为4~16MHz,我们一般采用8MHz的晶振。高速内部时钟(HSI): 由内部RC振荡器产生,频率为8MHz

2021-08-12 07:35:54

时钟源的作用无论是小型单片机还是像STM32这样高级单片机,它们工作的核心都是大规模的时序逻辑电路,而驱动时序逻辑电路的关键则是准确而又稳定的时钟源。它的作用就像小学在操场上做广播体操时...

2021-08-19 07:06:25

Xilinx Virtex 4 和高性能时钟合成器 LMX2531 来满足 9 位 ENOB 高速数字转换器的系统要求。 特性2 个 GSPS 模数转换通道大于 9 位 ENOB 超宽输入频率范围面向测试和测量系统的低成本双通道高速数字转换器原型

2022-09-20 07:01:22

有人要问,采用一个系统时钟不是很简单吗?为什么STM32要有多个时钟源呢?因为首先STM32本身非常复杂,外设非常的多,但是并不是所有外设都需要系统时钟这么高的频率,比如看门狗以及RTC只需要几十k

2021-08-12 06:41:28

什么是时钟? 时钟是单片机运行的基础,时钟信号推动单片机内各个部分执行相应的指令。时钟系统就是CPU的脉搏,决定CPU速率。片机有了时钟,才能够运行执行指令,才能够做其他的处理 (点灯,串口

2022-02-14 07:52:45

fpga的时钟信号,该fpga_clk经过 fpga内部以后,再路由某个管脚将新命名的 ext1_clk与ext2_clk输出给外部ic,100Mhz的ext1_clk与ext2_clk因此称为供源时钟。

2019-08-06 07:42:55

的时钟源。随着集成电路加工中功能器件的尺寸缩小,器件电源电压也呈下降趋势,包括PLL和其它混合信号功能所用的电源。然而,PLL的关键元件——“压控振荡器”(VCO)的实用威廉希尔官方网站

要求并未随之大幅降低。许多高性能

2019-06-26 06:39:37

的引脚。然而,电路板正在接收 200KHz 时钟信号,这让我很困惑?这可以做到吗?板上没有晶体,所以它要么使用那个时钟源,要么使用内部时钟。它的最高频率要求是 115,200 异步 UART,因此内部时钟

2023-01-30 07:58:17

如何解决高温下STM32采用内部晶振作为系统时钟的时钟源导致时序紊乱问题?

2022-02-14 07:09:59

参考频率源,电路和普通电路一样。但要注意确保MODCLK脚在复位时为高,否则系统会出错。 本系统采用Motorola公司推荐的4.194MHz晶振频率,同时通过写时钟合成控制寄存器SYNCR中的相关位

2012-11-15 16:22:38

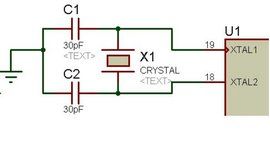

尤其适合于产品线丰富批量大的生产者。无源晶振其缺陷是信号质量较差,通常需要精确匹配外围电路(用于信号匹配的电容、电感、电阻等),更换不同频率的晶体时周边配置电路需要做相应的调整。建议采用精度较高的石英

2013-04-18 15:58:58

是否可以将ETR引脚时钟信号作为定时器的时钟源呢?基于STM32定时器ETR信号有何应用?

2021-11-23 07:46:35

晶体(XTAL)输入之间的自动切换,最小化切换,引起的瞬态,在频率容差范围内工作寿命。小数N分频PLL设计基于成熟的高性能,低抖动频率合成器产品组合,可最大限度地提高网络性能,而整数N分频PLL则提供通用时钟,可用作CPU和现场可编程门阵列(FPGA)参考时钟

2019-02-25 09:40:01

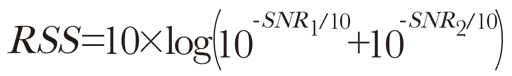

SNR 性能的影响以及怎样降低一个噪声时钟源的抖动。作为基线,DC1826A-A 的时钟输入采用一个罗德与施瓦茨 SMB100A RF 发生器来驱动,并由 Stanford Research SR1 提供

2018-07-19 16:23:22

系统时钟那么高的频率,如果都用高速时钟势必造成浪费。同一个电路,时钟越快功耗越大、抗电磁干扰能力越弱。复杂的MCU采用多时钟源的方法来解决这些问题。如下图,是STM32的时钟系统框图。转存失败重新上传取消如上图左边的部分,看到STM32有4个独立时钟...

2021-08-19 06:33:34

已经有段时间了。但是,在要求快速切换速度、低相位噪声或低杂散信号电平的场合,有必要使用更为复杂的架构。通过正确的设计方法,结合使用现代低成本高集成度的PLL和直接数字合成器(DDS)集成电路(IC

2019-07-08 06:10:06

大家好,我现在设计一个时钟源,由压控振荡器输出10MHz时钟,需要经过一个时钟合成器输出62MHz(jitter值小于2ps)作为高精度ADC和FPGA的时钟源,可是我在ADI官网上寻找了很久,发现

2018-09-25 11:36:31

描述适用于 GSPS 数据转换器的低成本、高性能时钟解决方案。此参考设计讨论如何使用低噪声频率合成器 TRF3765 为 4 GSPS 模数转换器 (ADC12J4000) 生成采样时钟。实验展示了

2018-08-16 06:56:42

频率合成器的高性能架构实现威廉希尔官方网站

详解

2021-04-07 06:48:49

系统时钟源的比较选择及高性能PLL的发展趋势安森美半导体公司 供稿在所有电子系统中,时钟相当于心脏,时钟的性能和稳定性直接决定着整个系统的性能。典型的系统时序

2009-12-20 09:28:06 31

31 无线基础设施、宽带和仪器仪表应用通常需要高性能的时钟电路,它们主要需要时钟的器件是高速数据转换器。这些系统的时钟电路所需的几个关键性能指标包括低相位噪声和抖

2009-07-06 18:37:55 449

449

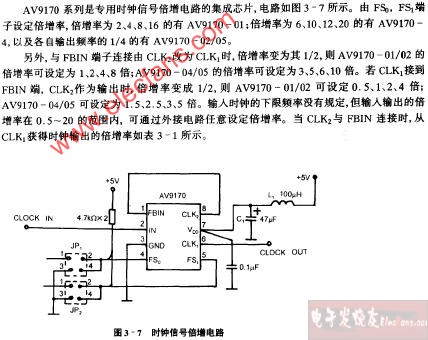

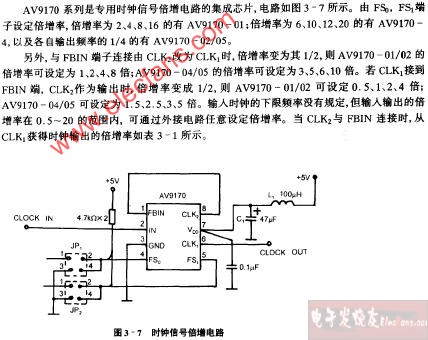

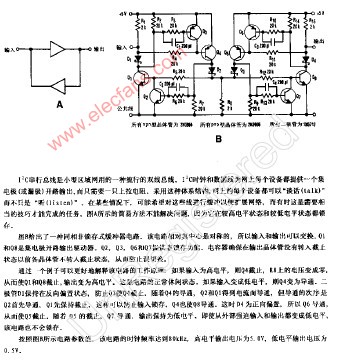

时钟信号倍增电路图

2009-07-14 17:18:36 741

741

IC数据和时钟时钟线缓冲电路

2009-09-12 11:57:02 1372

1372

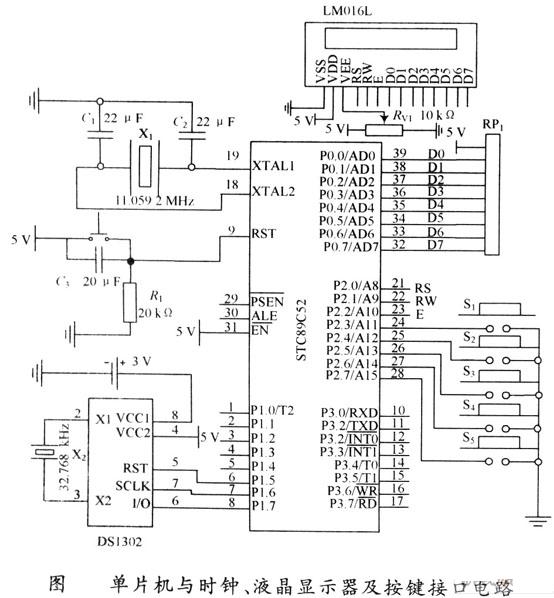

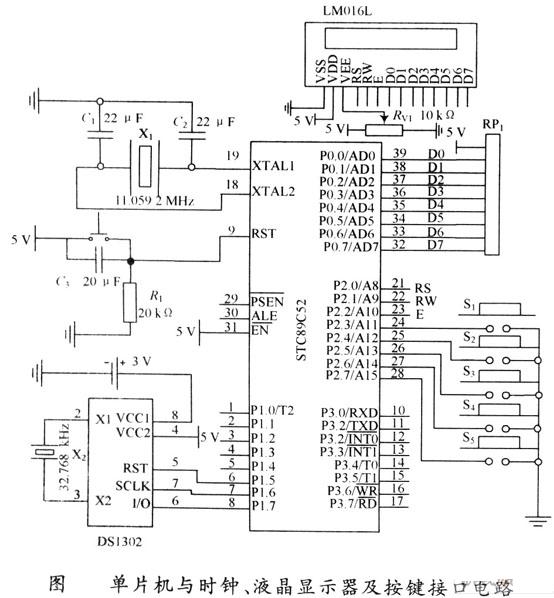

单片机与液晶显示器及按键接口电路

单片机与时钟芯片DS1302接口电路部分:DS1302是美国DALLAS公司推出的一种高性能、低功耗的实时时钟芯片,采用SPI三线

2010-02-16 12:04:02 2283

2283

MAX3679A高性能四路输出时钟发生器(Maxim)

Maxim推出用于以太网设备的高性能、四路输出时钟发生器MAX3679A。器件采用低噪声

2010-04-14 16:51:49 778

778 DS31415是一个灵活的,高性能的不同频率转换时间和频率合成中的应用集成电路。就其三个输入和四个输出时钟时钟,每个设备可以接受几乎任何关系或产生2kHz和750MHz的频率

2011-03-21 11:32:24 1033

1033 DS31407是一个灵活的,高性能的不同频率转换时间和频率合成中的应用集成电路。就其三个输入和四个输出时钟时钟,每个设备可以接受几乎任何关系或产生2kHz和750MHz的频率。

2011-03-21 11:35:53 1159

1159 DS31408是一个灵活的,高性能的不同频率转换时间和频率合成中的应用集成电路。在其八个输入时钟和14个输出时钟,

2011-03-21 11:40:29 1712

1712 信号在不同时钟域之间的转换是复杂数字电路设计中不可缺少的一部分,直接锁存法和锁存反馈法可处理控制信号的同步,异步FIFO在跨时钟的数据交换方面具有高效的优势,本文设计的

2011-08-22 12:07:12 5851

5851

讨论了物理设计中时钟网络的英国威廉希尔公司网站

,并以现有的CPU时钟网络的为例,介绍了高性能CPU的时钟网络英国威廉希尔公司网站

。

2011-12-27 15:28:56 46

46 高性能的时钟同步系统是任何通信传输领域必不可少的,并且在很大程度上决定了整个传输系统的性能,可称之为传输系统的心脏 时钟同步系统是基于锁相环路的同步原理,跟踪一个高

2011-12-28 16:39:39 41

41 提出一种高频时钟电路的设计方案。利用一款先进的可编程时钟合成器MPC92433,基于FPGA的控制,实现4对LVDS信号输出。系统经过测试,输出时钟信号频率达到1 GHz,可以广泛应用到各种数

2012-08-08 11:29:46 24

24 世界上的各种电子设备,每一台中都一定会有好几个电子电路在工作。为了让它们正常发挥功能,离不开间隔规律、稳定的周期信号“时钟信号”。电子电路以这个时钟信号为基准而进行动作。时钟信号既是让各个电路完成其功能的时机提示信号,也是使电子设备与周边的控制器等连动(同步)用的信号。

2016-04-12 13:47:11 5037

5037 我们知道,SERDES对参考时钟有严格的相位噪声性能要求。通常,SERDES供应商会根据其SERDES采用的PLL以及CDR架构特点,以及性能数据,提出对参考时钟的相位噪声的具体要求。

2017-02-10 18:40:10 5965

5965

现议价。不幸的是,相对较少信息已出现在晶体电路和工程师们常常把水晶电路视为一种黑色艺术,最好留给几个熟练的从业者(见盒子),关于石英水晶。 事实上,最高性能的晶体时钟电路要求各种复杂的考虑和微妙实现威廉希尔官方网站

。然而,

2017-05-05 11:38:25 14

14 时钟设备设计使用I2C可编程小数锁相环(PLL),可满足高性能时序需求,这样可以产生零PPM(百万分之一)合成误差的频率。高性能时钟IC具有多个时钟输出,用于驱动打印机、扫描仪和路由器等应用系统的子系统,例如处理器、FPGA、数据转换器等。

2017-08-30 11:04:04 4285

4285

高性能CPU的时钟网络设计

2017-10-30 15:28:58 23

23 在本文中,笔者将谈论抖动合成器与清除器的不同系统参考信号(SYSREF)模式,以及如何用它们来最大限度地提高JESD204B时钟方案的性能。 LMK04821系列器件为该话题提供了很好的范例研究素材

2017-11-17 10:31:45 3009

3009

设计中。 时钟信号是任何数字电路设计的基础,而时钟源是雷达、通信、测试仪器等电子系统实现高性能指标的关键,很多电子设备和系统功能的实现都直接依赖于高性能的时钟源。文中选择时钟合成器MPC92433+FPGA的方式设计高频时钟源,实现了4路LVDS (Low Voltage

2017-11-28 14:41:49 1

1 源。CDCE62005时钟合成器芯片提供了一种现实的时钟解决方案,以满足对高速ADC的严格要求。该应用报告突出了与时钟源相关联的限制性代理,其对ADC信号噪声性能产生不利影响。

2018-05-16 14:26:14 24

24 TI最近推出了一套适合于高速、高IF采样模数转换器(ADC)的设备,如ADS583,它能够采样多达135个MSPS。为了实现这些高性能设备的全部潜力,系统必须提供极低的相位噪声时钟源。CDCE72010时钟合成器芯片提供了现实的时钟解决方案,以满足对高速ADC的严格要求。

2018-05-28 09:09:47 11

11 首先,我们看一下时钟信号中最常见到的波形 - 矩形波(尤其是方波更常用)。在较低时钟频率的系统中我们看到的基本上都是以矩形波为主的时钟信号,因为电路基本上都是靠时钟的边沿(上升沿或下降沿)进行

2018-12-06 11:53:10 59988

59988

想象一下,如果频率较高的时钟域A中的信号D1 要传到频率较低的时钟域B,但是D1只有一个时钟脉冲宽度(1T),clkb 就有几率采不到D1了,如图1。

2019-02-04 15:52:00 10841

10841

ADI研讨会:高性能时钟: 解密抖动

2019-08-20 06:05:00 1656

1656 一个不寻常的电路,“tanktwanger”,提供了一些优于传统时钟合成方法的时钟产生和调整优势。您可以针对众多应用调整主电路,但在构建此VHF设计时必须注意。

2019-08-08 10:51:20 2346

2346

美国马萨诸塞州诺伍德市 - 全球领先的信号处理应用高性能半导体公司ADI公司今天推出了一系列时钟IC,可满足当今高性能电子应用中最严格的信号处理要求,如作为无线基础设施收发器,仪器仪表和宽带基础设施

2019-09-15 16:52:00 3289

3289

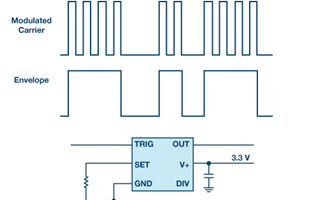

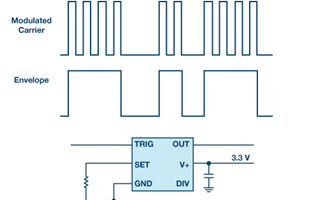

许多模拟电路需要一种时钟信号,或者要求能在一定时间后执行某项任务。对于这样的应用,有各种各样适用的解决方案。

2019-11-19 14:39:36 2676

2676

时钟设备设计使用I2C可编程小数锁相环(PLL),可满足高性能时序需求,这样可以产生零PPM(百万分之一)合成误差的频率。高性能时钟IC具有多个时钟输出,用于驱动打印机、扫描仪和路由器等应用系统

2020-11-03 10:40:00 0

0 时钟篇 选用全局时钟缓冲区(BUFG)作为时钟输入信号,BUFG是最稳定的时钟输入源,可以避免误差。 只用一个时钟沿来寄存数据,使用时钟的两个沿是不可靠的,如果时钟沿“漂移”,就会导致时序错误

2020-12-11 10:26:44 1482

1482 AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515时钟分配IC的高性能ADC的低抖动采样时钟发生器

2021-04-30 09:48:42 13

13 贸泽电子即日起备货Renesas Electronics FemtoClock2高性能时钟频率合成器。

2021-10-14 16:03:12 1331

1331

时钟芯片是一种高性能、低功耗、带RAM的实时时钟电路,时钟芯片可以对年、月、日、周日、时、分、秒运行计时,具有闰年补偿功能,工作电压为2.5V~5.5V。它使用三线接口与CPU运行同步通信,并可使用突发方式一次传送多个字节的时钟信号或RAM数值。

2021-12-20 10:04:00 10463

10463 如果用单独的时钟信号板,一般采用什么样的接口,来保证时钟信号的传输受到的影响小?

2022-09-16 08:58:49 1918

1918

时钟电路是一种电路,它可以产生定期的时钟信号,用于控制电子设备的运行。

它的特点是可以产生定期的时钟信号,可以控制电子设备的运行,可以提高电子设备的精度和可靠性。时钟电路的应用非常广泛,它可

2023-02-20 18:16:38 5973

5973 。高性能时钟芯片是电子设备不可或缺的重要元器件,在服务器、交换机、基站、医疗设备中广泛应用。但是,该领域此前一直为国外厂商所垄断。极景微依托创始团队在超低抖动锁相环威廉希尔官方网站

及创新时钟电路方案领域的深厚积累,成功

2021-11-22 09:47:49 1792

1792

、保持(hold)时间的时序关系,电路的输出(布尔值)就是可预测的,这是数字逻辑电路设计的基础。如果 不能满足建立保持时间 ,我们认为输入是 异步 (asynchronous) 信号 。一个时钟域的同步信号输出到另一个时钟域通常被认为是异步信号。

2023-06-23 17:53:00 898

898

即电路中的所有受时钟控制的单元,全部由一个统一的全局时钟控制

2023-06-27 09:54:21 377

377

时钟电路用于产生稳定的时钟信号,常见于数字系统、微处理器、微控制器、通信设备等。时钟信号用于同步各个电子元件的操作和数据传输,确保系统的正常运行。

2023-08-03 14:46:04 1242

1242 单位宽(Single bit)信号即该信号的位宽为1,通常控制信号居多。对于此类信号,如需跨时钟域可直接使用xpm_cdc_single,如下图代码所示。参数DEST_SYNC_FF决定了级联触发器

2023-08-16 09:53:23 462

462

业界高端FPGA的卓越性能和高口碑声誉都有哪些因素了?其中很重要的一个因素就是FPGA内部丰富的时钟资源使得FPGA在处理复杂时钟结构和时序要求的设计中具有很大优势。设计师可以更好地控制和管理时钟信号,提高时序性能、减少时钟相关问题,并满足设计的高性能和稳定性要求。

2023-08-31 10:44:01 530

530 芯片为什么要时钟信号 芯片是现代电子设备的核心组成部分,广泛应用于计算机、手机、电视等各个领域。芯片内部有着复杂的电子元件和电路结构,这些元件和电路结构需要进行同步操作,以实现正确的工作。因此,芯片

2023-09-01 15:38:11 1376

1376 时钟分频电路通过将输入的高频时钟信号分频,生成较低频率的时钟信号。它通常基于计数器和逻辑门实现,用于将高频时钟信号分解成系统所需的各种频率。

2023-09-14 14:53:57 4894

4894 件、计算机、数字电路和通讯协议等设备的信号。它的主要作用是进行时序控制,使数据传输和处理的时序保持一致。时钟信号一般由计时器产生,其具有一定的周期性、稳定性和精度。 时钟信号的主要信号参数包括周期、频率、精度和占空比等,

2023-09-15 16:28:12 1767

1767 芯片为什么需要时钟信号? 在我们日常生活中,我们所使用的各种电子设备都需要一个时钟信号来进行计时和同步,例如:手机、电脑、电视、汽车、机器人、智能家居等设备都需要时钟信号。对于各种这些电子设备

2023-09-15 16:28:14 1369

1369 的基础,因此,在电子学领域中,如何产生和控制时钟信号是一项至关重要的威廉希尔官方网站

。 时钟信号是指一个周期性的方波信号,其周期性能和稳定性非常重要。为了使时钟信号精确可靠地产生,需要考虑多种因素的影响,包括设备的稳定性、

2023-09-15 16:28:22 1496

1496 时钟信号的同步 在数字电路里怎样让两个不同步的时钟信号同步? 在数字电路中,时钟信号的同步是非常重要的问题。因为在信号处理过程中,如果不同步,就会出现信号的混淆和错误。因此,在数字电路中需要采取一些

2023-10-18 15:23:48 771

771 什么是时钟芯片?时钟芯片的工作原理 时钟芯片的作用 时钟芯片是一种用于计算机或其他电子设备中的集成电路,它提供精准的时钟信号。时钟信号是计算机进行各种操作的基础,比如数据传输、运算等等,所以时钟芯片

2023-10-25 15:02:33 2314

2314 什么器件可以产生时钟信号?时钟信号是用来做什么用的?时钟信号起什么作用? 时钟信号是一个精确的电信号,它可以通过电子器件来产生,并且具有一定的频率和周期。时钟信号在电子系统中具有非常重要的作用,因为

2023-10-25 15:07:45 637

637 什么是时钟电路?什么是脉冲?时钟电路是如何生成脉冲的? 时钟电路是一种电路,它产生的周期性的信号被用作计算机系统的基准。时钟电路产生的信号被称为时钟脉冲或时钟信号。在计算机系统中,时钟信号用于同步

2023-10-25 15:14:17 795

795 时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26:56 298

298 时钟电路是指用于产生稳定、精确的时间基准信号的电路。这种电路通常采用晶体振荡器或者其他稳定的振荡器作为时钟源,产生固定频率的信号。时钟信号被广泛应用于数字系统、通信系统、计算机系统等各种电子设备中,用于同步和控制各种操作和数据传输。

2023-11-17 09:50:08 770

770 电子发烧友网站提供《时钟和频率合成的应用领域.pdf》资料免费下载

2023-11-27 10:41:13 2

2 高性能20路PCIe时钟缓冲器新品推介SQ82100PCI-Express(PCIe)是一种高速串行计算机扩展总线标准,主要用于扩充计算机系统总线数据吞吐量以及提高设备通信速度。目前服务器

2023-12-20 08:19:38 240

240

什么是时钟信号?数字电路的时钟信号是怎么产生呢? 时钟信号,也称为时钟脉冲,是用于同步数字电路中所有操作的基本信号。它提供了一个参考频率,使得所有电路元件都能按照同样的节奏进行工作。时钟信号

2024-01-25 15:40:52 909

909 芯片为什么要时钟信号 时钟芯片的作用是什么? 时钟信号在芯片中起着非常重要的作用。它是芯片的“心脏”,相当于人体的心脏,用于同步和控制芯片中的各个功能模块之间的操作。时钟信号可以提供一个稳定的时间

2024-01-29 18:11:31 626

626

![]() 、NA、NB等分别与FPGA连接,接口模式为模式。

、NA、NB等分别与FPGA连接,接口模式为模式。 电子发烧友App

电子发烧友App

评论