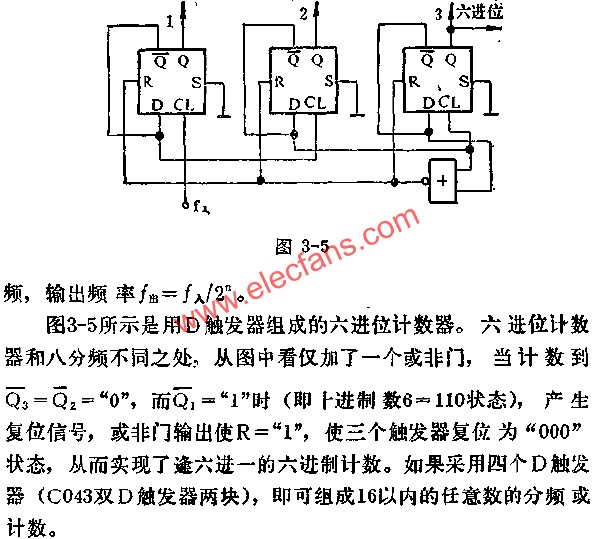

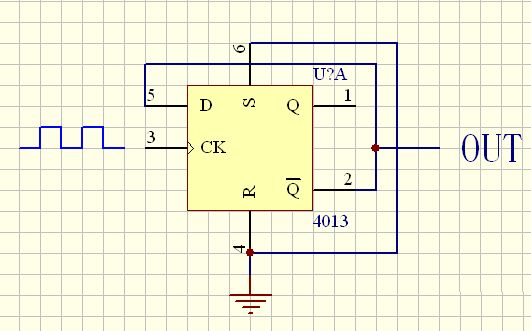

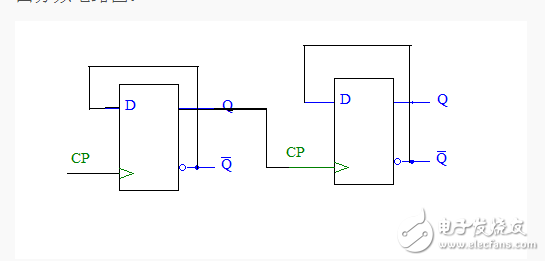

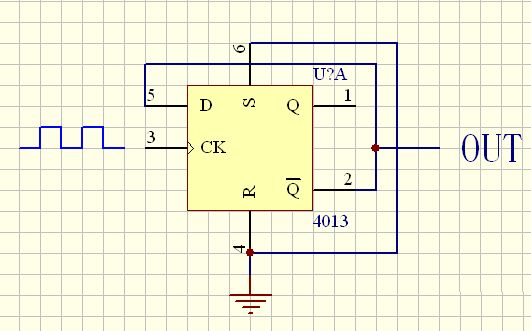

上例图中A将D触发器的D端和Q相连,即可组成二分频电路,如果把三个D触发器串行相连,如图所示,则经过一

2010-09-20 03:40:48 12045

12045

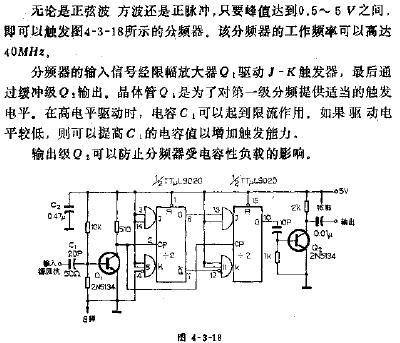

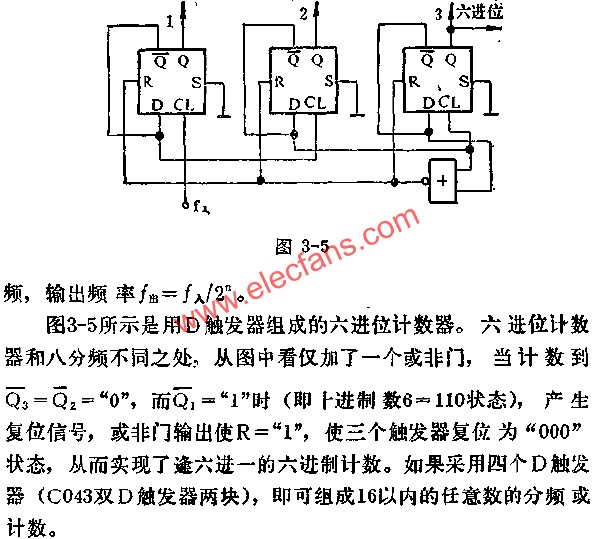

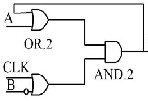

由3 个D 触发器和少量逻辑门构成, 采用了同步工作模式, 其原理是由吞脉冲计数原理产生2 个占空比不同的五分频信号A 和B

2011-11-25 15:16:42 30813

30813

,即0和1,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。 触发器有集成触发器和门电路组成的触发器二种。触发方式有电平触发和边沿触发二种。 触发器应用很广,可用做数字信号的寄存,移位寄存,分频和

2023-01-11 17:17:07 9167

9167

谁能解析一下这个32分频器的具体工作原理?或者有没40103和4013的中文资料?在线等,谢谢!

2017-05-01 17:34:53

51单片机12分频与1分频区别

2023-10-31 06:52:04

如何使用74LS194设计一个16分频器啊求电路图!

2019-11-30 16:23:18

,呵呵。。。上半年,由于Boss项目,学习了FPGA,学的有点急,也断断续续的,才过几个月,似乎知识已经远去,打开电脑,速览以前的资料,记忆又回来了。。。简单记录下这道题,权当回忆。。。//基本D触发器

2012-02-22 13:54:40

初学FPGA对modelsim仿真也不熟悉,仿真几次感觉带时钟的模块老是不对劲,请教一下类似分频,计数的这种模块,testbench该如何写?顺便附上我的一个练习,走过的路过的给个建议,帮助,谢谢

2014-12-01 22:26:41

本帖最后由 gk320830 于 2015-3-7 11:16 编辑

Ti的D触发器SN74LVC2G74,想做一个按键开关机电路,即二分频电路,但是调试过程中老是有问题,请大家帮忙分析分析

2013-10-30 15:44:27

D触发器实现二分频电路(D触发器构成的2分频电路)

2020-03-02 11:05:49

D触发器组成的_2N_1_2分频电路,几种奇数分频电路设计

2012-05-23 19:34:41

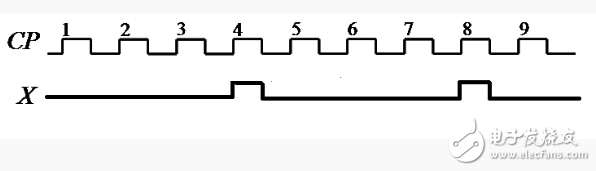

做了一个仿真:key_in作为D触发器的输入,led_out作为触发器输出,时钟周期20ns,key_in每10ns随机变化一次,这样的设置下,key_in信号的变化沿有时会和时钟上升沿重合,根据

2022-01-25 22:41:02

各位朋友,大家好!我刚学习FPGA,选择的是VHDL语言,试着编写了一个二分频和四分频的程序,二分频成功了,但四分频却有问题,代码如下:library ieee;use

2012-11-27 22:03:47

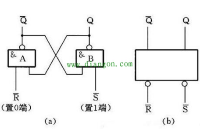

触发器PPT电子教案:触发器是构成时序逻辑电路的基本逻辑部件。? 它有两个稳定的状态:0状态和1状态;? 在不同的输入情况下,它可以被置成0状态或1状态;? 当输入信号消失后,所置成的状态能够保持

2009-09-16 16:06:45

一、实验的目的1、掌握触发器功能的测试方法。2、掌握基本RS触发器的组成及工作原理。3、掌握集成JK触发器和D触发器的逻辑功能及触发方式。4、掌握几种主要触发器之间相互

2009-10-10 11:32:55

触发器实验1)熟悉常用触发器的逻辑功能及测试方法。2)了解触发器逻辑功能的转换。三.实验内容及步骤 (1) 基本RS触发器逻辑功能测试(2) JK触发器逻辑功能测试(3) D触发器逻辑功能的测试

2009-03-20 10:01:05

按逻辑功能不同分为:RS触发器、D触发器、JK触发器、T触发器。按触发方式不同分为:电平触发器、边沿触发器和主从触发器。按电路结构不同分为:基本RS触发器和钟控触发器。按存储数据原理不同分为:静态

2012-06-18 11:42:43

触发器输入电路二极管D的作用是只把负的尖脉冲输入触发器,还可用来组成加速电路。

2009-09-22 08:28:30

、RS触发器、真值表、卡诺图等。但是,这里的很多内容其实已经过时了。此外,对于FPGA的学习来讲,我们只用到了其中很少很少的一部分内容。如果没有数字电路的基础,我们建议就看一部分,知道D触发器

2018-09-20 15:09:45

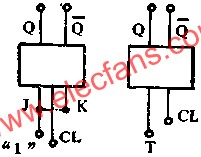

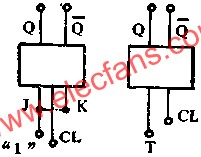

如图, 将j-k触发器用D触发器代替,刚入门 求教

2014-01-09 20:56:31

写了一个定时器0中断程序,知道把单片机12分频改为1分频时,定时器进入中断的时间快12倍,但是不清楚中断服务程序的指令是否也可以快12被。我测了许久都不能有个结论,还请各位大神帮帮忙呀!如果可以快

2015-03-07 16:28:19

jk触发器设计d触发器,根据原理图实现模8加1计数器,来源于西电慕课貌似这个软件只有5.0和5.12两个版本。在win10下拖曳器件会发生残影的现象,而且无法修改连线。虽然有自动连线功能但感觉线连

2021-07-22 08:39:47

求助谁能教设计一个D触发器

2014-12-24 22:54:35

我用门级描述verilog写了d触发器,然后链接了q非端和d断,把输出q连接到一个计数器想做2分频,但是因为没有初始状态,波形都是x。仿真器里可以设置初始状态么?

然后我给d触发器加了一个r端,使

2023-05-10 11:52:10

首先我们要弄明白,什么是二分频器,什么是三分频器?二分频器是由一个高通滤波器和一个低通滤波器组成,而三分频器又有增加了一个带通滤波器,由于滤波器在分频电附近呈现出一种带有一定斜率的衰减特性,在理

2021-01-28 16:58:56

两个非门电路是如何组成一个D触发器的?即可通俗说明下D触发器吗?

2023-05-10 10:32:03

观察输出波形并加以记录。电路有用到:74ls90 pdf .三分频电路d触发器构成2分频电路用多级2进计数器的分频电路脉冲分频电路双稳态分频电路图任意分频电路图1/60分频电路用VHDL语言实现3分频电路SN7474N构成简单的分频电路[此贴子已经被作者于2009-6-22 8:04:20编辑过]

2009-06-22 08:02:10

根据输入信号改变输出状态。把这种在时钟信号触发时才能动作的存储单元电路称为触发器,以区别没有时钟信号控制的锁存器。触发器是一种能够保存1位二进制数的单元电路,是计算机中记忆装置的基本单元,由它可以组成

2019-12-25 17:09:20

何谓四分之一波长的天线?如何去制作四分之一波长的天线?

2021-05-25 07:05:42

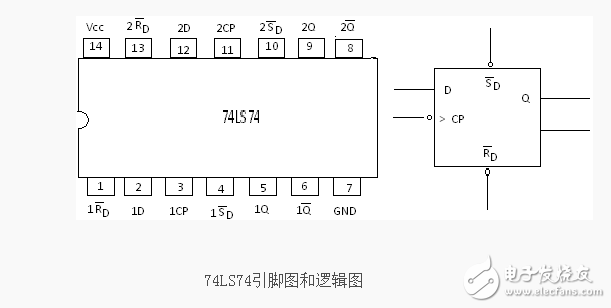

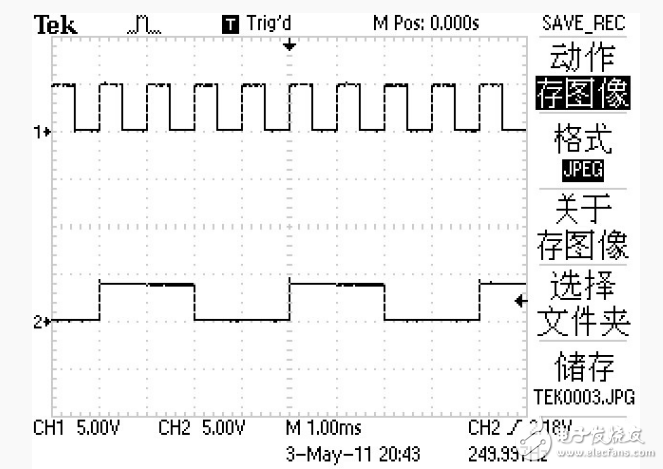

我按照如下图的电路连接实物,74LS74D供电5V,输入信号为1KHZ方波,结果出现下面视频的现象,,想问下有大佬知道怎么回事吗,,试了好几次了,,

2019-06-18 22:33:24

`如图所示,图中第一个触发器D接第二个触发器的非Q端,这个时序图,整不明白啊,我的看法是:当第一个时钟信号高电平来的时候,第一个触发器的输出状态Q是不能判断的啊,因为D接在第二个触发器的非Q端。求大佬指点一下 这个图,是如何工作的?`

2019-01-16 11:50:35

做个单稳态电路、后端做个双稳态电路,按下并松开一次按键实现输出状态翻转一次。现在有个问题:按下去马上松开按键,很正常;但假如按下去的时间比较长,超过单稳态电路中,电容积分复位第一个D触发器的时间,在松开

2014-09-25 16:47:34

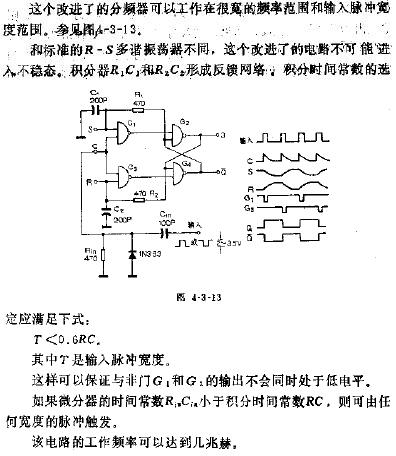

双D型触发器构成的振荡器电路实致上是一个可以灵活控制的波形信号发生器,其结构为图1所示的一个由双D型触发器构成的振荡器。该振荡器的起振、停止可以控制,输出波形的相位和占空比也可以调节,其工作波形如图2所示。图2 波形发生器工作逻辑图

2009-05-25 00:41:49

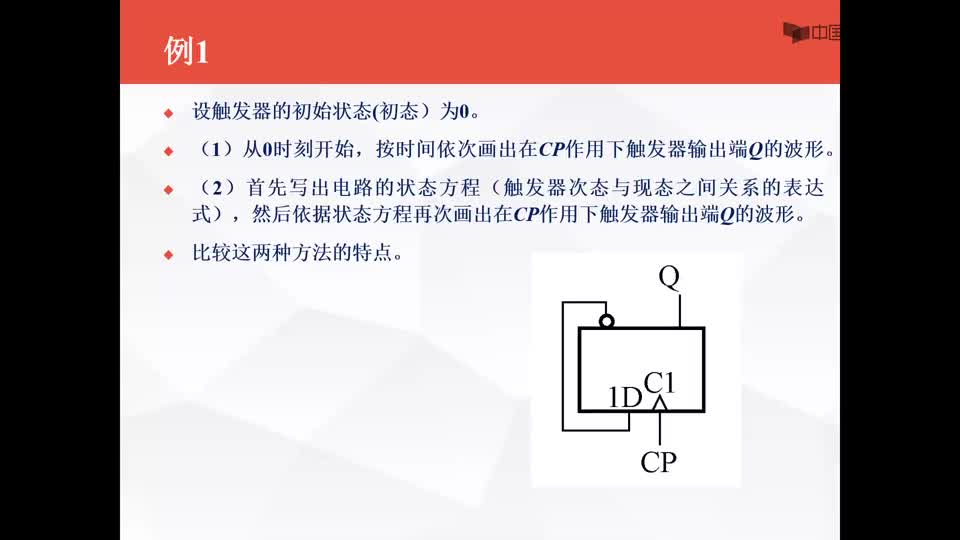

触发器没有使用相同的时钟信号,需要分析哪些触发器时钟有效哪些无效分析步骤和同步时序电路一样,不过要加上时钟信号有关D触发器的例题抄自慕课上的一个题目,注意第二个触发器反相输出端同时连接到复位端JK

2021-09-06 08:20:26

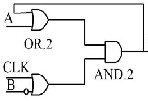

产生“ 2分频”计数器电路,即输出的频率为时钟脉冲。通过在D型触发器周围放置反馈环路,可以构建另一种类型的触发器电路,称为T型触发器,或更常见的是T型双稳态,可用作二分频二进制计数器中的电路如下图所示

2021-02-03 08:00:00

基于PIC的MB506分频电路

2015-08-13 09:26:30

新课第五章 触发器5.1 概述1、触发器具有“记忆”功能,它是构成时序逻辑电路的基本单元。本章首先介绍基本RS触发器的组成原理、特点和逻辑功能。然后引出能够防止“空翻”现象的主从触发器和边沿触发器。同时,较详细地讨论RS触发器、JK触发器、D触发器、T触发器、T'触发器的逻辑功能及其描述方法。

2009-04-02 11:58:41

想要通过1路方波来产生4路相差90°的方波信号,目前单转差已经完成,但是差分再转IQ就不知道用什么方法了。因为频率很低,听说可以用D触发器2分频实现,但是具体要怎么弄呢,感觉只能分频,没法实现

2021-06-24 07:03:25

如何用D触发器实现2分频 原理在线等

2016-07-03 19:37:58

本帖最后由 gk320830 于 2015-3-5 20:47 编辑

如何用JK触发器构成D触发器 电路图来人给个图吧..

2011-11-14 15:21:03

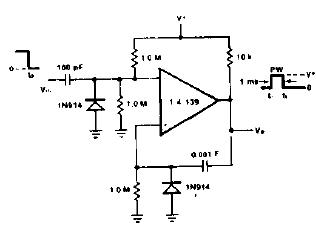

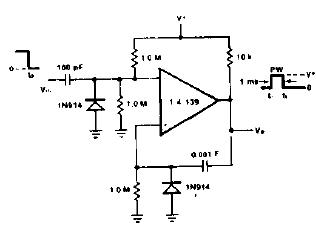

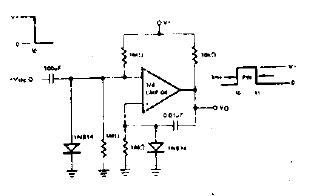

用运放和触发器(分频)设计一个复合信号发生器。设计制作一个方波产生器输出方波,将方波产生器输出的方波四分频后再与三角波同相叠加输出一个 复合信号,再经滤波器后输出一个正弦波信号。设计框图如图 1

2019-03-08 16:40:34

单片机内部有大量寄存器, 寄存器是一种能够存储数据的电路, 由触发器构成。1.触发器触发器是一种具有记忆存储功能的电路, 由门电路组成。 常见的触发器包括: RS 触发器、 D 触发器和 JK触发器

2022-01-20 07:13:51

怎样去设计一种基于门电路的D触发器呢?如何对基于门电路的D触发器进行仿真?

2021-09-14 06:21:42

十分方便。我们转化后怎样判断它们的正确性呢?是根据各触发器的特征方程来验证。 例 1:已知D触发器,试把它转化为JK触发器。D触发器的特征方称为:Qn+1=DJK触发器的特征方称为Qn+1

2018-08-23 10:36:20

、RS触发器、真值表、卡诺图等。但是,这里的很多内容其实已经过时了。此外,对于FPGA的学习来讲,我们只用到了其中很少很少的一部分内容。如果没有数字电路的基础,我们建议就看一部分,知道D触发器

2019-01-17 17:24:19

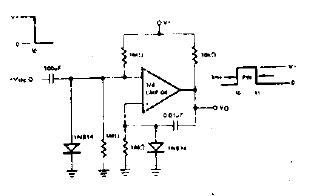

有源二分频电路图:分频点在250MHZ,上图仅为一个声道,另一声道类同。运放IC可选择1个四通道运放TL084,或者选择两个NE5532,JRC4580。

2009-09-17 14:48:44

小弟求一张三分频的电路图,以及指导扬声器信息、算出各配件的方法,不胜感激.....谢谢各位了

2012-08-03 08:50:41

触发器(Flip-Flop,简写为 FF),也叫双稳态门,又称双稳态触发器。是一种可以在两种状态下运行的数字逻辑电路。触发器一直保持它们的状态,直到它们收到输入脉冲,又称为触发。当收到输入脉冲

2019-06-20 04:20:50

源三分频电路设计[hide][/hide]

2009-06-22 10:52:05

用CD4013双D触发器做的脉冲4分频器

2021-05-13 07:25:00

电后,与非门的1脚为低电平,故U1A输出端第3脚为高电平,3脚与与非门的12脚相连,故12脚也为高电平。 2、电路刚上电时,D触发器的RD引脚通过电容C1,电阻R2上电复位,使D触发器的输出Q=D

2023-03-20 15:33:48

D触发器结构的五分频器逻辑电路

2019-09-11 11:29:19

请问一下D触发器怎样实现四分频呢?

2023-05-10 14:34:08

怎样去设计一个基于数字电路的D触发器?如何对基于数字电路的D触发器进行仿真?

2021-09-16 06:45:31

本帖最后由 一只耳朵怪 于 2018-5-24 17:48 编辑

我想用D触发器做一个二分频电路,但是输出信号一直是1V,请问是什么地方出错了?谢谢。

2018-05-24 17:44:03

电平触发的D触发器型号有哪些?大部分都是边沿触发的,现在要用到电平触发器,不知道具体型号没法买到

2019-02-28 14:32:13

集成触发器、集成计数器及译码显示电路实验目的1. 验证基本RS、D、JK触发器的逻辑功能。2. 了解十进制加法计数器和减法计数器的工作过程。3. 了解计数、译码、显示电路的工作状态。实验原理在数字电路

2008-12-11 23:38:01

的分类 触发器呢大体可以按这几个部分分类:1、按晶体管性质分,可以分为BJT集成电路触发器和MOS型集成电路触发器。2、按工作方式分,可分为异步工作方式和同步工作方式,异步工作方式也就是不受时钟控制

2015-04-07 17:47:42

cd4013双d触发器

CD4013双D触发器做的脉冲4分频器应用

-----------------------------. ┌─────

2008-01-09 23:48:45 4808

4808 D触发器

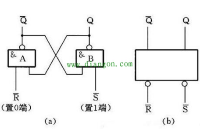

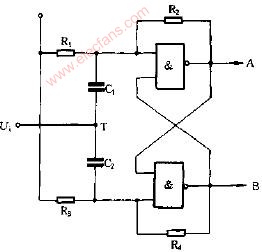

同步式D触发器逻辑电路图

D触发器功能

2008-10-20 09:57:54 2222

2222

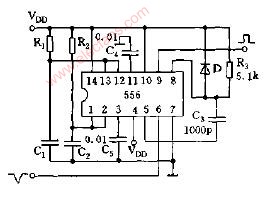

单穏触发器电路图1

2009-04-06 08:39:16 428

428

单穏触发器电路图2

2009-04-06 08:39:38 388

388

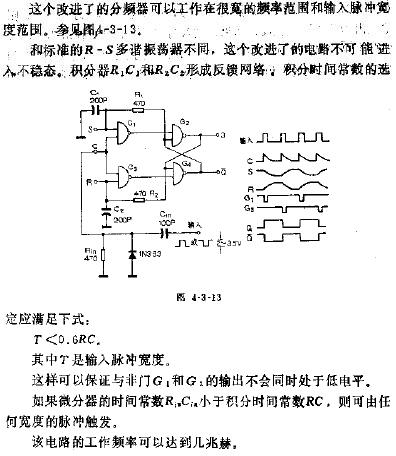

四分频器

2009-04-11 10:26:45 3110

3110

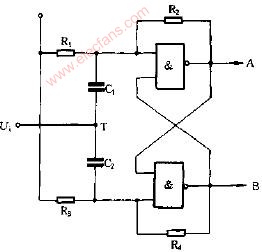

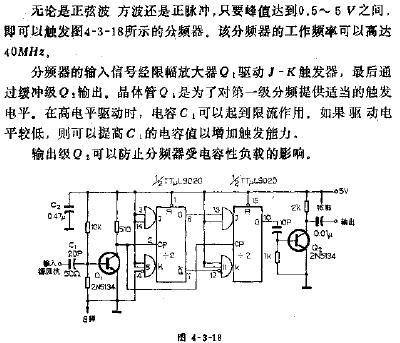

由R-S触发器构成的分频器

2009-04-11 10:28:43 961

961

D触发器电路图

2009-05-08 14:26:44 3680

3680

T触发器电路图

2009-05-08 14:27:49 9589

9589

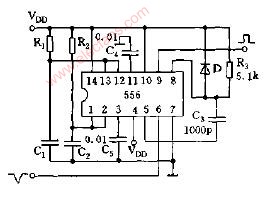

时基触发器电路图

2009-05-18 15:05:38 431

431

D触发器实现二分频电路(D触发器构成的2分频电路)&

2009-06-12 13:58:56 75438

75438

d触发器构成2分频电路

2009-06-22 07:36:33 7782

7782

触发器的分类, 触发器的电路

双稳态器件有两类:一类是触发器,一类是锁存器。锁存器是触发器的原始形式。基本

2010-03-09 09:59:59 1554

1554 图中所示是用CMOS电路D触发器组成T型触发器和J-K触发器线路。图示线路将D触发器的Q端与D端相连,就可组成T

2010-09-20 03:31:35 17220

17220

图中所示是用J-K触发器组成的D触发器电路。

从J-K触发器的逻辑图已知在D触发器端增

2010-09-24 00:21:27 6900

6900

图中所示是J-K触发器组成T触发器的电路和逻辑符号。将J端和K端连接,作为T端,它的功能是当T=“1”,即J,K

2010-09-24 00:26:06 8546

8546

本内容介绍了采用新触发器的高速CMOS 前置分频器 ,欢迎大家下载

2011-07-26 18:05:25 37

37 数字电路--触发器双稳态触发器

2016-12-20 17:32:40 0

0 本文开始介绍了什么是单稳态触发器以及单稳态触发器的电路组成,其次阐述了单稳态触发器特点、门电路构成的单稳态触发器、D触发器构成的单稳态触发器,最后详细的阐述了时基电路构成的单稳态触发器。

2018-03-27 09:24:23 71987

71987

rs触发器电路图与rs触发器内部电路图 rs触发器电路图 主从RS触发器电路图: 主从触发器由两级触发器构成,其中一级接收输入信号,其状态直接由输入信号决定,称为主触发器,还有一级的输入与主触发器

2022-10-19 19:16:03 22366

22366

计算机的时钟节拍、频率分频、数据传输的帧同步等等。计数器可以通过级联多个RS触发器来实现,其中每个触发器的输出作为下一个触发器的输入。 频率分频器 RS触发器可以用于构建频率分频器电路。频率分频器可以将一个输入信号的频率减小为

2023-11-17 16:03:44 751

751 触发器是数字电路中常用的组合逻辑电路,在现代电子系统中有着广泛的应用。其中,最常用的两种触发器是T触发器和JK触发器。本文将详细介绍T触发器和JK触发器的区别和联系。 一、T触发器 T触发器是一种

2024-02-06 14:04:55 419

419

电子发烧友App

电子发烧友App

评论