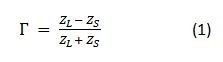

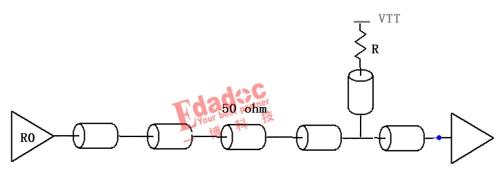

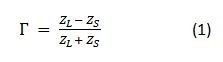

在进行阻抗匹配的时候我们可以在电阻源端放置一个串联端接电阻,但是有时候受到空间的限制可能会把电阻摆的稍微远一点,那么这个时候大家可能会有疑问,电阻离发送端远一点或者电阻放置在接收端,那么电阻还能消除

2023-11-07 07:40:02 742

742

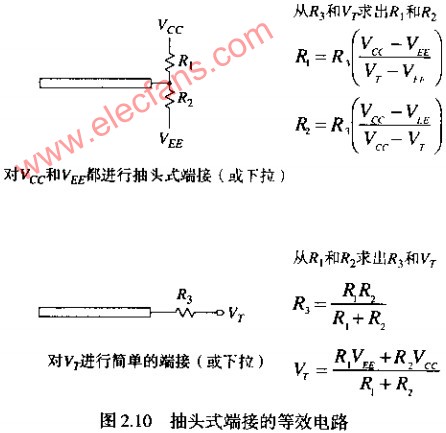

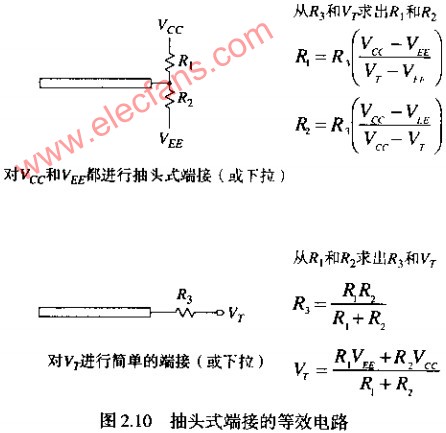

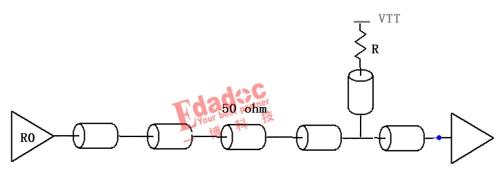

图6为Thevenin端接电路。该电路由上拉电阻R1和下拉电阻R2组成,这样就使逻辑高和逻辑低与目标负载相符。

2020-07-08 11:41:22 4388

4388 过更详细的介绍,当时提到过一个概念叫做“源端端接有效”,根据这个概念,不管是在源端还是在接受端,只要其中任意一端实现阻抗控制,那么就可以避免反射,由此引入今天的主题:端接电阻缓解阻抗突变,抑制反射。

2022-02-16 10:41:49 8238

8238

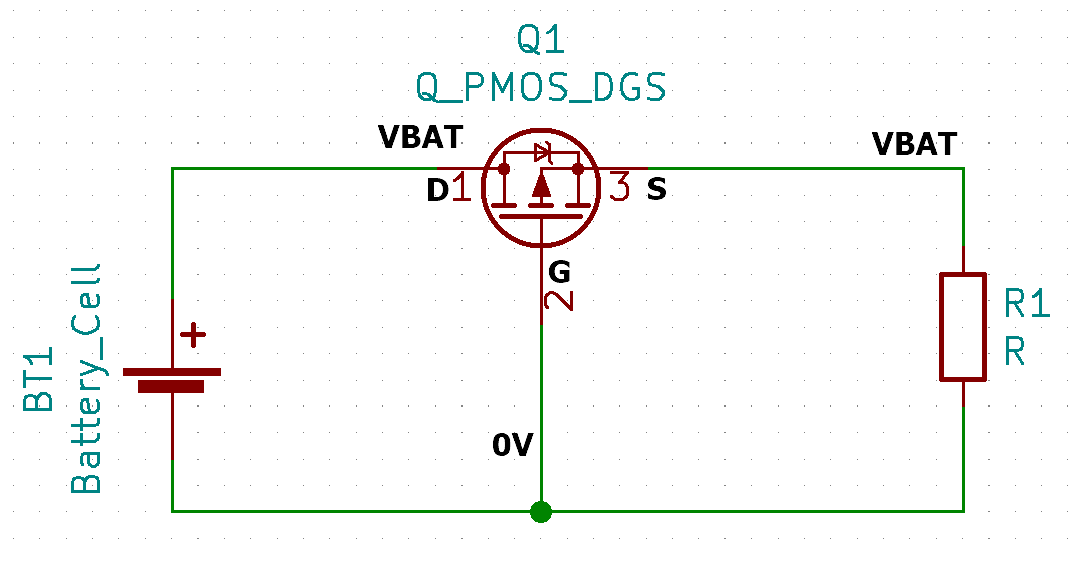

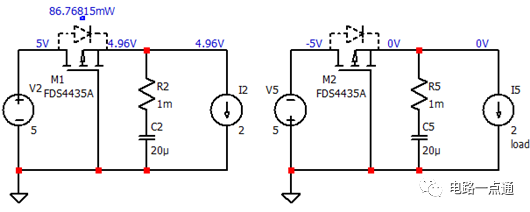

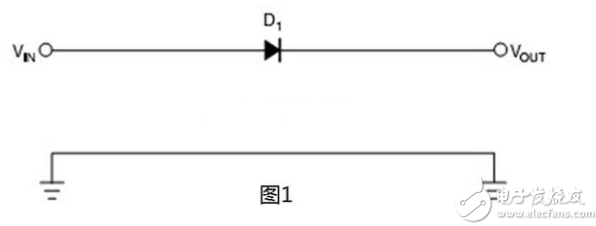

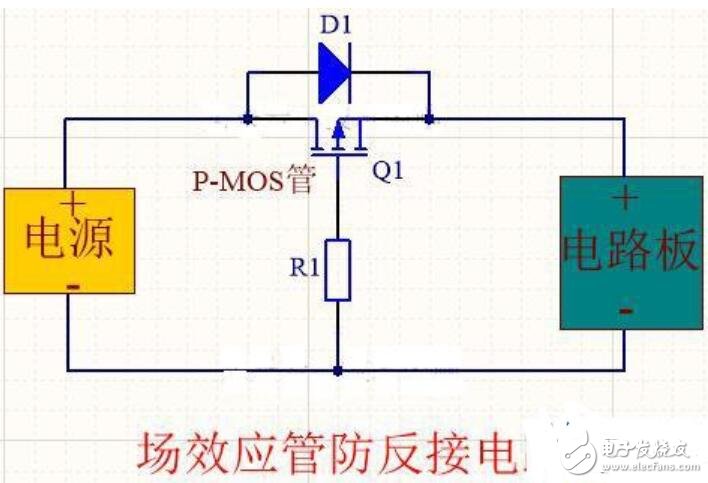

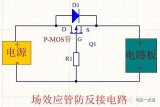

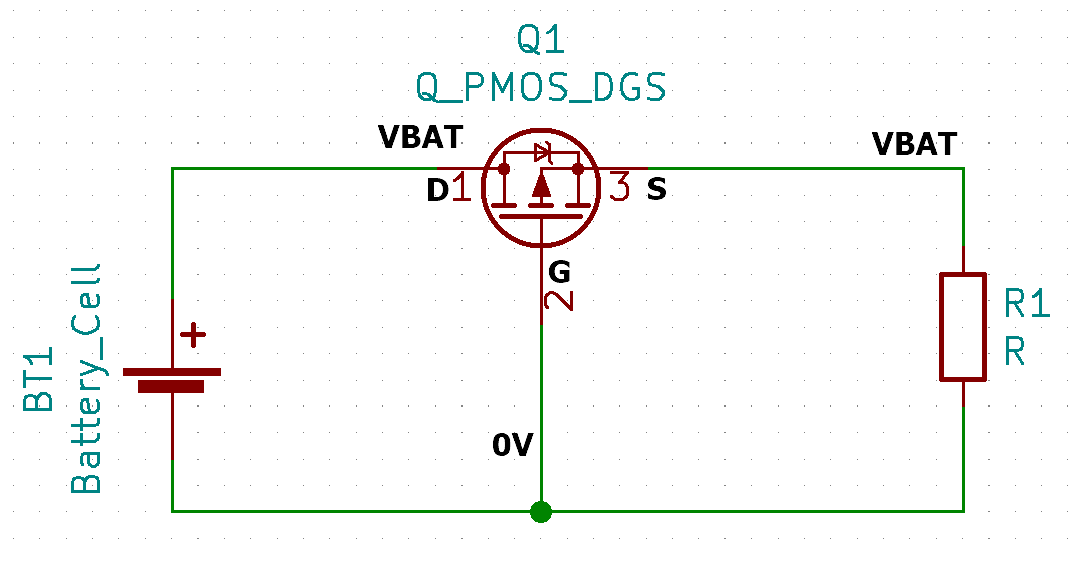

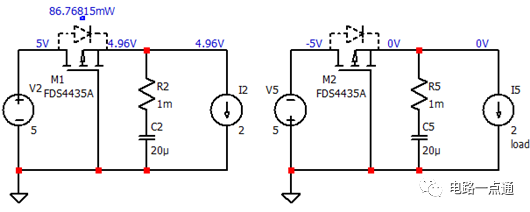

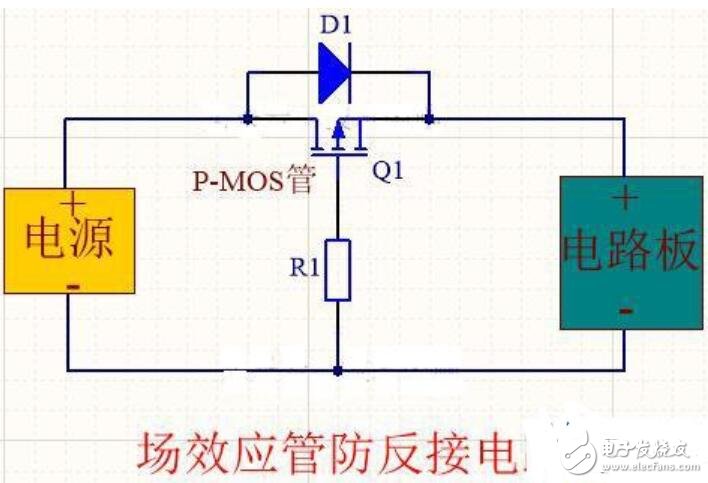

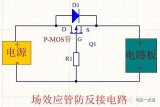

在接电源到板子的时候,如果一个疏忽接反了,极有可能烧毁芯片或器件,所以需要设计防反接的电路。本文就介绍如何用MOS管来实现电源防反接电路。

2023-03-22 15:20:06 2163

2163

电路小课堂,防反接电路哪里跑 ...... by 矜辰所致

2023-05-12 18:38:23 3464

3464

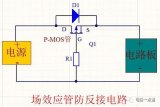

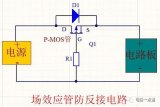

场效应管防反接电路其功能和二极管防反接电路一样,其目的都是防止电源的正负输入端接反而导致负载电路烧毁等意外情况发生。场效应管防反接电路相比二极管防反接电路最大的优势是几乎零压降,二极管的压降一般

2023-06-10 09:30:48 674

674

rS-485 网络的许多信号完整性和通信问题都源于端接,这可能是因为缺少端接或端接不正确。在 RS-485基础知识系列的这一部分,我将讨论何时不需要端接 RS-485 网络,以及在需要端接时如何使用标准(并联)端接和交流电 (AC) 端接网络。

2023-07-04 11:38:55 1270

1270

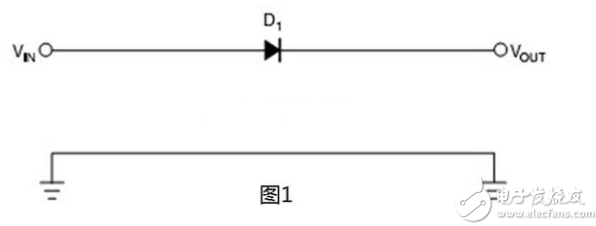

今天给大家介绍两个防反接电路,此电路用到的元件非常的少。

2023-07-10 09:59:25 1157

1157

基本的PMOS防反接电路,利用PMOS的寄生二极管。

2023-09-04 09:20:26 968

968

今天一如既往的给大家分享干货,之前写了二极管防电源反接电路,今天分享MOS管防电源反接电路。

2023-09-06 10:11:39 1708

1708

16位收发器,带30个Ω端接电阻;3 态

2023-03-24 14:58:14

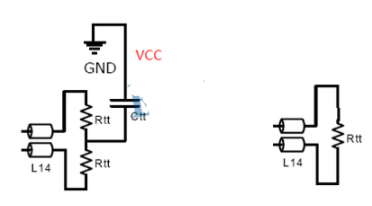

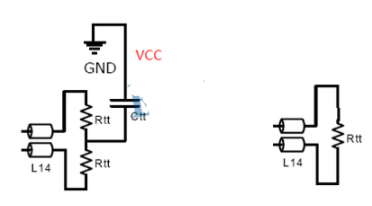

如图,上端接电源,下端接地,f1_1是输出,想问下,这个电路里各个电阻电容的作用

2015-12-22 15:10:32

高电平时的驱动电流以保证通过端接电阻的高电平电压满足门限电压要求。在输出为高电平状态时,这种并行端接电路最大的缺点是消耗的电流过大,如果电源是 5v,驱动电流可能达到 50-100ma,这是普通驱动器无法

2020-03-19 07:00:00

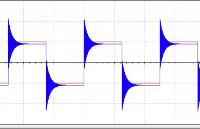

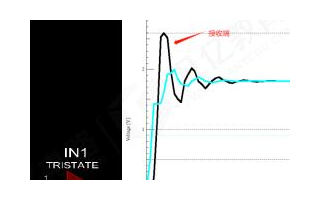

,串联端接比较好地消除了反射带来的过冲及振铃,但由于接收器内部呈现容性阻抗,出现了信号上升、下降沿退化。其他几种方案在此电路中的效果相当,都不能很好地解决问题。但是,也有微小的差别,并联上拉将逻辑

2018-11-27 10:50:39

高速先生成员--姜杰

端接可以解决很多反射问题,如果还有问题,有没有一种可能是端接电阻阻值没选对?

对于点到点的拓扑,末端并联电阻的阻值比较容易选择,端接电阻阻值R与传输线特征阻抗一样即可

2024-03-04 15:49:14

你好,

请问DACAD9780是否需要在电路板上加端接电阻? datasheet上说明Input Differential Input Impedance 为80~120 欧姆, 是不是就不用在板子上加100欧姆电阻?

谢谢!

2023-12-15 08:04:31

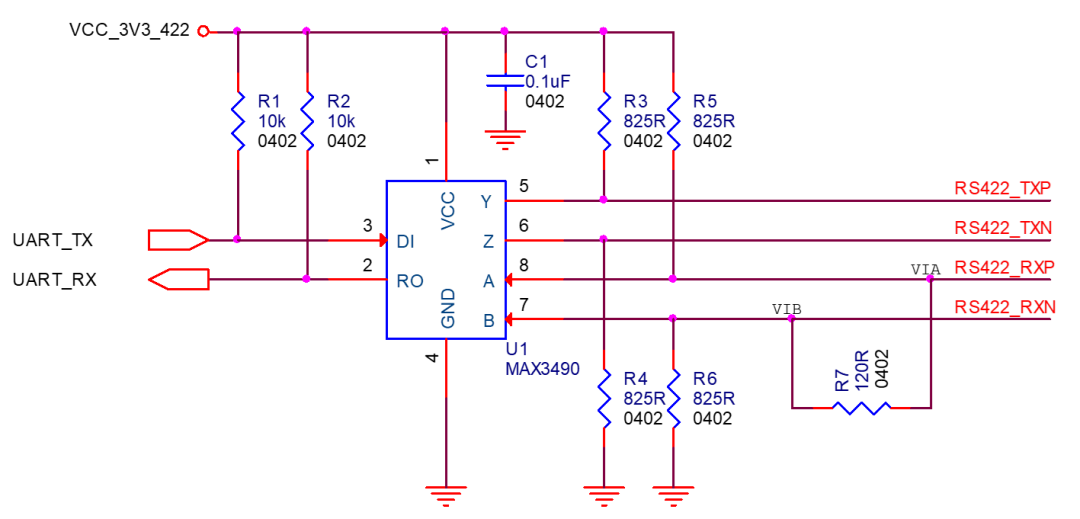

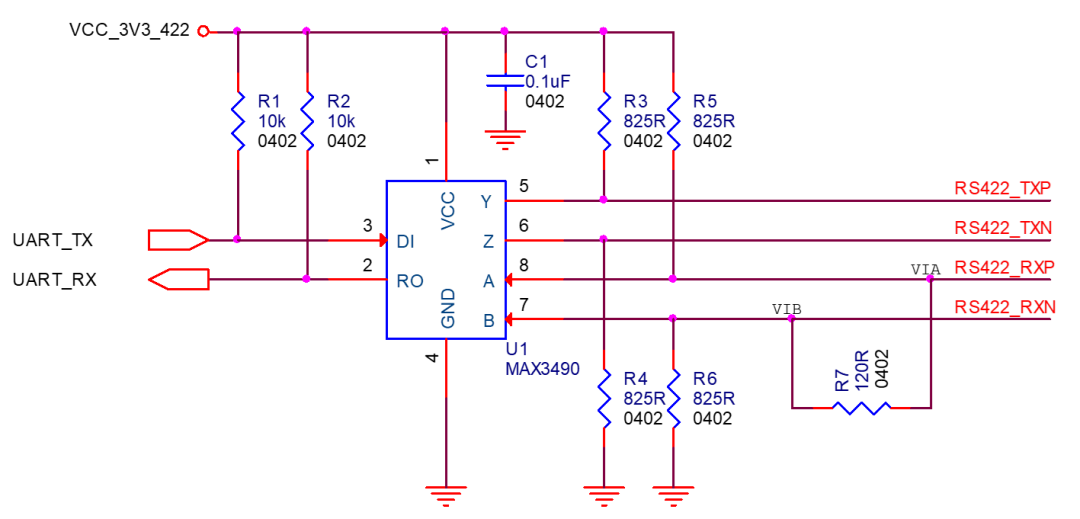

产中,我们的设备工作时在每个极端始终具有120R端接电阻,但在隔离条件下,单个设备应该在不需要端接电阻的情况下进行通信。以下是我们的485接口的电路图。

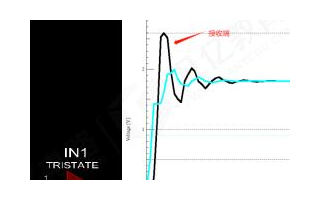

下面的第一张图是在没有端接时的A-B信号示波器

2024-01-03 08:50:57

行之有效,缺陷是会耗费直流电输出功率。上拉的情况下能提升驱动器工作能力,下拉的情况下能提升对电流量的吸收力。 戴维宁端接 戴维宁端接就是说选用上拉电阻和下拉电阻来相互构成端接电路,促使戴维宁等效电路

2020-07-01 14:29:50

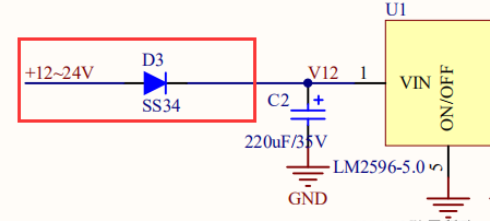

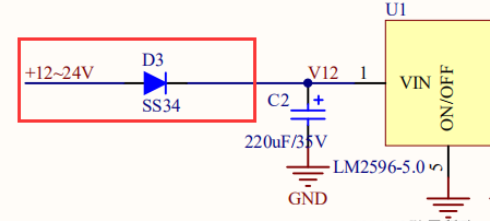

电路1、在直流电源和地之间并接电容的电容可称为滤波电容.滤波电容滤除电源的杂波和交流成分,压平滑脉动直流电,储存电能.取值一般100-4700uF.取值与负载电流和对电源的纯净度有关,容量越大越好

2021-12-28 07:29:11

原因:实际应用时,容性负载超过dcdc模块正常使用时的最大容性负载,输出电容过大,开机瞬间需要很大的启动电流,会引起模块的启动不良。解答:建议减小输出端所接电容或是在输出端加缓冲电路以提高模块带容性负载的能力。

2018-07-19 14:07:41

`原因:实际应用时,容性负载超过模块正常使用时的最大容性负载,输出电容过大,开机瞬间需要很大的启动电流,会引起模块的启动不良。解答:建议减小输出端所接电容或是在输出端加缓冲电路以提高模块带容性负载的能力。`

2018-06-26 15:05:10

`pcb威廉希尔官方网站

:电源与地之间接电容的原因`

2012-08-20 13:52:07

`本章节主要讲解内容:1.末端端接与串联端接的比较2.选择合适的端接电阻3.端接器件之间的串扰`

2021-04-02 11:08:45

`作者:黄刚对于做过DDR模块的PCB工程师来说有没有过这样的体验,在板子小密度高的情况下,要是突然发现原理图上没有那一大把地址信号的端接电阻,他们的心情一定会是这样的…掐指一算,基本上一个DDR

2020-09-10 14:48:25

电路设计中为什么电源和地之间要接电容?

2021-11-11 09:22:15

电源与地之间接电容的原因分析1、电源与地之间接电容的原因有两个作用,储能和旁路储能:电路的耗电有时候大,有时候小,当耗电突然增大的时候如果没有电容,电源电压会被拉低,产生噪声,振铃,严重会导致CPU

2021-12-27 06:34:00

拓扑为一拖四、fly-by。在处理差分时钟的时候,雷工在原理图上看到的除了端接电阻,还有一个并联在差分信号P/N中间的电容。 如果这个电容早两天出现,雷工估计还要纠结放在链路的哪个位置,可是,对于认真

2020-06-12 14:55:42

一、对于电子电路:电阻的两端并联一个电容,为了减小对高频信号的阻抗,相当于微分,这样信号上升速度加快,用于提高响应速度;电容一端接电阻,一端接地,则相反,滤去高频,相当于积分,用于滤波。

2019-05-23 07:26:41

的QX40/41/42等输入模块均属于漏型输入模块。源型输入电路源型输入电路的电流是从PLC的输入端流进,而从公共端流出,即公共端接外接电源的负极。 如果所有输入回路的二极管的阴极相连,就构成了共

2012-04-24 14:02:23

容差模拟电路的软故障诊断的小波方法基于小波和量子神经网络的故障诊断原理

2021-04-12 06:40:08

的输出阻抗,可在ECL电路的接收端使用下拉端接电阻来吸收能量。 · 串联端接用点对点的布线拓扑是最佳的,此外,串联端接对那些相对于时钟频率为小尺寸的网络走线很适合。 · 对于短的传输线,当最小

2018-11-27 15:20:36

DN281- 宽输入范围,高效率DDR端接电源实现快速瞬态响应

2019-06-18 13:37:26

1.LT1764数据手册中电特性参数表格里的NOTE3:将LT1764-adj的ADJ与OUT相连,请问ADJ与GND之间是否需要接电阻?

2.当给LT1764-ADJ的输入电压在16V-20V之间

2024-01-03 10:34:47

AM26C31差分信号的输出,需要在差分信号之间接电容吗?

2018-04-18 09:08:42

开关电源高压地与低压地之间为什么要接电容呢?

2023-04-20 15:08:00

都从信号接收端接出来,总会在端接电阻分支点和接收端之间存在一段长度的走线,如下图链路模型。这段桩线的长度Lstub会影响信号接收质量,若桩线过长将削弱端接效果。下图显示的是接收端前面桩线长度分别为Tr、Tr

2023-02-27 17:31:13

數位電容表电路此處介紹的電容表優點為簡單,使用的零件數又少。再者,此電容表的準確度相當好,因此可當成實驗室的儀器使用。電路的工作原理為計數一段時間內(由一組低頻振盪器決定計數時間長度)固定振盪電路所

2010-10-06 11:04:06

火线零线之间串接电阻有什么作用

2019-03-18 22:12:53

电力线接收端接口电路图4中的二极管D1、D2起限幅作用,用来保护后续电路。?

2008-10-13 13:55:48

大神们,请教个问题;本人电路设计刚入门我有一款芯片,如下图所示,我想问FREFin管脚是参考输入信号,为什么需要接电容电阻?如果接,那么阻值容值怎么确定大小?

2017-11-01 10:39:30

的影响后,下面我们就来看看在DDR的Fly_By设计链路中容性负载对链路阻抗的影响。如下是常见的DDR一拖五的Fly_By拓扑的设计方案,链路中一个主控拖五个负载颗粒,端接电阻放在最后一个颗粒后面。

我们

2023-05-16 17:57:26

。· LVPECL优势:交流耦合允许调整偏置电压。避免电路两端之间的能量流动。弱点:交流耦合只推荐用于平衡信号(50%占空比的时钟信号)。备注:交流耦合电容的ESR值和容值应该很低。电阻桥· CMOS优势

2019-09-27 07:30:00

你好, 请问DACAD9780是否需要在电路板上加端接电阻? datasheet上说明Input Differential Input Impedance 为80~120 欧姆, 是不是就不用在板子上加100欧姆电阻? 谢谢!

2018-08-24 11:18:49

。(3)戴维宁端接戴维宁端接就是采用上拉电阻和下拉电阻来共同组成端接电路,使得戴维宁等效阻抗等于传输线的特征阻抗以实现阻抗匹配。戴维宁端接的优点是上拉电阻和下拉电阻都能用来吸收反射,在电路上没有信号

2020-03-16 11:29:10

我想问一下电路为什么需要端接呢?常见的端接方式又要哪些呢?

2021-03-06 07:00:29

先说说电路为什么需要端接?众所周知,电路中如果阻抗不连续,就会造成信号的反射,引起上冲下冲,振铃等信号失真,严重影响信号质量。所以在进行电路设计的时候阻抗匹配是很重要的考虑因素。我们的PCB走线进行

2019-05-17 08:04:22

15~75Ω,较多的选择为33Ω。 串联端接的优点在于; · 每条线只需要一个端接电阻,无须直流电源相连接,因此不消耗过多的电能; · 当驱动高容性负载时可提供限流作用,这种限流作用可以帮助减小

2018-11-27 15:22:15

固态继电器典型应用电路

1.基本电路(1)基本连接电路固态继电器的基本连接电路如图7-36 所示。其中图7-36 (a) 所示为一般应用电路,在输入端接控制信号,

2010-03-29 14:16:26 223

223

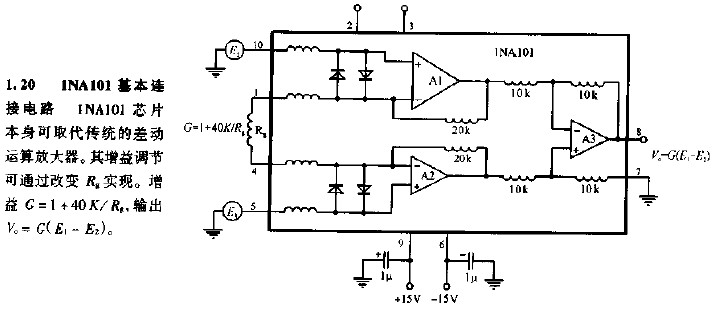

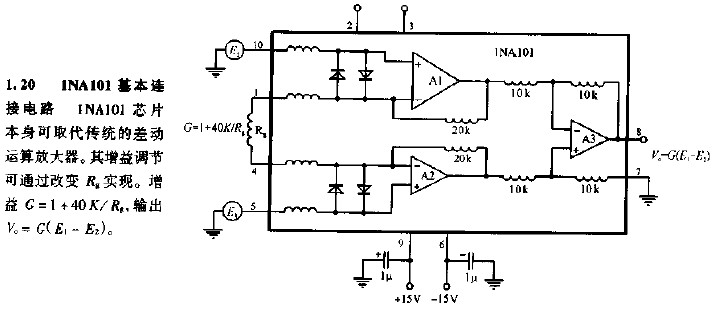

INA101基本连接电路

2009-04-19 11:50:47 1774

1774

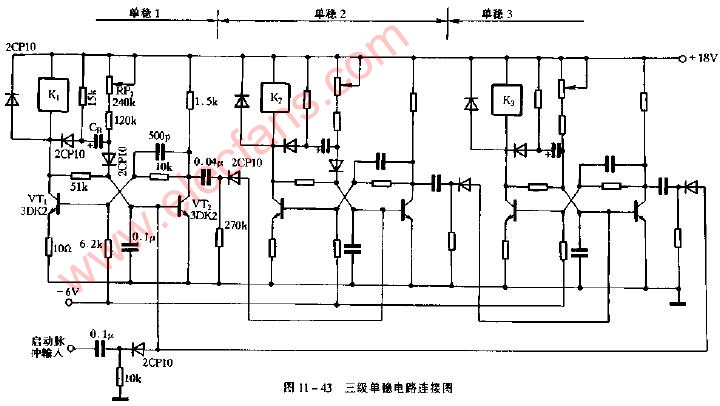

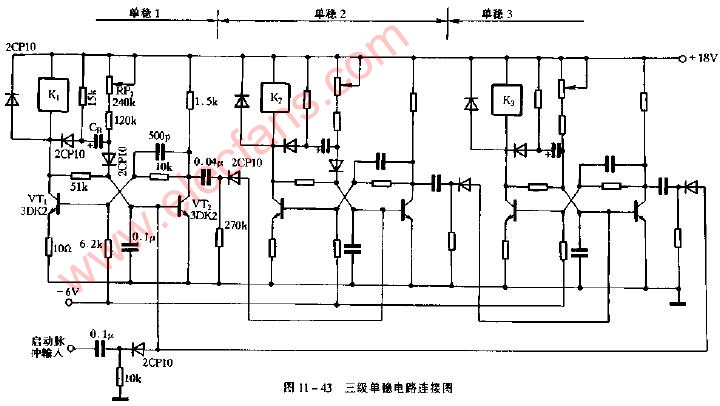

三级单穏电路连接电路图

2009-05-08 14:07:44 744

744

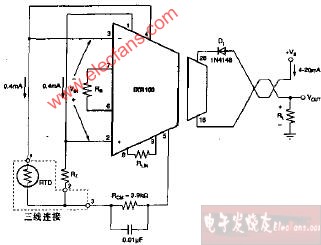

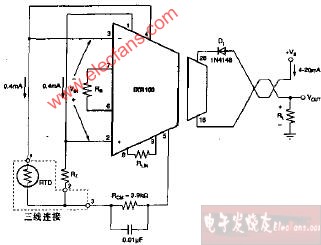

RTD三线基本连接电路图(二)

2009-06-22 10:46:04 4655

4655

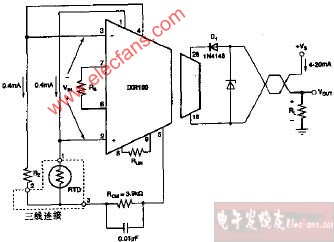

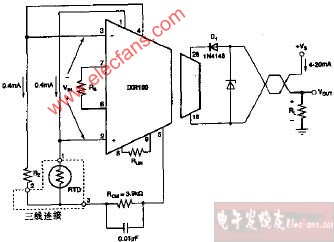

RTD三线基本连接电路图(一)

2009-06-22 10:46:31 7809

7809

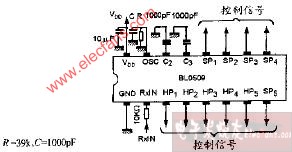

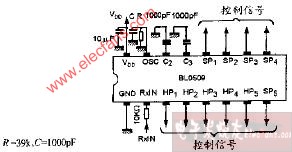

BLO509型应用连接电路图

2009-07-02 10:57:47 538

538

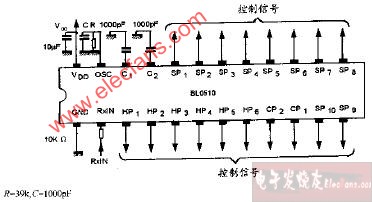

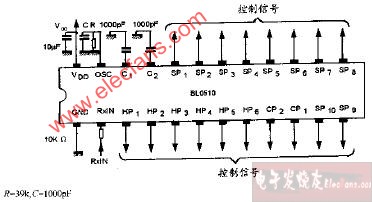

BLO510型应用连接电路图

2009-07-02 10:58:09 644

644

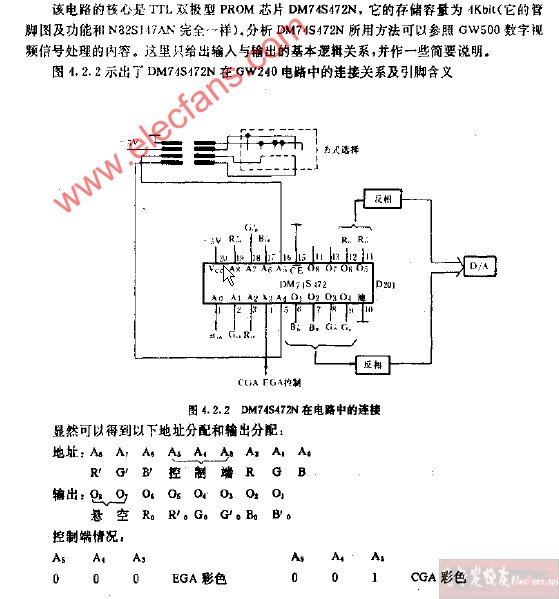

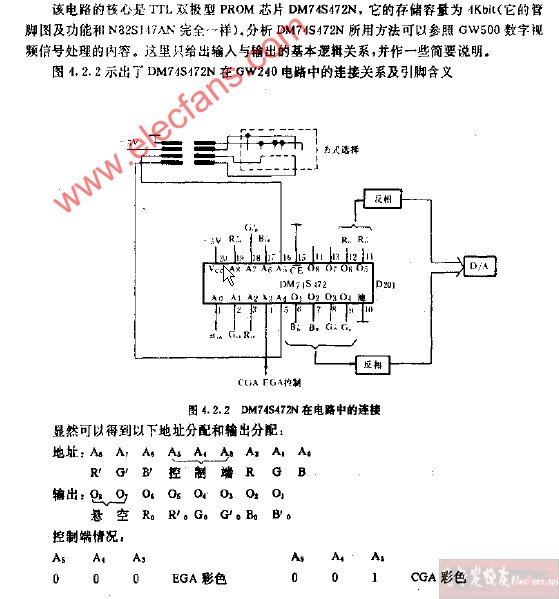

DM74S472N在电路指那个的连接电路图

2009-07-15 11:27:37 866

866

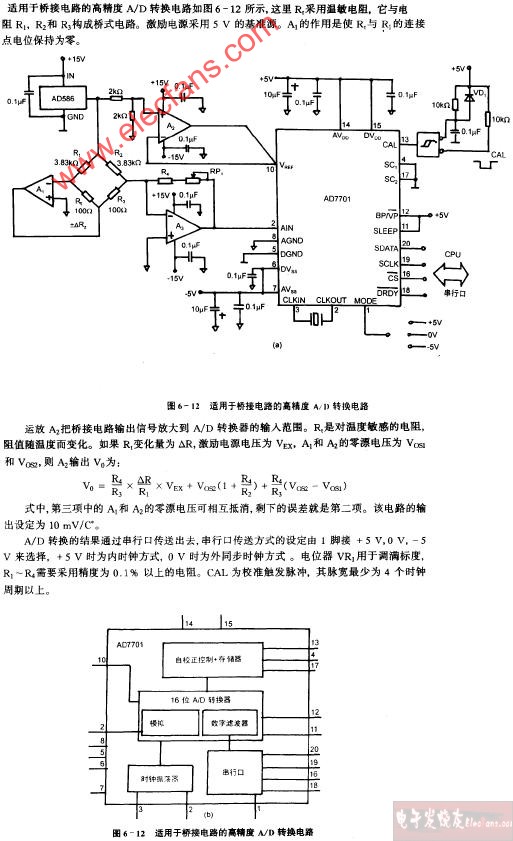

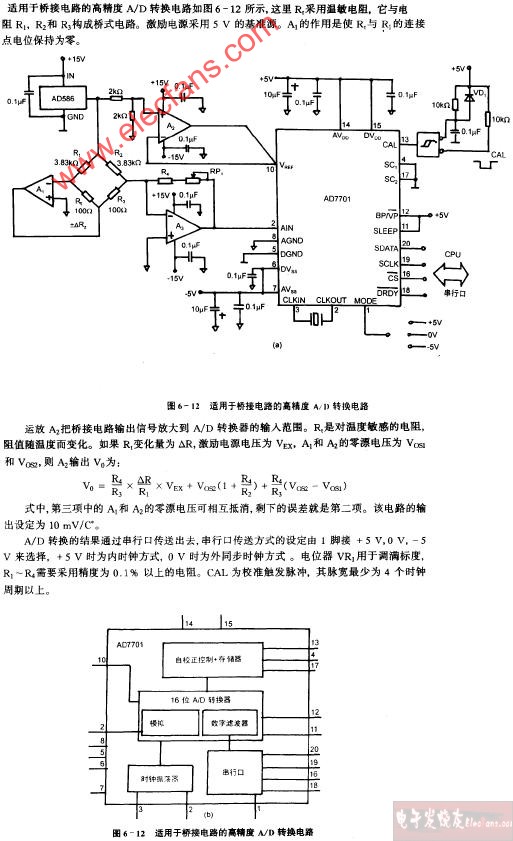

适用于桥接电路的高精度AD转换电路图

2009-07-15 16:30:58 595

595

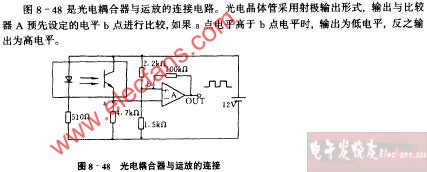

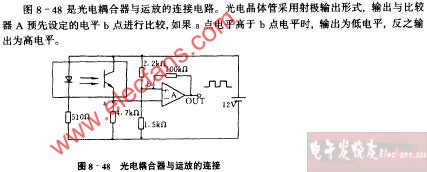

光电耦合器与运放的连接电路图

2009-07-16 17:36:56 1226

1226

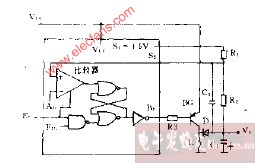

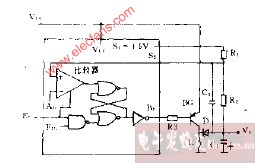

逆变器V3框图及外接电路图

2009-07-20 14:57:14 780

780

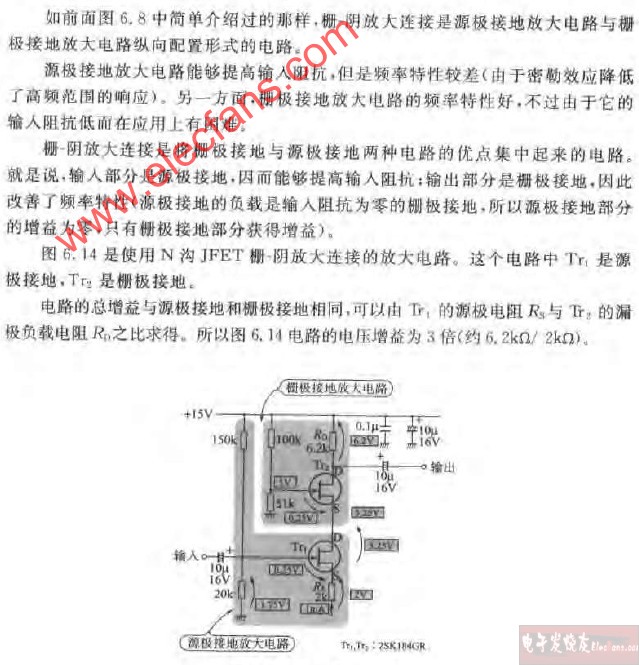

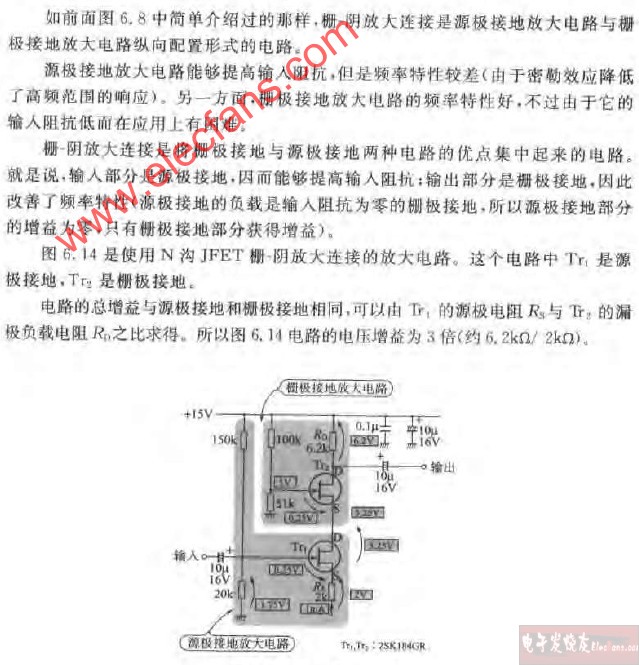

栅-阴放大连接电路图

2009-08-13 15:56:14 620

620

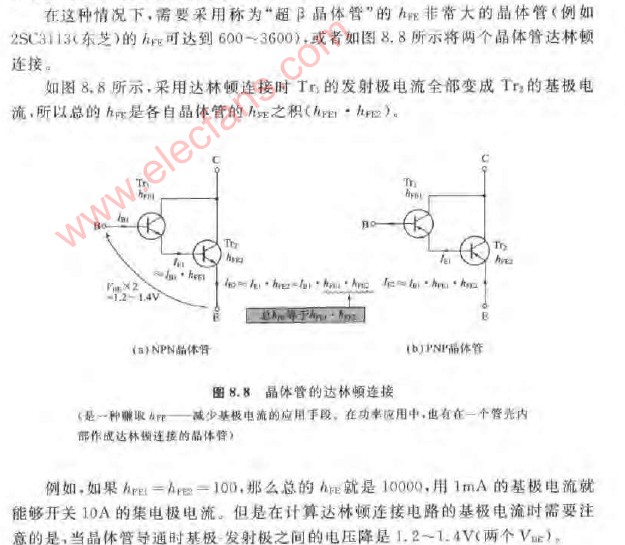

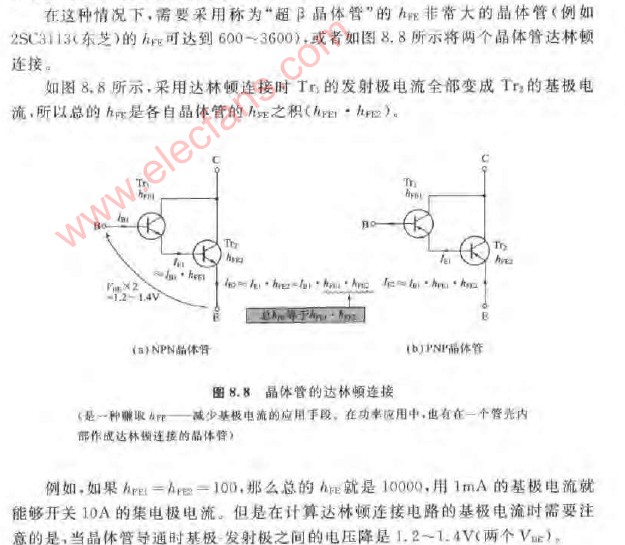

晶体管的达林顿链接电路图

2009-08-15 17:24:09 3008

3008

可为一端接地负载提供恒流的电源电路

电路的功能

电流源是为阻

2010-05-17 11:41:08 2235

2235

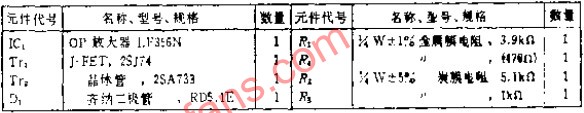

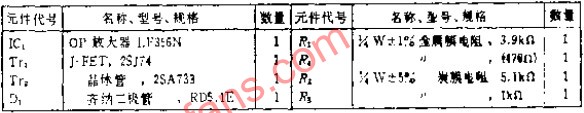

有时ECL电路采用图2.10所示的抽头示端接方式进行端接。根据所期望的总的阻抗和终端电压来计算抽头式端接的有交电阻值公式为:

2010-06-01 15:49:50 585

585

图6.16中,相邻的端接电路会在电路走线之间交叉耦合信号能量。这种交叉耦合比通常发生在相邻传输线之间的

2010-06-11 16:59:09 1489

1489

PT100连接电路

2011-06-07 16:45:28 7152

7152

通过端接电路在抑制攻击线上反射的同时,减小了受害线上信号的串扰,从而使信号在两条耦合线上的传输质量得到改善。最后进行了多组数据的串扰比较研究,分析了串扰减小的原因。

2011-12-12 14:31:21 28

28 连接电路是一个学电子的必经之路,对于新手感觉很难上手,不知从何下手,连接电路很是困难,很多信号、接口、电源、接地都模糊不清。电路图连接电路,有什么技巧呢?下面我们一起来讲一讲,完全干货,值得收藏噢!

2018-11-16 16:31:48 20152

20152 电子设备都须用到直流电源,接入电源最怕的就是正负极接反了。若没有防反接电路,那就不知会发生什么情况了, 元件损坏那是肯定的了。所以一般电路都会加反接电路,如下介绍几种常用电路。 1、利用一个二极管

2019-01-31 15:00:40 2320

2320

在没有防反接电路的设计中,如果用户接反电源正、负极,可能会发生意外事故或者烧坏电子产品。为了防止这些意外发生,提高产品的可靠性,我们可以设计一个防反接的电路。我们可以用二极管设计防反接,也可以用

2019-11-24 09:58:00 20959

20959

末端并联端接也用的比较多,如前文提到的T点及Fly_by拓扑,其中上拉比较常见,端接电阻通常和传输线阻抗一致。

2021-04-11 09:56:07 2248

2248

对于做过DDR模块的PCB工程师来说有没有过这样的体验,在板子小密度高的情况下,要是突然发现原理图上没有那一大把地址信号的端接电阻,他们的心情一定会是这样的…

2020-12-24 15:29:14 448

448 电路设计中为什么电源和地之间要接电容?https://blog.csdn.net/qq_41694204/article/details/81557660

2021-11-06 13:36:00 3

3 电源与地之间接电容的原因分析1、电源与地之间接电容的原因有两个作用,储能和旁路储能:电路的耗电有时候大,有时候小,当耗电突然增大的时候如果没有电容,电源电压会被拉低,产生噪声,振铃,严重会导致CPU

2022-01-05 14:32:38 4

4 电路1、在直流电源和地之间并接电容的电容可称为滤波电容.滤波电容滤除电源的杂波和交流成分,压平滑脉动直流电,储存电能.取值一般100-4700uF.取值与负载电流和对电源的纯净度有关,容量越大越好

2022-01-05 15:11:08 9

9 高速电路信号完整性分析与设计—端接与拓扑

2022-02-10 16:38:28 0

0 Raychem瑞侃为印刷电路板(PCB)终端提供普遍的公、管脚和母端子。Raychem瑞侃可以为PCB端接电线或模块提供各种经济高效且安全可靠的解决方案。此外,使用相应的Raychem瑞侃实用工具

2022-06-22 11:26:04 1213

1213 本章的主要内容 末端端接与串联端接的比较 选择合适的端接电阻 端接器件之间的串扰

2022-09-20 14:42:29 1

1 以下应用笔记描述了高速模数转换器(ADC)之前信号调理电路中常用的变压器的初级侧和次级端接之间的差异。本文详细介绍了这两种端接方案对专为高中频应用设计的ADC的增益平坦度和动态性能的影响。

2023-01-13 14:49:03 538

538

早期的PECL端接电路提供了400mA的输出电流能力,足以端接大约14对PECL输出。该电路已代表需要400mA以上电流的设计人员进行了重新审视。增加单个电阻可将可用输出电流增加 300%,增加一个晶体管可将输出能力提升至 4A。

2023-01-13 15:03:17 480

480

本设计笔记展示了 DDR 存储器端接电源如何供应和吸收 6A 电流,同时保持 1.8V 或 2.5V 电源的稳压基准电压。该电路为 DDR 同步 DRAM (SDRAM) IC 提供终止电压。具有MAX1637降压控制器。

2023-01-14 14:31:32 1980

1980

末端并联端接的电阻最好放在接收器之后,走线先连接到接收器,然后拉出一条“尾巴”,端接电阻放在“尾巴”后面,如图所示。

2023-03-22 16:16:29 526

526

场效应管防反接电路其功能和二极管防反接电路一样,其目的都是防止电源的正负输入端接反而导致负载电路烧毁等意外情况发生。场效应管防反接电路相比二极管防反接电路最大的优势是几乎零压降,二极管的压降一般

2023-05-28 11:04:24 1248

1248

四种防反接电路汇总

2023-05-29 09:56:43 622

622

本文将分析由于RS422/485电路偏置电阻取值错误而导致的通信异常,然后通过增大端接电阻来解决问题,这不是正确的电路设计。

2023-07-13 11:44:03 1956

1956

变频器三相输入端接电动机,三相输出端接三相电源线会出现什么影响? 在工业设备中,交流电机是最常见的负载,而变频器是用来控制电机的速度和转矩的重要电子设备。在这个过程中,如果三相输入端接电动机,三相

2023-10-22 11:33:59 1224

1224 为什么电路端接电阻能改善信号完整性? 在电路设计中,信号完整性是一个极其重要的概念。信号完整性是指信号在传输、转换和处理过程中所遭受的失真、干扰或损失。这些信号可能是模拟信号或数字信号,它们的完整性

2023-10-24 10:04:52 372

372 电子发烧友网站提供《为什么要在电源与地之间接电容?.doc》资料免费下载

2023-11-14 11:39:36 2

2 电子发烧友网站提供《端接电阻基础知识.doc》资料免费下载

2023-11-21 09:31:02 0

0 。它有一个特定的阻抗,通常以欧姆表示,表示为电阻和电抗的复数组合。传输线的负载阻抗与传输线的特性阻抗之间的不匹配会导致反射,并且会产生信号衰减和系统性能下降。 在阻抗匹配时,串联端接电阻靠近发送端,可以减少传输线

2023-11-22 18:26:12 860

860 信号线上串接电阻的作用及其对整个电路的影响 在电子电路设计中,信号线上串接电阻是一种常见的电路调节元件。它能够对电路的传输特性、噪声抑制和电流变化等方面产生影响。本文将详细探讨信号线上串接电阻的作用

2023-12-21 13:59:37 763

763 CMOS是一种常见的逻辑门电路,它使用CMOS威廉希尔官方网站

来实现数字逻辑功能。在CMOS电路中,输入端接电阻后接地的情况下,一般情况下是低电平。 首先,让我们先了解一下CMOS电路的基本原理。CMOS(互补

2024-01-09 11:25:51 672

672 端接可以解决很多反射问题,如果还有问题,有没有一种可能是端接电阻阻值没选对?

2024-03-04 15:44:22 125

125

电子发烧友App

电子发烧友App

评论